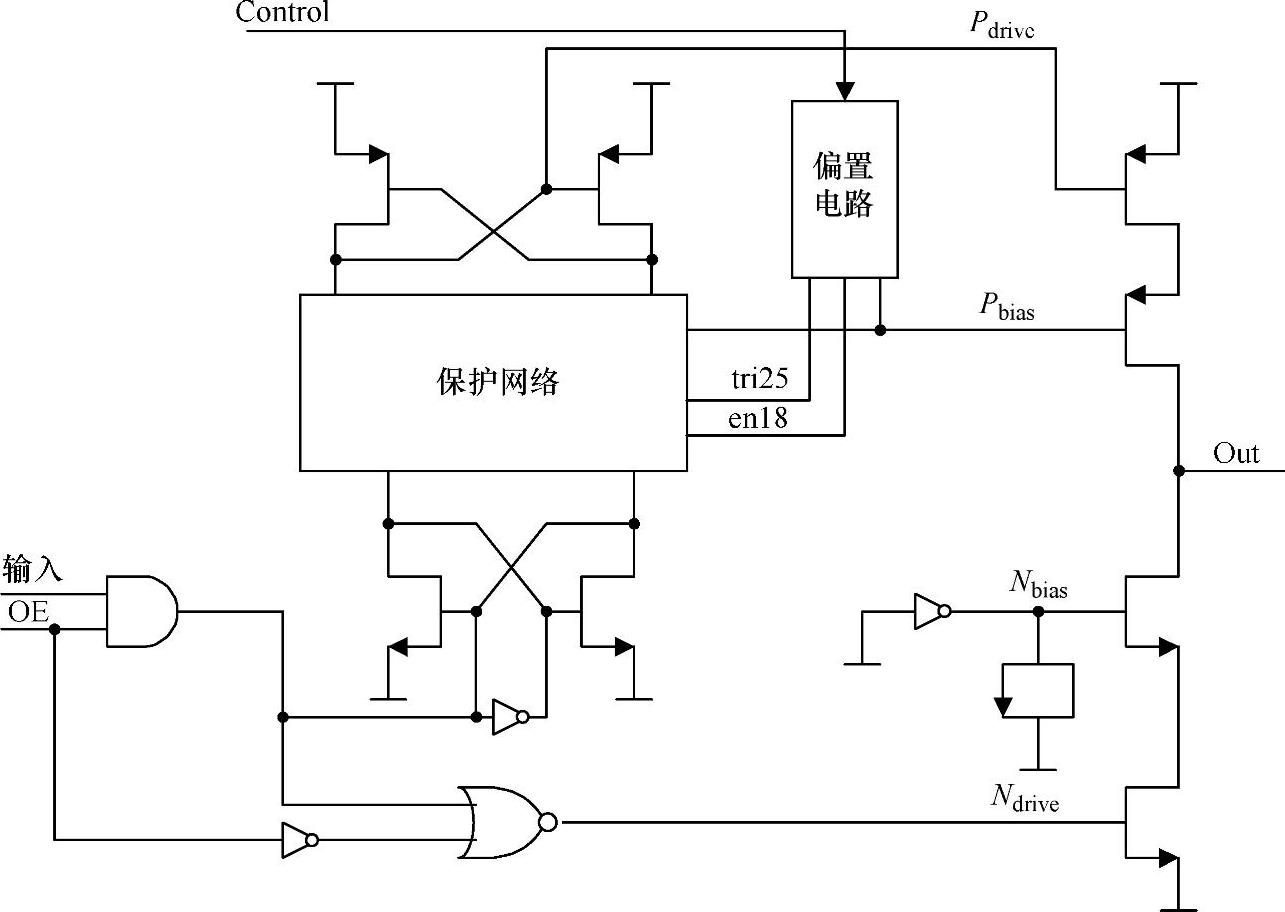

【摘要】:单端缓冲器的基本结构并没有随着工艺尺寸的缩小而变化。一个更典型的情况是要求核心芯片能适应3.3V和1.5V的I/O,需要采用多个不同的I/O标准。当时开发的这种结构是为了用1.8V的晶体管支持1.8V、2.5V和3.3V的I/O标准。层叠I/O结构可以采用较薄氧化层器件支持多I/O标准,具有改善I/O性能的潜能。这种方式存在的问题包括热插孔保护、ESD保护和不使用缓冲器时的三态输出。图6-3 层叠输出缓冲器框图

单端缓冲器的基本结构并没有随着工艺尺寸的缩小而变化。主要的变化是每个工艺节点都必须支持的更高的信号速率。如果采用固定的接口,如1.8V STTL,性能问题将会减少。这使得输出缓冲器可以采用更薄的栅氧器件进行设计,提供更好的性能和更低的电容。一个更典型的情况是要求核心芯片能适应3.3V和1.5V的I/O,需要采用多个不同的I/O标准。设计者只能从下述两种方案中选用一种:使用可以支持更高电压的氧化层厚度同时能容忍低电压标准的性能问题,或使用较薄的氧化层器件同时采用复杂的结构以避免器件受到3.3V标准的过电压条件。氧化层较厚的器件所具有的较高阈值电压和接口电路要求的较低电源电压会引起性能问题。图6-3是参考文献[4]中介绍的一种层叠输出缓冲器的简化电路图。当时开发的这种结构是为了用1.8V的晶体管支持1.8V、2.5V和3.3V的I/O标准。层叠I/O结构可以采用较薄氧化层器件支持多I/O标准,具有改善I/O性能的潜能。通过给Pbias与Nbias提供适当的偏置,可以产生一个受控的阻抗,实现板级信号和负载的匹配,减少反射,改善信号完整性。利用层叠结构的优点并采用一组器件实现期望的阻抗,可以改善输出阻抗控制。这种方式存在的问题包括热插孔保护、ESD保护和不使用缓冲器时的三态输出。

(https://www.xing528.com)

(https://www.xing528.com)

图6-3 层叠输出缓冲器框图(来源于参考文献[4])

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。