在过去的30年产生了许多的I/O标准。主要的标准包括:先进图形端口(AGP)、电流型逻辑(CML)、发射极耦合逻辑(ECL)、正发射极耦合逻辑(PECL)、发射接收逻辑(GTL)、高速收发器逻辑(HSTL)、残余连续终结逻辑(SSTL)、低压CMOS(LVCMOS)、低压差分信号(LVDS)、超高速连接(它是LVDS标准的子集)、低压发射极耦合逻辑(LVPECL)和低压晶体管晶体管逻辑(LVTTL)。这些标准中许多是单端的,使性能受到严重制约。目前真正的高速接口电路主要使用的I/O标准是HSTL、SSTL、LVDS、LVPECL(以及其他形式的ECL)和CML。CML缓冲器一般用于速度最高的应用中。

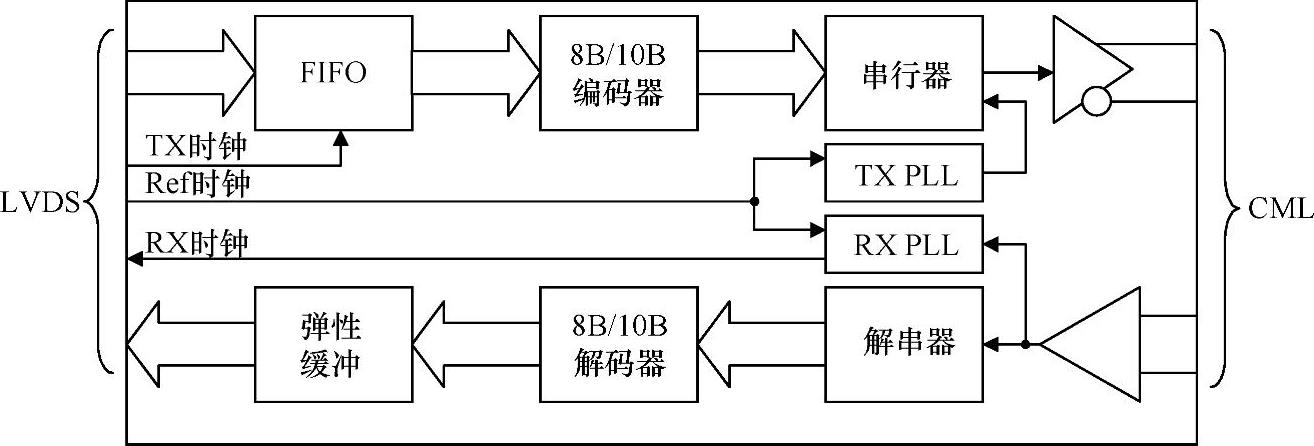

目前I/O缓冲器中使用的两个基本信号配制是:单端和差分。单端信号的工作速度不超过600~800Mbit/s,主要是满足存储器接口电路的需求,虽然采用其他一些技术已经可以获得更高的速率[5]。对LVDS标准,差分标准具有1~1.5Gbit/s的数据传输速率,并且在CML标准下速率可高达10Gbit/s(并可能更高)。差分I/O标准可以分为两大类:并行总线和串行连接。LVDS标准是一种比较典型的并行总线,而CML是串行连接。图6-1所示为一个典型的高速串行系统。采用LVDS标准将并行信号从左侧输入到芯片中。数据流在传送到串行端之前使用8B/10B标准进行编码。采用这种编码方案保证时钟恢复的0→1和1→0的转换,并且使得0和1的个数平均来说基本相等,保持直流平衡。尽管这种编码方案增加了一些带宽开销,但是它依旧是使用最普遍的互连编码形式。例如,如果使用8B/10B编码并且期望的数据速率达1Gbit/s,为了解决与编码相关的开销问题,实际的传输速率必须为1.25Gbit/s。

(https://www.xing528.com)

(https://www.xing528.com)

图6-1 对并行数据采用LVDS信号而串行数据采用CML信号的典型串行系统图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。