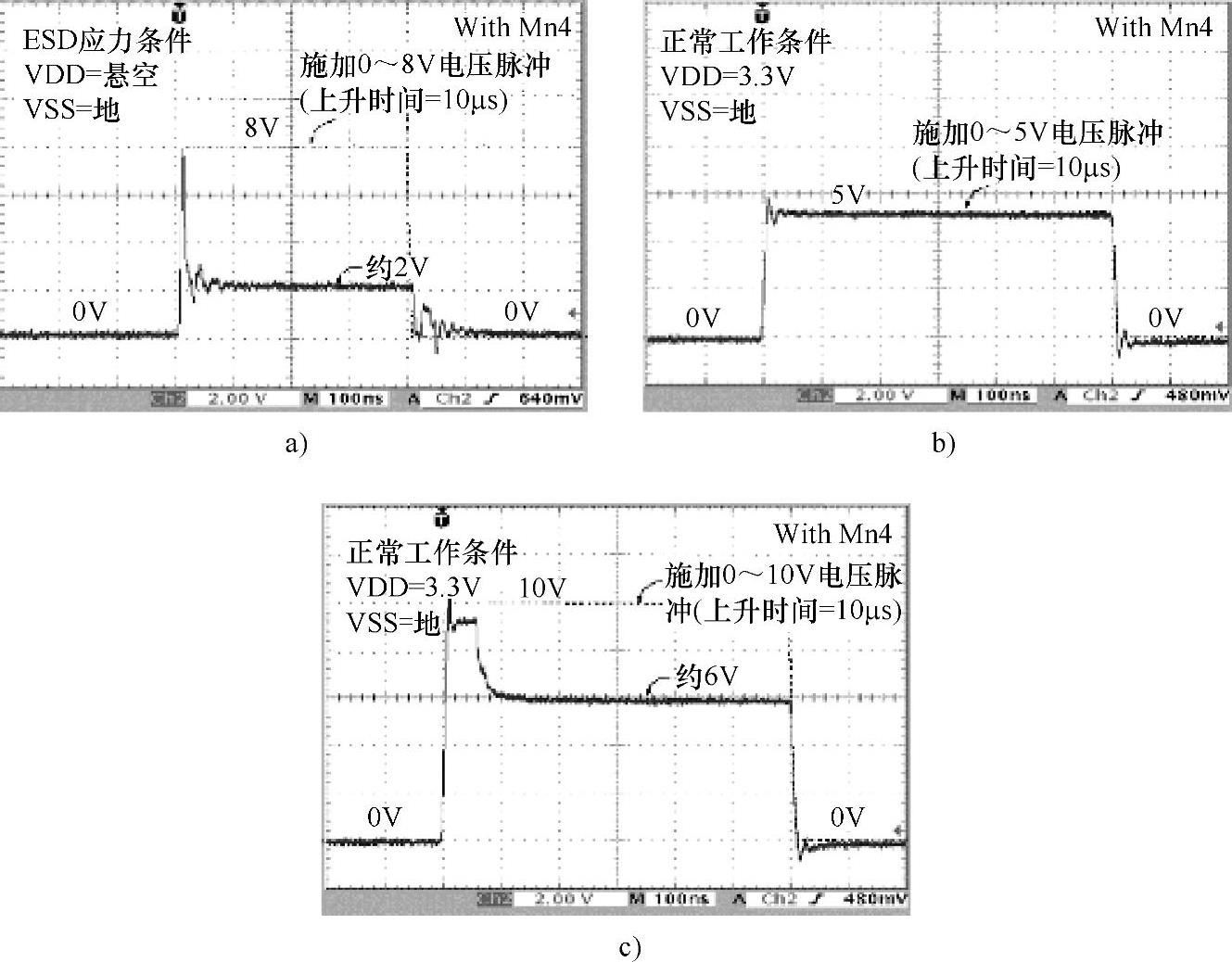

为了验证混合电压I/O的ESD保护电路开启的有效性,当VSS相对接地而VDD悬空(为了仿真PS模式的ESD应力条件)时,给I/O压焊点加一个上升时间为10ns的0V到8V的尖锐上升电压脉冲。输出缓冲器中层叠NMOS的快速反向击穿电压约为10V。这样一个加到I/O压焊点的0V到8V的脉冲并没有使混合电压输出缓冲器的层叠NMOS击穿。但是0V到8V的脉冲能触发开启ESD保护电路,从而得到一个如图5-24a所示的衰退的电压波形,其中0V到8V的脉冲被SNTSCR器件钳位到约2V。图5-24a中从8V到2V约10ns的转换时间就是用0.35μmCMOS工艺实现的SNTSCR器件相应的开启速度。

在VDD(VSS)为3.3V(0V)的电路正常工作条件情况下,给I/O压焊点加一个上升时间为10ns的0V到5V的输入电压脉冲,采用数字示波器监测I/O压焊点上电压,结果如图5-24b所示,所加的0V到5V的波形并没有衰减。在电路正常工作期间,Mn4的栅被偏置到VDD(3.3V)。通过电容C2耦合的Mn2的栅电压通过开启的Mn4泄放到地,因此SNTSCR器件并没有被正常的5V输入信号触发开启。如果所加的电压脉冲进一步增加到10V,在电路正常工作条件下,I/O压焊点上测量的电压波形如图5-24c所示,所加的0V到10V的脉冲被钳位到约6V,但是没有达到图5-24a所示的约2V的水平。在0.35μmCMOS工艺下,层叠NMOS的快速反向击穿电压约为10V,而快速反向保持电压约为6V。因此,图5-24c中所示的约6V的衰退电压是被混合电压I/O缓冲器中层叠NMOS钳位在快速反向区的结果。如果ESD保护电路中的SNTSCR器件被触发开启,这个电压水平将被钳位到它的保持电压约2V左右。这个结果进一步证明了ESD保护电路中的器件Mn4可以被安全的加到SNTSCR器件中以保护混合电压I/O缓冲器而不会在电路正常工作条件下出乎意料地触发。

(https://www.xing528.com)

(https://www.xing528.com)

图5-24 a)在PS模式ESD应力条件下,由上升时间为10ns的0V到8V电压脉冲触发,在I/O压焊点测量的电压波形(y轴:2V/div;x轴:100ns/div) b)在正常工作条件下,VDD=3.3V,VSS=0V,由上升时间为10ns的低电平为0V到高电平为5V的电压波形 c)低电平为0V到高电平10V电压脉冲触发,在I/O压焊点测量的电压波形(y轴:2V/div;x轴:100ns/div)

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。