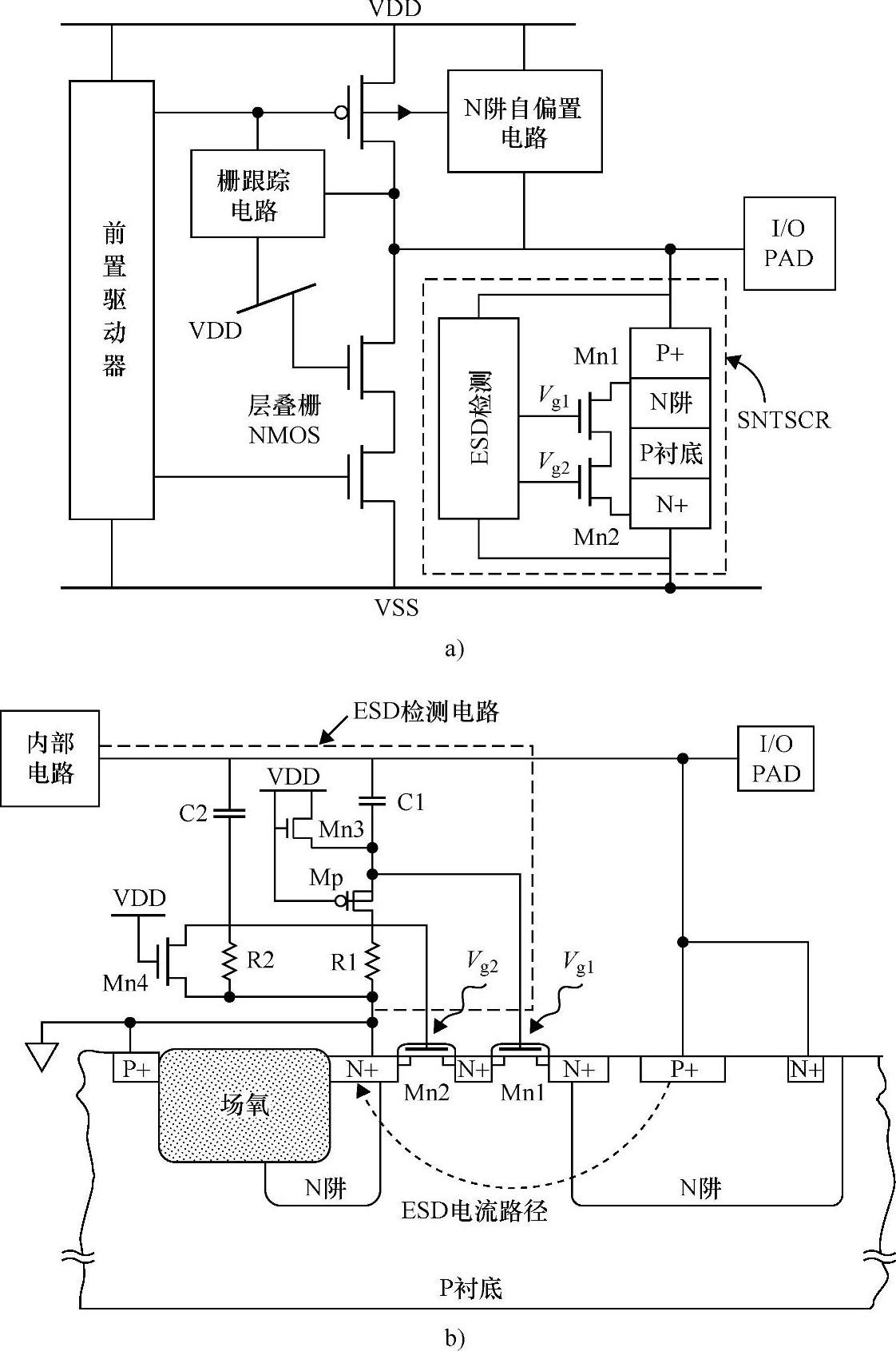

基于对SNTSCR器件的实验研究,采用SNTSCR的保护混合信号电压I/O缓冲器的ESD保护设计如图5-22a所示。其中设计了一个ESD检测电路可以在ESD应力条件下提供合适的栅偏置从而触发SNTSCR器件。另外,这个ESD检测电路必须使SNTSCR器件在IC处于正常工作条件时保持关断。使用栅耦合技术设计并考虑了栅氧化层可靠性问题的ESD检测电路如图5-22b所示。

在电路正常工作条件下,SNTSCR处于关断状态,因此它不会干扰I/O压焊点的电压信号。在这种状态下,图5-22b所示的Mn3起电阻作用,将Mn1的栅压(Vg1)偏置到VDD,而Mn2的栅通过电阻R2接地。当I/O压焊点加的是5V高输入电压时,Mn1与Mn2晶体管之间共用的n+区的电压约为VDD-Vthn(Vthn是NMOS器件的阈值电压)。所以ESD保护电路中的所有器件在电路正常工作期间都能满足不会使栅氧化层中电场太强的要求。当I/O压焊点的电压从0V变到5V时,通过电容C1耦合的电压也会使Mn1的栅压增加。因此图5-22b所示的PMOS器件(Mp)被设计为一旦Mn1的栅压增加到VDD+Vthp(Vthp是Mp的阈值电压)时超过的电压便受到钳位。适当设计ESD检测电路可以确保SNTSCR器件在电路正常工作条件下处于关断状态。另外,即使I/O压焊点上有高输入电压,PMOS(Mp)可以进一步钳位Mn1的栅压以保证Mn1栅氧的可靠性。

图5-22 a)采用SNTSCR器件保护混合电压I/O缓冲器的ESD保护电路 b)保护混合电压I/O缓冲器的ESD检测电路设计中,SNTSCR器件采用有较大的维持电阻和耦合电容设计范围(https://www.xing528.com)

电容(C1和C2)、电阻(R1和R2)、Mp和Mn3组成一个给SNTSCR器件提供合适栅偏置的ESD检测电路。电容C1(C2)被设计来耦合ESD瞬态电压到Mn1(Mn2)的栅上以降低SNTSCR器件的触发电压。为了触发SNTSCR器件进入保持区,电阻R1(R2)被设计为可以较长时间维持Mn1(Mn2)栅上的耦合电压。为了改善设计范围从而可以在常规的CMOS工艺中轻易地选择合适的维持电阻和耦合电容,在Mn2的栅和VSS之间的维持电阻R2上跨接了器件Mn4。器件Mn4的栅被偏置到VDD,但是考虑到与工艺相关的天线效应问题,最好通过扩散电阻将栅连接到VDD电源线。在电路正常工作条件下,Mn4总是处于开启状态从而把耦合电压Vg2钳位到阈值电压(Vthn)之下,并且保持Mn2关断。所以,在电路正常工作条件下,可以保证SNTSCR被关断。

在PS模式ESD应力条件下,加到I/O压焊点的是一个较高的正ESD电压,VSS接地而VDD悬空。在这种应力条件下,因为悬空的VDD电源线上的初始电压为零,使得Mp的栅被接地。因此Mp开启,而Mn3关断。电容C1和C2的作用是分别将ESD瞬态电压从I/O压焊点耦合到Mn1和Mn2的栅极。设计应该使得耦合电压高于阈值电压,从而保证混合电压I/O电路中的器件在被ESD能量损伤前能开启Mn1和Mn2,将SNTSCR器件触发开启。另外,在ESD应力条件下,悬空的VDD电源线上的初始电平为零,因此Mn4关断。耦合到Mn2栅上的电压由维持电阻(R2)和耦合电容(C2)决定。当SNTSCR被触发开启时,ESD电流主要通过SNTSCR器件从I/O压焊点泄放到VSS。SNTSCR器件具有较低的触发电压和较低的保持电压,可以安全的保护混合电压I/O电路的薄栅氧,还可以以较小的芯片面积达到较高的ESD级别。

ESD检测电路的作用是在电路正常工作条件与ESD应力条件下给SNTSCR器件提供一个合适的栅偏置。为了得到合适的栅偏置,耦合电容(C1和C2)和维持电阻(R1和R2)值的确定非常重要。基于前面的工作原理,为了在各种CMOS工艺下都能保证电路如期望的那样工作,可以用HSPICE仿真方法精细调整确定合适的C1、C2、R1和R2值。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。