本节将介绍一种新的ESD保护设计,通过采用层叠NMOS来触发SCR器件可以极大地改善混合电压I/O缓冲器的ESD鲁棒性[80,81]。针对混合电压I/O电路,在新的ESD保护电路中,SCR器件采用层叠NMOS结构栅耦合电路技术,它可以与普通的CMOS工艺充分地兼容而不会引起栅氧化层可靠性问题。不需要采用厚的栅氧,针对3V/5V容限的混合电压I/O缓冲器的新ESD保护设计已经在0.35μmCMOS工艺中成功得到验证,并且应该在更小尺寸的工艺中也是适用的。

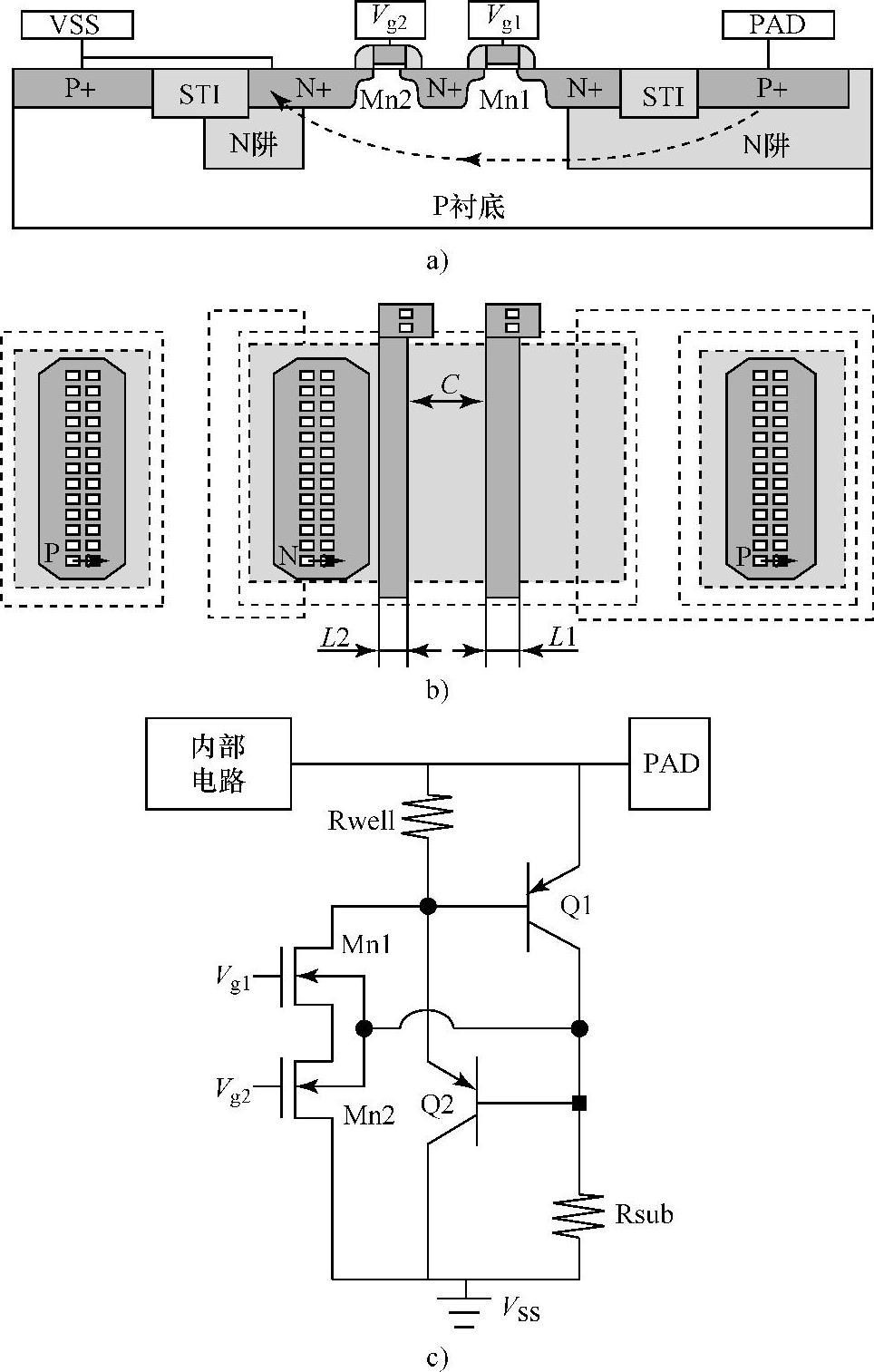

层叠NMOS触发晶闸管(SNTSCR)的剖面图与相应的版图分别如图5-19a与图5-19b所示。这种SNTSCR器件结构可以在典型的CMOS工艺中实现而不需要额外的工艺调整。在键合压焊点安排SNTSCR器件可以保护混合电压I/O电路免受ESD损伤。这种SNTSCR器件对应的等效电路如图5-19c所示。

在SNTSCR器件中,两个NMOS晶体管(Mn1和Mn2)以串接方式层叠在一起,其中Mn1的漏跨接在N阱与衬底之间的结上。在I/O压焊点与VSS之间由P+扩散、N阱、P衬底和n+扩散形成的一个横向SCR器件如图5-19a中虚线所示。以层叠方式连接Mn1和Mn2的目的是为了在电路正常工作条件下能承受高电压水平的输入信号而不引起SNTSCR器件栅氧化层的可靠性问题。如果只采用单个NMOS,例如像传统的LVTSCR那样[82],当高压信号进入I/O压焊点时,栅氧化层上的电压将高于VDD。如果传统的LVTSCR长期工作在这种混合电压I/O电路中,将引起栅氧化层可靠性问题。在ESD应力作用期间,栅偏置设计适当的Mn1和Mn2都将开启,触发横向SCR开启以泄放ESD电流。在CMOS工艺中无需厚栅氧器件,采用提出的SNTSCR器件作为保护混合I/O电路,不会引起栅氧化层可靠性问题。这种ESD结构对深亚微米工艺来说变得日益重要,其中薄栅氧器件被用在I/O结构中以减小高速应用时的引脚电容,并且

图5-19 提出的采用p衬底CMOS工艺的SNTSCR器件

a)剖面图 b)相应的版图 c)等效电路

仍然与高压IC接口。

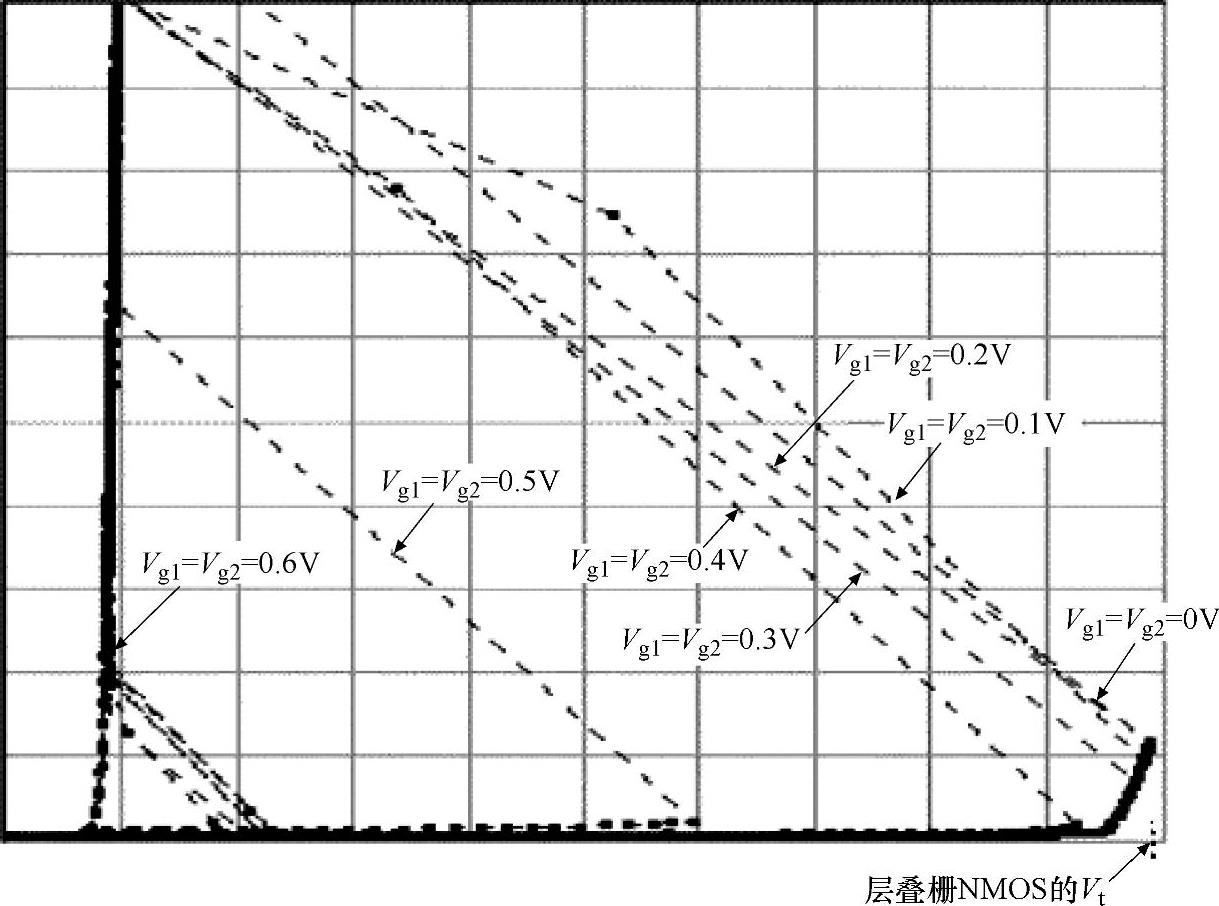

为了研究SNTSCR器件的特性,可以调整三个版图尺寸参数(图5-19b中所示的C、L1和L2)。其中L1和L2分别是Mn1和Mn2的沟道长度,C是跨越在Mn1和Mn2器件共用的n+扩散区两侧多晶到多晶之间的间距。采用0.35μm工艺制造了版图参数不同但是沟道宽度固定为60μm的这种SNTSCR器件。其中C=0.5μm而L1=L2=0.35μm的一个SNTSCR器件在不同栅偏置Vg1和Vg2时的I-V特性曲线如图5-20所示。当栅偏置从Vg1=Vg2=0V增加到Vg1=Vg2=0.5V时,SNTSCR器件的触发电压(Vt)从10V下降到6V。当Vg1=Vg2>0.6V时,Mn1和Mn2都导通并触发SNTSCR开启,因此Vt下降到1V~2V。给Mn1和Mn2加适当的栅偏置,SNTSCR器件的触发电压将低于混合电压I/O缓冲器中层叠NMOS的快速反向击穿电压。因此,新提出的采用SNTSCR器件的ESD保护电路能有效保护混合电压I/O缓冲器。(https://www.xing528.com)

图5-20 不同栅偏置时测得的C=0.5μm而L1=L2=0.35μm的一个实际SNTSCR器件的I-V曲线(x轴:1V/div;y轴:1mA/div)

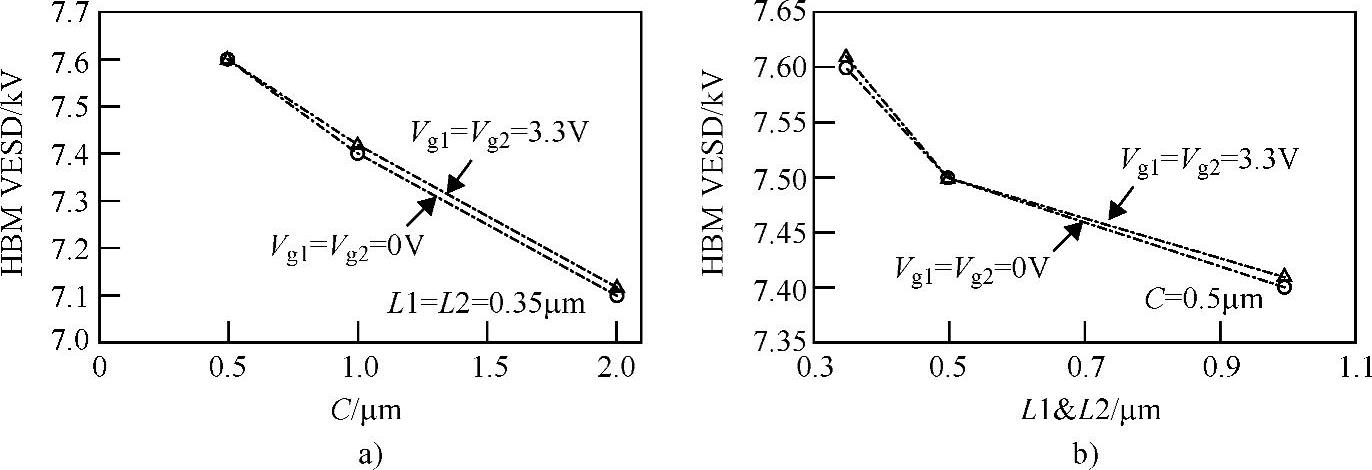

版图参数和栅偏置对SNTSCR器件在PS模式的HBM ESD级别的影响如图5-21a和图5-21b所示。图5-21a显示的是固定沟道长度L1=L2=0.35μm,SNT-SCR器件的HBM ESD级别与版图参数C之间的关系。图5-21b显示的是固定版图参数C=0.5μm,SNTSCR器件的HBM ESD级别与沟道长度L1和L2之间的关系。失效判据确定为偏置电压为5V时,泄漏电流大于1μA。当版图参数C、L1和L2增加时,SNTSCR器件的HBM ESD鲁棒性稍有衰退。版图参数(C、L1和L2)较小的SNTSCR器件具有较窄的阳极到阴极间距,这意味着更小的导通电阻。因此,版图参数(C、L1和L2)较小的SNTSCR器件有较高的ESD级别。栅偏置Vg1与Vg2并没有明显地改善SNTSCR器件的ESD级别(见图5-21),但是它能较早的触发SNTSCR以泄放ESD电流。这样,栅偏置设置合适的SNTSCR器件可以有效保护CMOS IC的混合电压I/O缓冲器。

图5-21 a)不同栅偏置(Vg1=Vg2)时HBM ESD级别与SNTSCR器件版图参数C之间的关系。失效判据:Vbias=5V时,Ileakage>1μA b)不同栅偏置(Vg1=Vg2)时HBM ESD级别与SNTSCR器件版图参数L1和L2之间的关系。失效判据:

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。