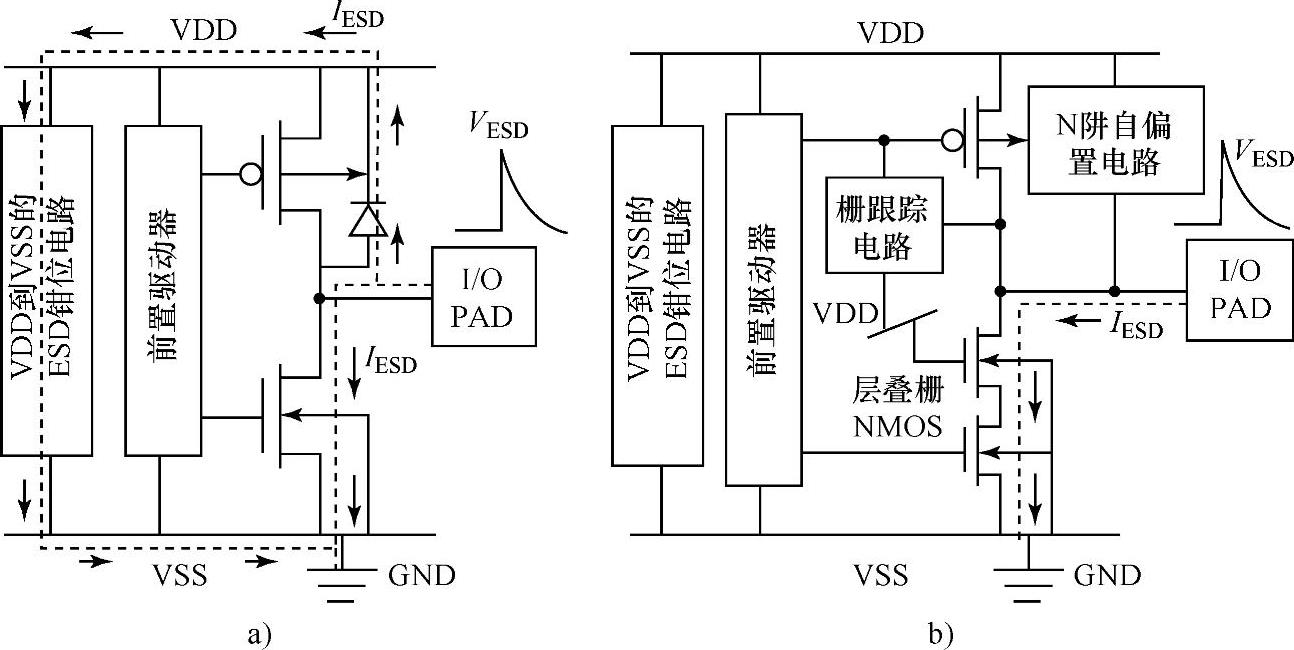

I/O压焊点上的ESD应力有四种引脚组合模式:正脉冲作用于VSS(PS模式)、负脉冲作用于VSS(NS模式)、正脉冲作用于VDD(PD模式)和负脉冲作用于VDD(ND模式)四种ESD应力条件。为了使CMOS输出缓冲器有足够高的ESD鲁棒性,CMOS缓冲器一般设计成具有大的器件面积和较宽的漏接触到多晶栅间距,这常常在I/O单元中占据较大的版图面积。在无需增加I/O单元器件面积的情况下,CMOS IC电源线上的VDD到VSS的ESD钳位电路已成功用于改善CMOS I/O缓冲器的ESD鲁棒性[55]。在PS模式ESD应力条件下传统CMOS输出缓冲器的ESD电流通路如图5-18a中虚线所示,大部分ESD电流通过PMOS的寄生二极管和VDD到VSS的ESD钳位电路泄放到地。因此,传统的CMOS输出缓冲器可以经受高ESD应力。但是由于考虑到混合电压I/O缓冲器的泄漏电流问题,在I/O压焊点和VDD电源线之间将不会有寄生二极管。因为在混合电压I/O电路中压焊点与VDD之间不能放置二极管,作用在I/O压焊点上的PS模式的ESD电压不能从压焊点被转移到VDD电源线,并且不能通过附加的电源轨(VDD到VSS)ESD钳位电路泄放。这种压焊点上的PS模式的ESD电流完全通过快速反向击穿的层叠NMOS泄放。在PS模式ESD应力条件下沿着混合电压输出缓冲器的ESD电流如图5-18b中虚线部分所示。层叠配置中的NMOS器件具有比单个NMOS更高的触发电压(Vt1)、更高的快速反向保持电压(Vsb)和更低的二次击穿电流[74]。因此,这种采用层叠NMOS结构的混合电压I/O电路的ESD级别一般比单个NMOS I/O电路的ESD级别低很多[74,75]。所以混合电压I/O电路在PS模式ESD应力条件下一般有最低的ESD级别(采用人体模式ESD测试时一般<2kV)。由于在I/O压焊点与VDD电源线之间没有寄生二极管,在ND模式应力条件下,混合电压I/O电路的ESD级别也较低。因此,混合I/O电

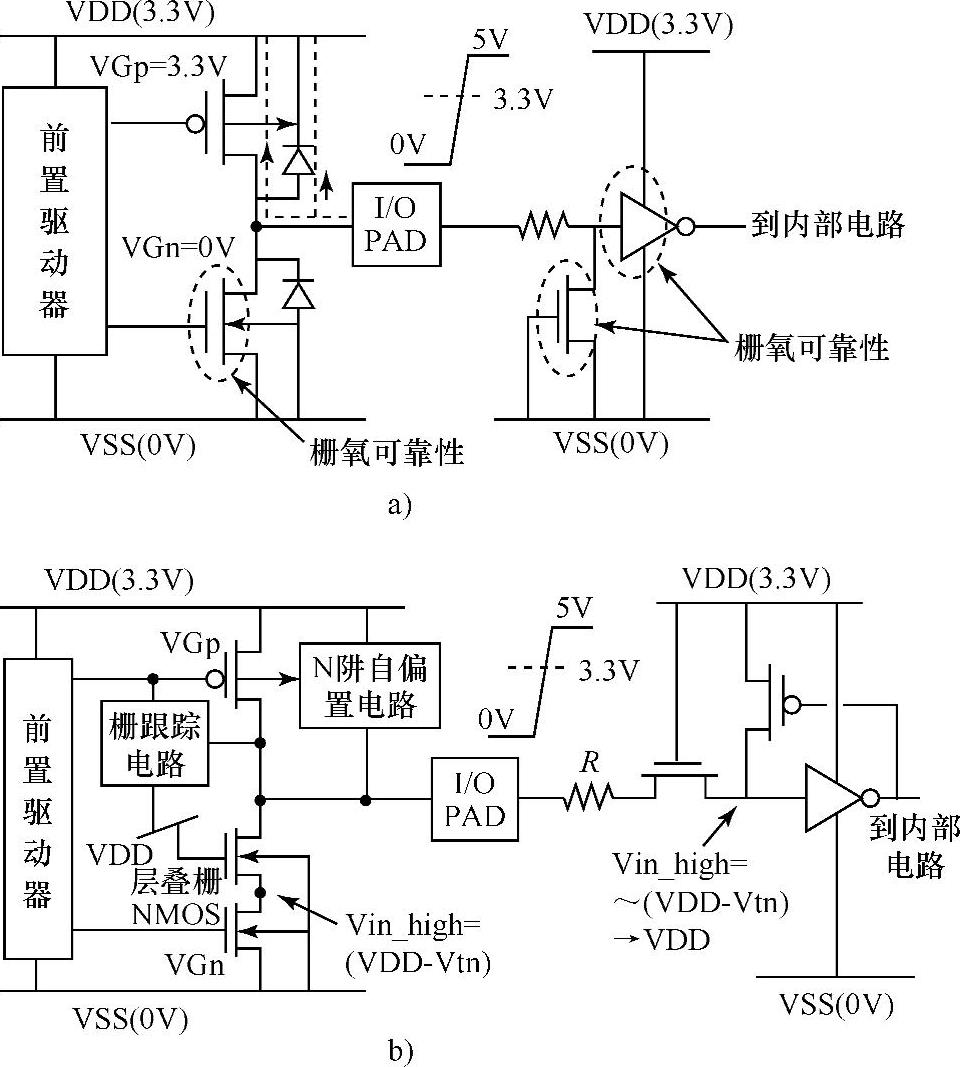

图5-17 缓冲器典型电路框图

a)传统的CMOS I/O缓冲器 b)采用层叠NMOS和自偏置阱PMOS的混合电压I/O缓冲器

路的ESD保护设计主要着重于改善正ESD应力条件下的ESD级别。(https://www.xing528.com)

图5-18 在PS模式ESD应力条件下缓冲器中ESD电流路径

a)传统的CMOS输出缓冲器 b)混合电压输出缓冲器

为了增加这种混合电压I/O电路的ESD级别,I/O压焊点与VDD电源线之间采用了一些在层叠结构中添加多个二极管的设计[63,64]。然而,当混合电压I/O电路工作在高电压输入、高温环境时,必须采用附加电路设计,减小从压焊点通过层叠二极管到VDD的正向泄漏电流[76-79]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。