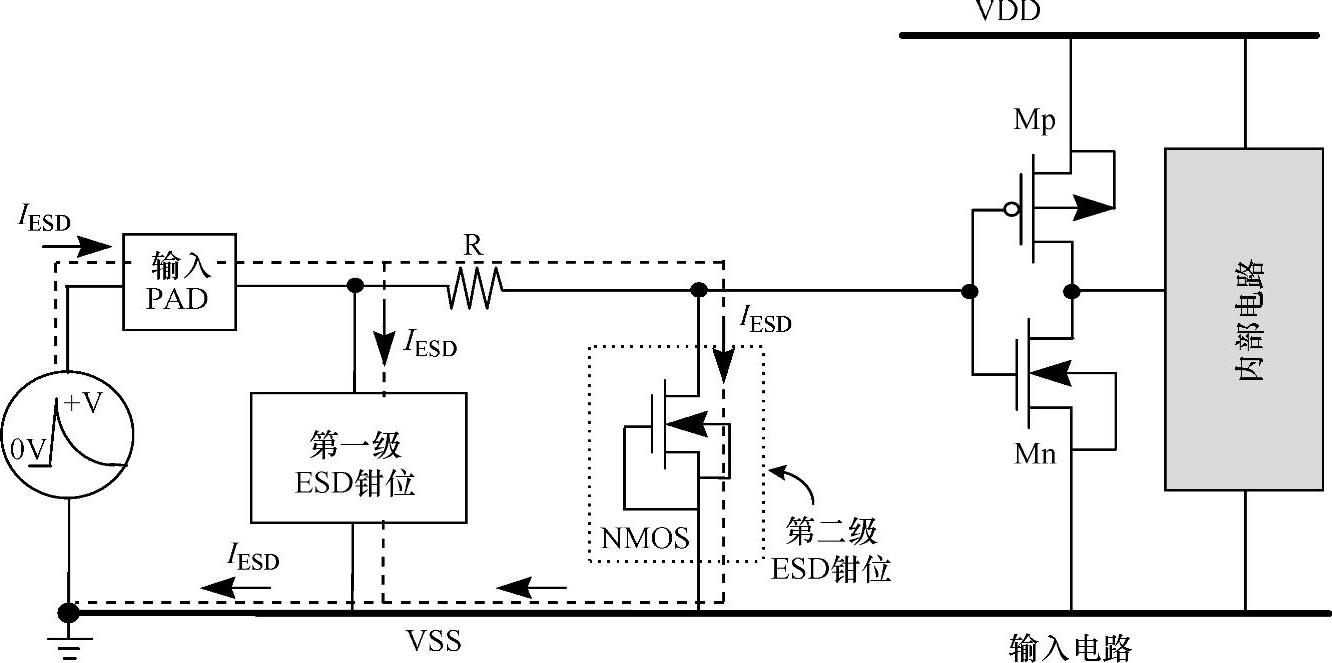

数字输入引脚通常采用的两级结构ESD保护设计,如图5-6所示。其中使用了一个栅极接地的短沟NMOS作为第二级保护器件,它可以钳位输入电路栅氧上的过应力电压。为了提供高ESD保护水平,第一级保护级采用一个鲁棒器件(例如SCR、场氧器件或长沟道NMOS)作为主要泄放单元以旁路输入压焊点上的ESD电流。在输入ESD保护电路的第一级与第二级之间,增加一个电阻来限制流过第二级短沟NMOS的ESD电流。其阻值取决于第一级ESD钳位器件的开启电压和第二级短沟NMOS器件的二次击穿电流。在第二级栅接地NMOS(GGNMOS)被过应力ESD电流损伤前,第一级ESD钳位器件必须被触发开启以旁路ESD电流。如果第一级ESD钳位器件的开启电压较高,则电阻应该足够大:大约在几百欧姆的级别。这种两级ESD保护设计能给数字输入引脚提供很高的ESD容限级别。但是较大的串联电阻和ESD钳位器件较大的结电容会引起较长的输入信号RC延迟,因此不适合用于模拟信号和高速I/O应用,而这两种情况在更先进的工艺中变得更占主导地位。

图5-6 CMOS IC中数字输入引脚通常采用的两级结构ESD保护电路

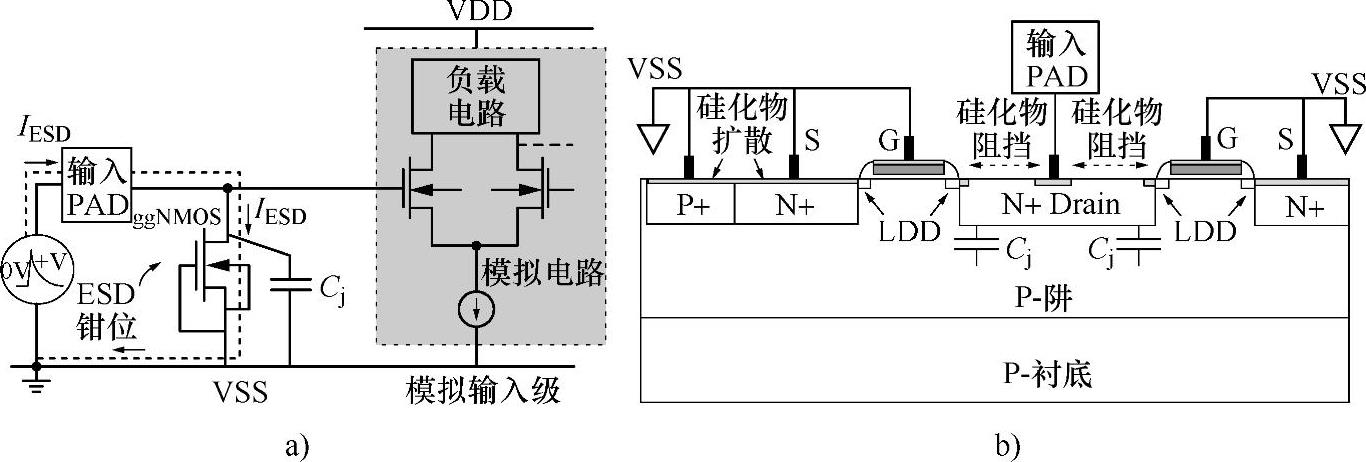

对模拟输入信号和高速I/O应用,在输入压焊点与内部电路之间一般不允许存在串联电阻。因此图5-6所示两级ESD保护设计不再适合于模拟和高速I/O引脚。为了保护模拟或高速I/O引脚,一般采用如图5-7a所示的只有单级ESD设计的ESD保护电路,其中采用GGNMOS作为ESD钳位器件。在先进的深亚微米CMOS技术中,由于缺少了限制ESD电流流向GGNMOS的串联电阻,也缺少NMOS器件的ESD鲁棒性,因此使ESD保护严重衰退[51,52]。GGN-MOS的设计一般具有很大的面积、漏与多晶硅栅接触之间的版图间距较宽,以维持能满足要求的ESD级别[16,52,53]。在深亚微米CMOS工艺中包括了附加的金属硅化物阻挡掩膜[40-44]以增加ESD钳位器件的鲁棒性。图5-7b是采用金属硅化物阻挡漏区GGNMOS的剖面示意图。但是有更大器件面积和更宽漏

(https://www.xing528.com)

(https://www.xing528.com)

图5-7 a)用于CMOS IC中模拟输入引脚的单级ESD饱和电路 b)具有金属硅化物阻挡漏区的GGNMOS的剖面图

区的GGNMOS给输入压焊点增加了很大的寄生漏电容。这样的寄生漏电容是非线性的并且电容大小与输入电压水平有关,对实际的高速I/O和模拟输入,这是不可接受的。

对一些高分辨率的数据转换器电路,要求在输入电压范围内模拟信号输入脚的输入电容尽可能保持为常数。高速模拟电路中,特别是在单端输入应用中,主要的失真源是模拟信号输入压焊点的ESD钳位器件具有的与电压有关的非线性电容。参考文献[65]报道了由于输入ESD钳位器件的非线性电容造成的电路性能的典型衰退情况。对于输入电压从0到2V的变化,输入电容的变化范围为4~2pF。电容的变化引起模数转换器(ADC)谐波失真的增加,并且使ADC的精度从14位退化到10位。这样,在采用缩小尺寸CMOS技术的高精度模拟应用中,设计有效的ESD保护电路已面临挑战。5.4.2节将详细介绍具有较小输入电容、无串联电阻和高ESD级别优势的小电容ESD保护设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。