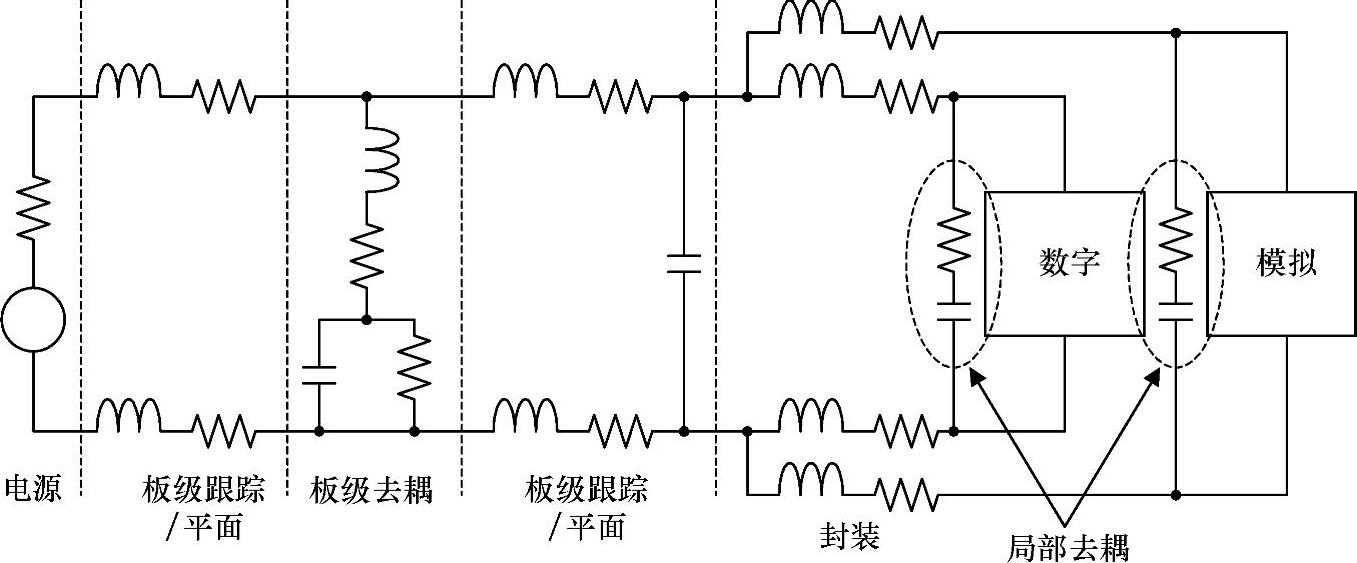

对深亚微米工艺来说,因为器件密度更大、边沿速率更快、电源电压更低,去耦已经越来越成为一个问题。对高速输出缓冲供电,瞬时IR压降已经达到伏特的级别。而对于低电压的内核电源,瞬时IR压降则达到了几百毫伏。对给定的电路模块,IR压降源于电源轨上的串联电阻和感抗。图4-25所示为一个有IC的电路板简化图。在板级增加的去耦元件可以减小板级的电源纹波,但是由于器件封装和芯片寄生参数的影响,在芯片级增加去耦所起作用一般极小。各种寄生参数的确切值很难提供,但是对引线键合封装,电感的范围是5~10nH。对倒装焊芯片封装来说,电感小于1nH。图中显示的模拟与数字部分的电源被完全隔离。

图4-25 带有IC的电路板

采用下述两个简单的方程可以分析电感和去耦对电压降的作用:

考虑串联电感为1nH、在30ps中电流变化为1mA(对0.13μm和小于0.13μm工艺来说,这并非是个不现实的数字)的简单情况,电感上的IR压降约为33mV,这个值的影响已经很重要了,特别是考虑电流会变到多高时。

图4-26所示为一个NMOS去耦电容的简化图。因为与其他去耦方式相比,单位面积栅氧电容的容值较大,由此,栅氧电容是最普遍用作去耦单元的器件。设计去耦单元时必须考虑寄生参数,如果忽略它们将导致不正确的假设,即认为插入单个大面积的栅就可以形成较大的去耦单元。实际上,这样形成的去耦单元较差,因为栅长两端沟道电阻将会增加,在电容上引起较大的串联电阻。另外,多晶硅密度规则也不允许这种情况。实际上,仅在靠近边缘的栅区对电容有贡献。使这个效应最小化的唯一方式就是使沟道长度更小。这必须与使用的单元数和每单元的电容相匹配。总的沟道电阻可以从VDS较小区域范围的IDS-VDS曲线上提取。

图4-26 NMOS栅电容

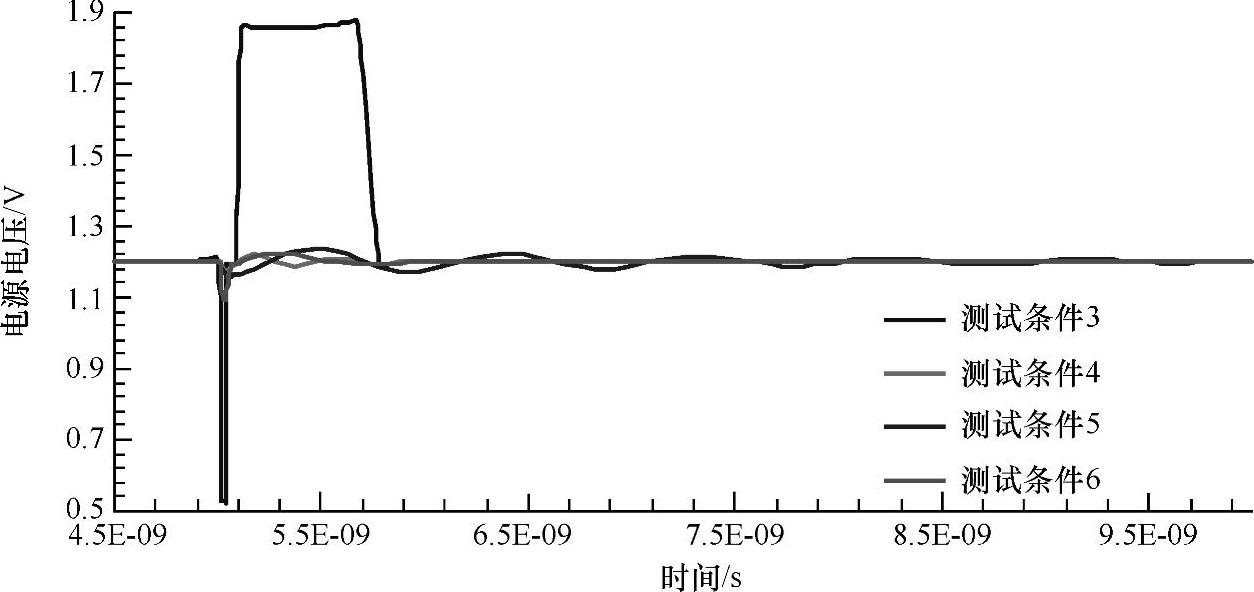

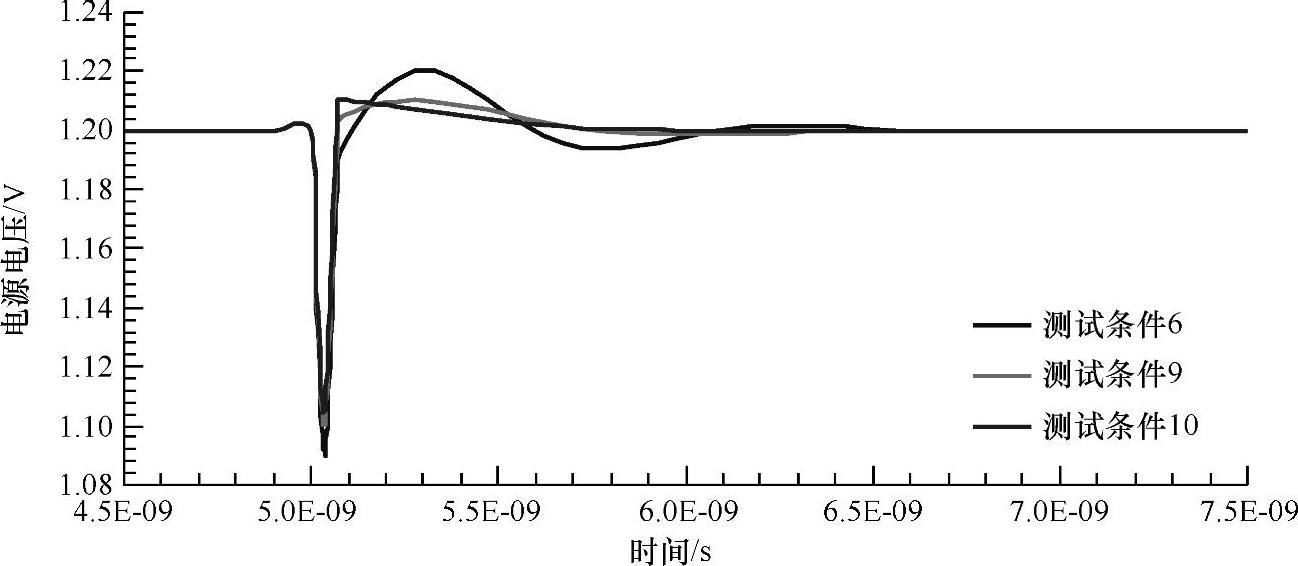

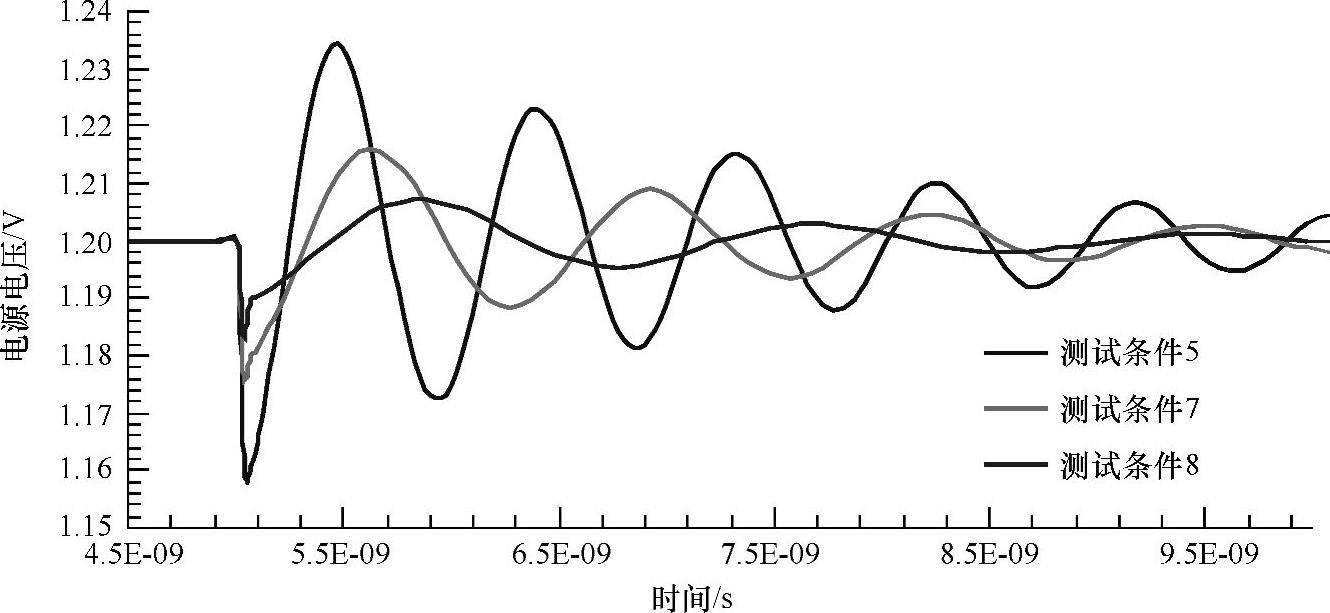

图4-27所示为去耦单元的简化模型。通常采用多个去耦单元并联,等效于图4-27右侧所示的电路。将多个去耦单元并联,就可能获得较小的有效串联电阻和较大的电容。最右侧的电路被用来模拟几种测试情况以说明封装寄生和去耦效应。假设电流源产生一个上升沿和下降沿为30ps、峰值为10mA的电流(这在90nm工艺种是有可能的)。图4-28所示为电流源的电流变化时电源电压上的感抗效应。图4-29所示为当去耦单元的串联电阻较高时去耦是如何的无效,这说明了使电容单元的寄生电阻最小化或确定并联单元足够多的重要性。图4-30说明了使串联电阻最小化是如何允许电容给电路提供必需的电流,减小电源压降的。表4-2总结了这些测试情况下的数值。

表4-2 去耦仿真结果简要总结

(https://www.xing528.com)

(https://www.xing528.com)

图4-27 等效电容的定义

图4-28 电源电压在无去耦和高感抗(测试条件3)、低感抗和有一定去耦(测试条件4)、高感抗和有一定去耦(测试条件5)与高感抗和有一定去耦以及高串联电阻(测试条件6)等条件下的变化

图4-29 电源电压在高感抗、高串联电阻和去耦电容分别为10pF(测试条件6)、20pF(测试条件9)和40pF(测试条件10)等条件下的变化

图4-30 电源电压在高感抗、低串联电阻和去耦电容分别为10pF(测试条件5)、20pF(测试条件7)和40pF(测试条件8)等条件下的变化

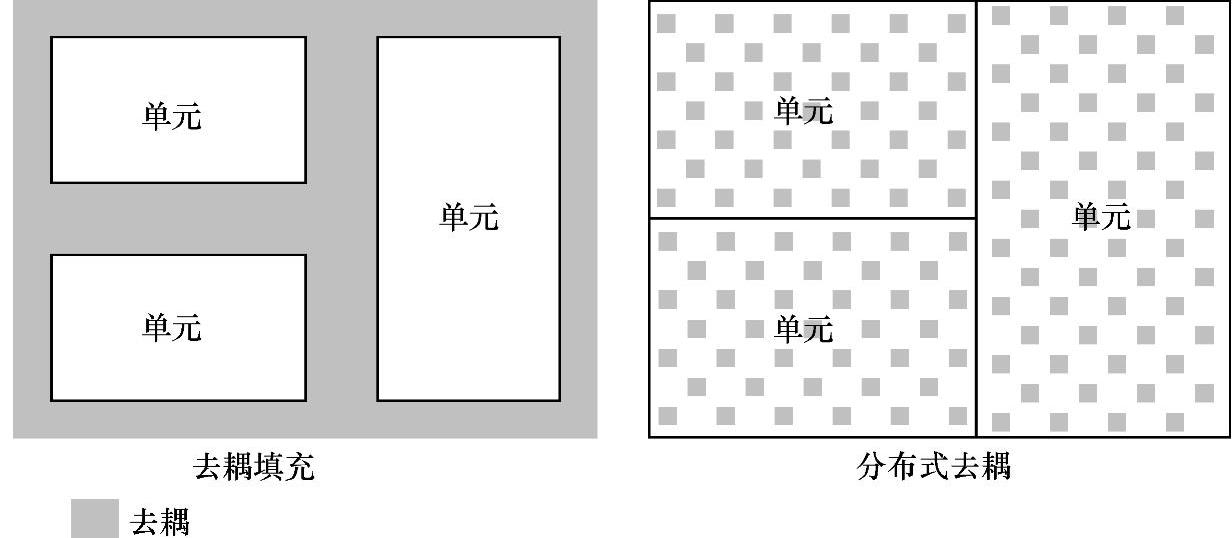

可以采用多种方法在设计中增加去耦。主要的两个方法如图4-31所示。去耦填充方法是在所有的空白区域填充去耦单元。只有在完成版图设计后才添加去耦电容的情况下才能采用这种方法。但是对某些电路,如VCO单元,一般需要用一个较宽的去耦电容环围绕其模块。第二种方法是将去耦电容分散到各个单元。这种方式要求在版图设计前进行更多的前端布局规划和仿真,但是许多情况下会获得比第一种方法更好的性能,因为去耦单元被贴近放置在需要去耦的单元旁边。确定去耦单元的数量有一点困难。一种方式是首先提取模块的平均功耗,然后使用

来评估所需去耦的数量。这里必须使用最大的工作频率。这给确定去耦数目提供了较好的出发点。但是,在实际上,用于评估电源总线寄生所进行的仿真是确定是否已提供了充分去耦的最佳方式。

图4-31 两种去耦方案

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。