保护环被广泛用来减小衬底中的噪声。已经进行了很多研究来探寻各种配置的优点[18-35]。关于如何更好的设计保护环结构使系统不同部分之间的耦合最小化方面,经常会有相互矛盾的信息。目前,混合信号芯片已经成为应用最广泛的产品,而不是只在个别场合才有所应用。即使现在的微处理器也包括了一些如PLL这样的模拟电路。接收器和发射器芯片可能包括大量的模拟和数字模块。而芯片中模拟和数字部分之间的耦合会产生不希望的噪声,导致性能退化。

作为一个例子,考虑一个简单的模-数转换器电路。如果有用的输入范围是2V,并且我们使用的是12位转换器,则一位的分辨率为488μV。如果通过衬底来自电路数字部分的耦合噪声足够大,就会减小转换器的位有效分辨率。目前衬底耦合的噪声已经十分高了,在一些情况下达到毫伏的范围。为了设计高性能的集成电路,必须在设计阶段就考虑如何隔离衬底噪声。

一般来说,较宽的保护环将提供更好的隔离[31]。这是因为增加了噪声源与受影响的敏感电路之间的阻抗。噪声源与保护环/衬底引出端越近,噪声越低[31],这是因为在构成噪声的杂散载流子有机会通过衬底扩散之前,就已经在靠近源的附近被轻易地收集了。噪声源与接收器之间的距离也有着十分重要的影响[31]。根据参考文献[23]的结论,隔离效果与分开的间距成线性关系,从阻抗的角度来看这是非常有道理的,因为电流的主要部分靠近表面流动,这很容易被保护环有效的收集。最终的性能和必需的间隔取决于衬底掺杂。最优的间距必须根据工艺信息来决定。对隔离电路有几种不同的策略。采用外延结构时,对被噪声困扰的电路,衬底上的保护环和紧临的隔离作用不大。对非外延结构,可以采用P+保护环、P+保护环与n阱环、二氧化硅沟槽、SOI和深n阱结构。这些保护结构的实际效果好坏取决于电源总线方案的设计与整个工艺规范(掺杂等)。许多研究表明,添加n阱保护环对改善隔离的作用很小,并且实际上会使噪声性能退化[19,31]。

对轻掺杂衬底,采用背面连接实际上会增加噪声[24]。这可能是由于背面连接引起阻抗增加,从而使载流子更可能流向敏感的电路而不是流出器件。抗噪声能力极大依赖于敏感电路相对于噪声源的位置、晶圆厚度和背面连接的压焊配置。而对于外延片,由于衬底的阻抗较低,情况将会不同。

与保护环的连接也是很重要的因素[28]。减小保护环连接的感抗能够极大地改善隔离效果。单独采用一个保护环引出端将有助于进一步改善隔离效果[23]。在低速电路中,衬底建模为阻性网络就足够了,但是在非常高速的IC中,衬底并不能被建模为纯阻性网络[18]。对高速电路采用Pisces和Medici进行仿真会因为较长的仿真时间而变得并不可行,但是这些工具可用于洞察通过衬底的耦合。(https://www.xing528.com)

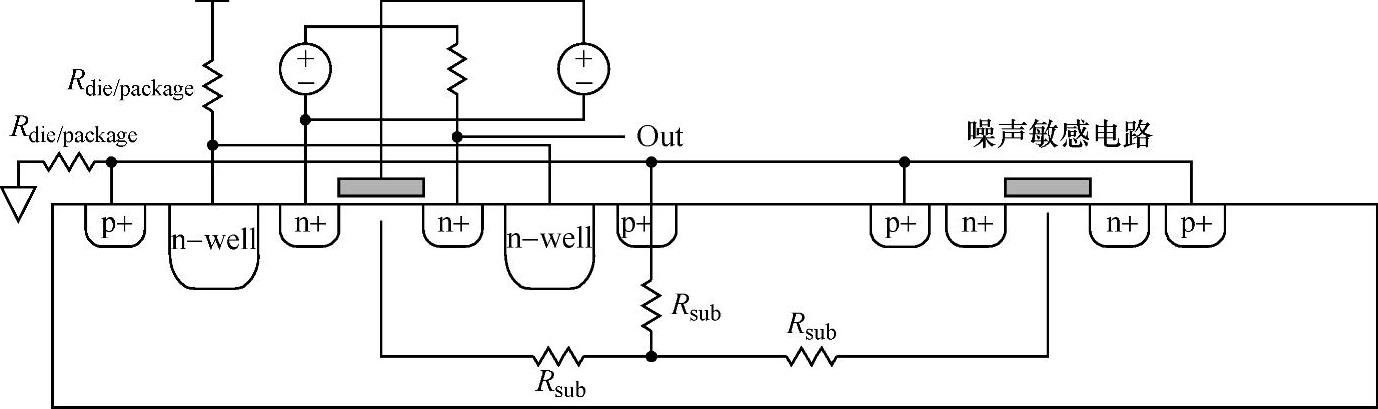

使用保护环的前提是衬底中能提供一种收集杂散载流子的方式,使它们不会到达电路的敏感部分引入不希望的噪声。设计保护环结构的关键因素之一是理解设计的对象和目标以及正确建模的能力。在许多实例中,因为对物理设计采用了不合适的模型可能导致不正确的结论。图4-23所示为一个可能的耦合模型的简化电路图。左边部分电路表示的是一个分别采用n阱和p+保护环与外部电源相连的噪声发生器电路。如果保护环路径上的电阻大于穿过衬底到达噪声敏感电路的路径上的电阻,噪声将耦合到敏感电路。同样,如果所有的保护环连在一起,电流可能会从其中一个保护环流出,通过另一个保护流进与该保护环相连的敏感电路。如果封装和芯片寄生参数中包括感抗,这种可能性将大大增加,因为感抗会极大的增加高频开关噪声的串联电阻。

图4-23 衬底耦合模型

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。