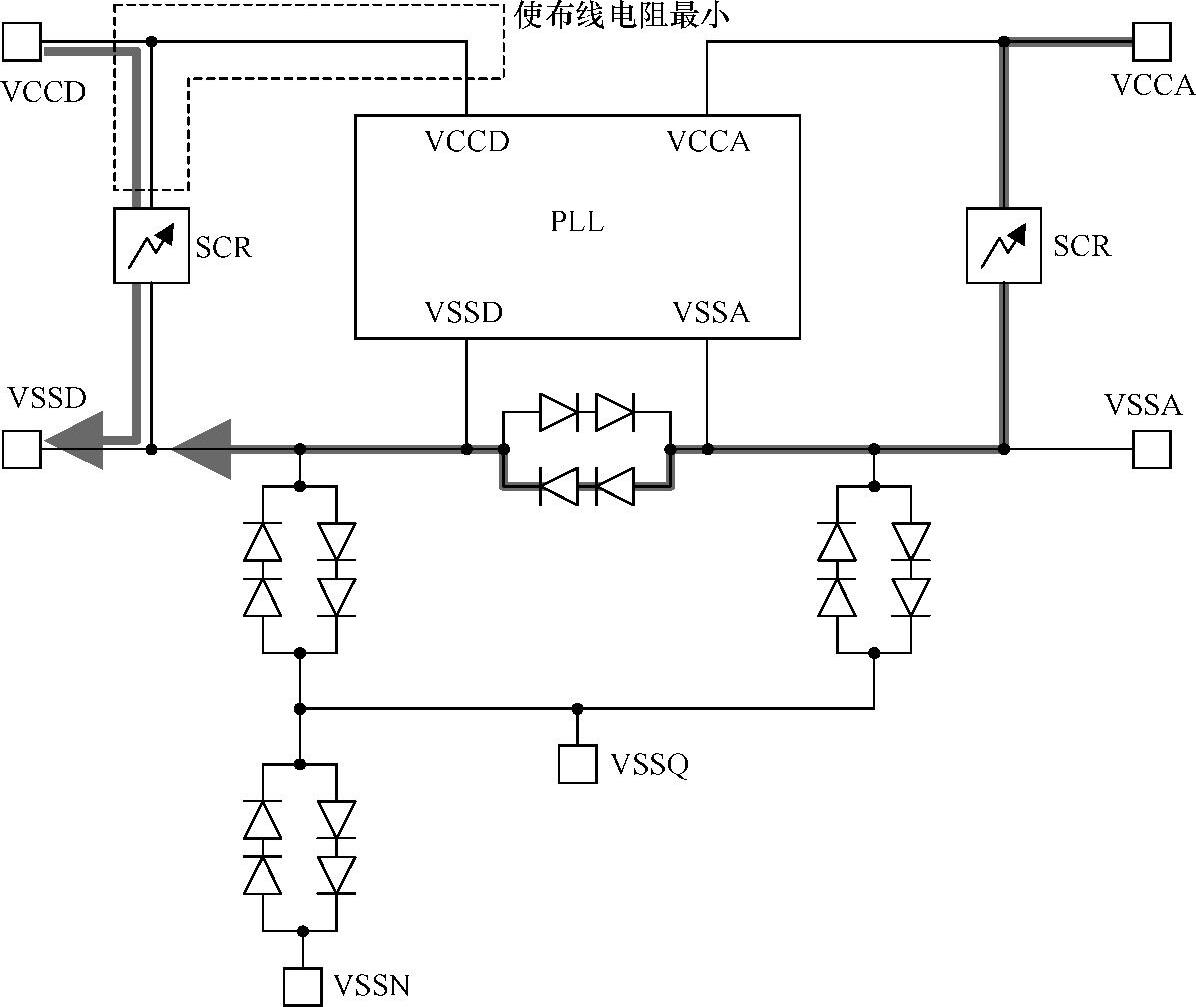

图4-21所示为一个针对芯片中使用多个地电平情况的保护方案实例。因为ESD作用可能在任意两个引脚之间发生,可以用背靠背二极管将各种接地连接在一起,给ESD泄放电流提供一条泄放路径。采用两个二极管可以减小各种接地之间的噪声耦合,在决定二极管尺寸和串联的二极管数目时,必须考虑这种耦合。必须确保在电路正常工作期间二极管从不正向导通,否则会使模拟电路的性能严重退化。图中作为实例,显示了几个ESD放电通路,表示ESD作用下不同元件的采用情况。

图4-21 基于较大数字IC构成的PLL的ESD保护配置

[该数字IC中I/O(VSSN)、核心电路(VSSQ)、PLL模拟(VSSA)和PLL数字(VSSD)等分别采用不同的接地]

为了适应先进的高性能微处理器的时钟频率,I/O信号频率不断增加。这就要求减小压焊点的寄生电容,但是对ESD保护器件的要求并没有免除。随着栅氧化层的减薄将导致ESD电容的减小,但是决不能因此而影响ESD保护水平。实际上,保护级别必须保持不变甚至更好。这对之前就已考虑这个问题的射频(RF)电路设计者来说已经不是什么新课题了,但是在具有高速外部I/O的混合和微处理器设计中,我们正经历同样的困难。关键问题是输入和输出引脚采用的ESD保护都不应该能影响芯片基本功能的所有性能。这意味着ESD结构的电容必须保持不变,与工作电压无关。如果不能实现这点,就会引起谐波失真,这将可能影响高速数据转换器、RF合成器、时钟数据恢复电路、或锁相环的性能。(https://www.xing528.com)

图4-22显示了用于保护高速和模拟输入的两种不同结构。因为二极管直接连接在高速引脚,可以使节点电容保持较小。虽然器件电容可以被保持到较小,但是因为金属互连和封装寄生,整个ESD电容会变得较大,这在任何时候都会给总节点电容增加200fF到1pF的电容。

图4-22 可以用来保护高速输入的各种ESD结构

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。