伴随着工艺的先进,集成电路设计的一个主要问题是要考虑版图设计前后的差异。当各个节点的总负载中互连寄生占主导地位时,这个问题就出现了。最初,互连效应被完全忽略(0.5μm和更大尺寸的工艺)。对较大的几何尺寸,虽然忽略了互连效应,但是电路仍然能正常运行,因为器件模型已包括了寄生效应。当几何尺寸持续缩小时,互连在电路节点总负载中所占的比例更大。在0.25μm工艺节点附近,设计者必须考虑互连的寄生效应以确保电路功能正常。不过,除了很长的信号线之外,互连的阻抗一般可以忽略。而在0.15μm工艺,即使对更局部的互连,寄生电阻也很重要而必须考虑。对90nm或更小的尺寸,必须提取全部寄生参数网表以确保电路功能,但是这要求在参数提取时必须保证电阻电容提取(RCE)的精确性。在处理版图设计前期、后期的问题时,可以采用下述3项基本技术:

(1)尝试在版图设计前期对所有问题进行建模,以缩小版图设计前期、后期的差异。

(2)不建立特殊模型;尽可能快的完成版图初步的设计,然后再对该版图进行优化

(3)使用历史数据进行版图设计前期的评价,以尽量满足设计目标。然后尽可能快地进行版图设计,再对设计的版图进行优化。

如果采用上述方法(1),版图设计前期的建模最耗费时间,并最容易出错,因为在设计的早期阶段就确定版图将是什么样子,即使不是不可能的话,有时也是很困难的。如果没有实际的版图,甚至没有一个布局规划,评估布线的寄生参数会变得很困难,除非这个单元很简单。采用方法(2)能够以最快的方式开始版图设计过程,但是最终的布局布线与开始进行的布局布线之间必然存在较大差别(对一个像压控振荡器这样的单元,产生的差别可能约为35%~45%)。这里最关键的问题是产生一个基本的设计,进而产生一个能供以后进行模拟的版图,但是在一个设计定案之前,需要反复进行提取版图网表的过程。其中困难之处在于处理版图产生的网表,而这种网表的可读性往往较差。因此,需要采用合适的方式建立电路层次,即主要是对多个较小的模块提取网表,从而使网表更易于管理。方法(3)其实就是方法(2)。只是在方法(3)中,前一代工艺中采用单元信息被作为一种通用的准则,以确定需要多少余量设计使设计满足规范要求。如果在0.13μm工艺中,已知一个给定的单元,如高速计数器,在版图设计前后差别为40%,这可以作为下一代工艺中关于可能发生变化的一般性准则。这种方式迅速,并且其精确度并不比花费大量时间试图在版图设计前对所有问题精确建模得到的结果差。(https://www.xing528.com)

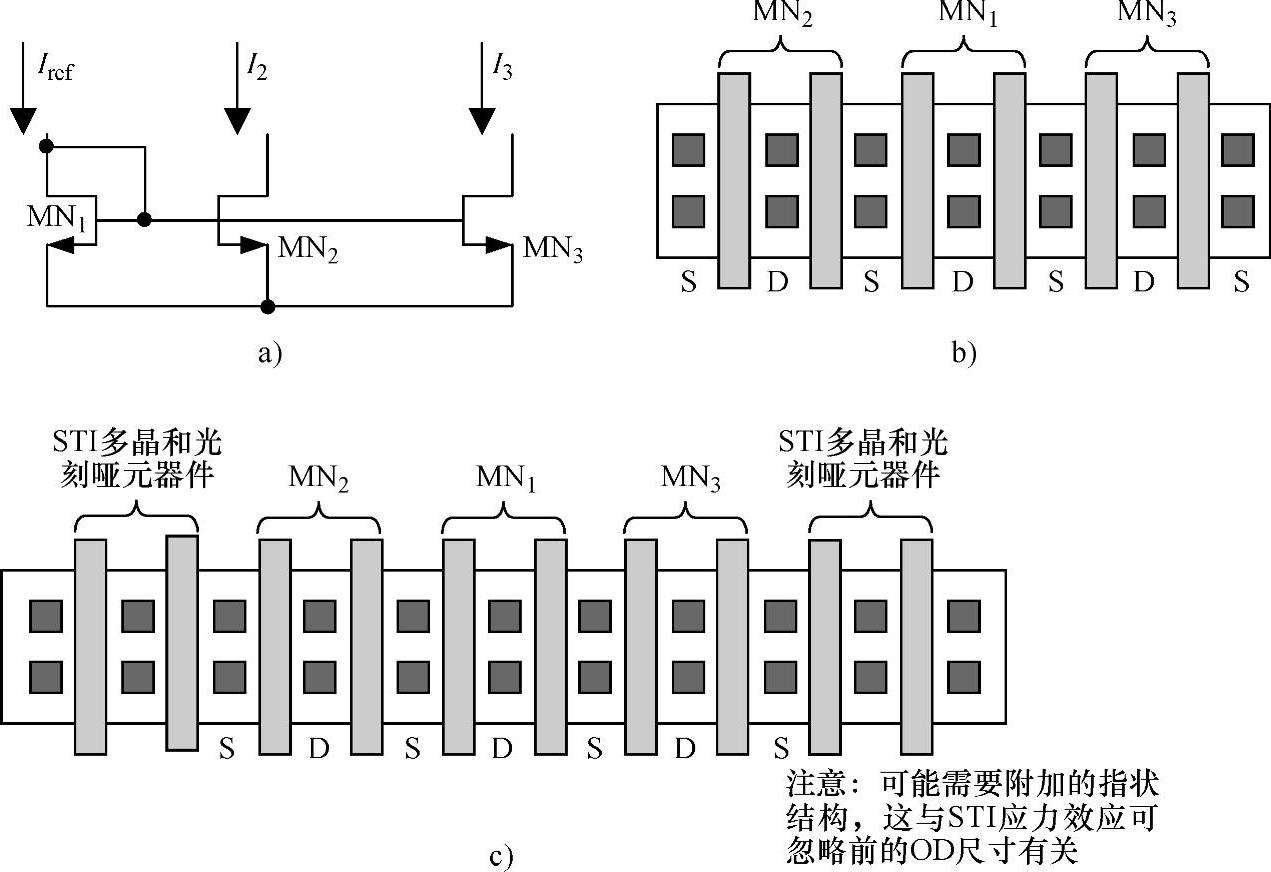

针对STI应力效应,可以采用几种处理方法。一种方法是把重点放在器件尺寸的调整,以保证与用来建立SPICE模型的器件版图相匹配。使用这种方法可以使应力效应的前仿真与后仿真之间的差异最小。第二种(可能更好的)方法是尝试在实际的版图之前准备一个初始的布局规划,从而在前仿真中就能包括这些效应,在实际版图完成之前获得OD参数。通过版图之前的布局规划,OD效应实际上可以用来增加如锁相环中的VCO或时钟恢复电路等关键电路的速度。至少它可以在版图之前考虑使用更精确的模型。因为版图对STI应力效应的影响很大,在版图开始之前必须对布局规划进行仔细的考虑。幸运的是,许多能够较好产生模拟版图的技术也能够自动产生与STI应力效应的良好匹配。图4-20所示为一个简单的电流镜及其两个可能的版图设计结果。图4-20b所示的版图在尺寸上更紧凑,但是从光刻的观点和STI应力效应的观点来看,它的匹配性较差。图4-20c所示版图采用哑元器件使STI应力效应最小化并且可以改善光刻和刻蚀问题,使匹配有了改善,但是占用的芯片面积较大。两个版图中并没有显示在器件的顶部和底部应该如何设计。一般在临近的单元之间增加保护环以保持单元两侧版图的连续性。

图4-20 a)简单的电流镜电路 b)芯片面积小,但是匹配差 c)采用哑元器件改善版图设计

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。