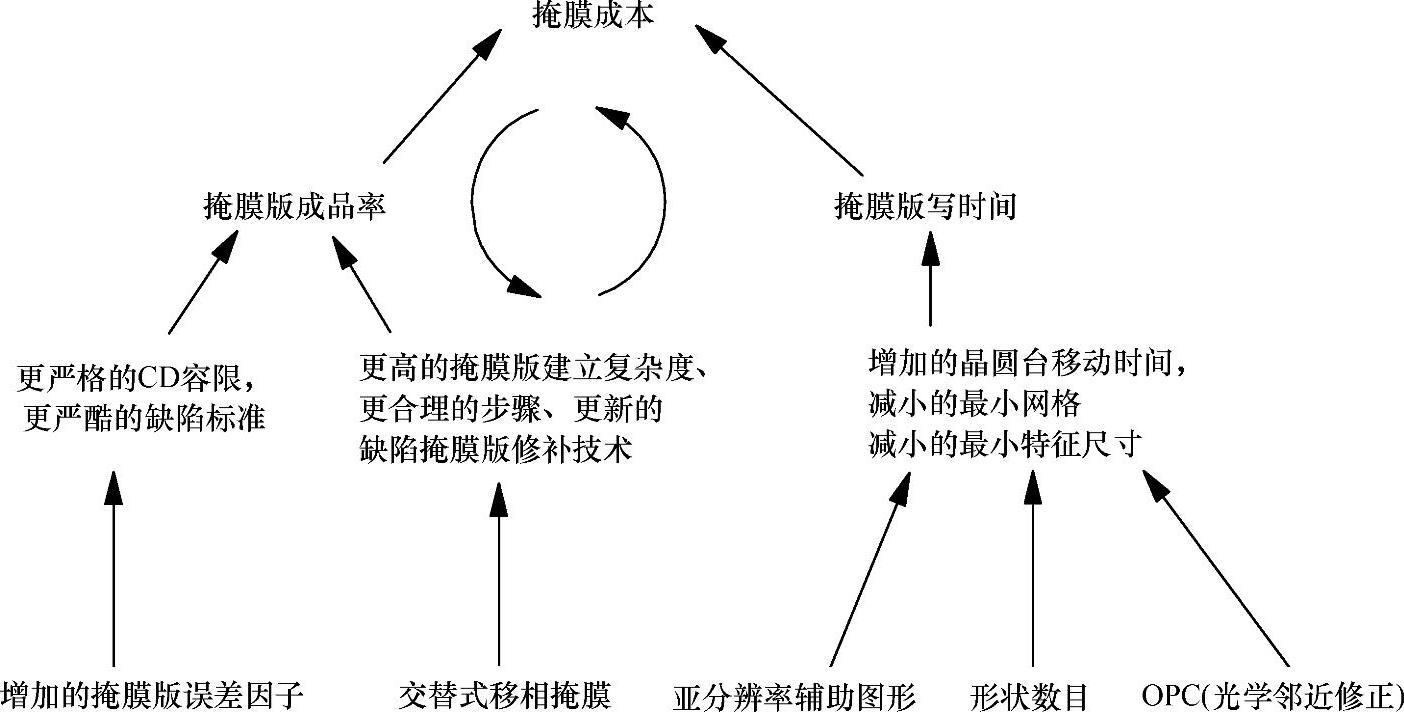

图3-34 RET与掩膜成本之间的关系[各种RET(交替式PSM、辅助图形等)影响掩膜成品率和制备掩膜的写时间,从而影响掩膜版成本]

早期的光刻,掩膜版的开销在芯片制造总成本中占的比例并不大。但是现在这一情况已经发生了巨大的变化;对90nm节点的产品,一组掩膜版的费用在一百万美元的级别[34]。掩膜费用是光刻工艺成本中增长最快的部分,超过了晶圆工序和曝光设备费用的百分比增长。对ASIC设计,由于只要加工为数不多的晶圆就能满足客户的需求,使得这一问题更加突出。由Sematech[36]对其成员公司完成的调查表明,一组掩膜版曝光的平均晶圆数,对逻辑ASIC来说大约是500片,而对DRAM生产,大约是8000片。基于业已报道的大量90nm技术节点ASIC设计数据,经过外推处理,结果表明,掩膜版开销已占到光刻总开销的60%[37]。

对低k成像的需求以及为此采用的RET是促使掩膜版成本增长的主要因素。驱使掩膜版成本增加的主要因素有两个:掩膜版制备过程中的写时间和掩膜成品率。这里所说的掩膜版成品率是包括最小缺陷标准和CD要求在内所有规范要求的掩膜版成品率。图3-34总结了由于使用低k成像和RET使得掩膜版成本增加的因素和机制。从底部开始,列出了向低k成像时代推进的各种因素。其中一部分因素是任何工艺缩放过程所通有的。每个掩膜版范围内图形数量的增加和更加密集的成像布局要求对各种基本规则的减小都是存在的,在此将其列出只是考虑到完整性。这两个因素都影响掩膜写时间。由更密集布局提出的精度要求,增加了载物台的移动次数,因此增加了写时间。增多的图形数量也增加了需要被写入的数据总量。因为先进的掩膜写工具是半导体工业加工设备中最昂贵的部分,而增长的掩膜写时间将增加掩膜开销。如3.2节所指出的,低k成像增大了掩膜误差增强因素(MaskErrorEnhancementFactors,MEEF)。因为CD容限随着工艺节点而缩放,掩膜对整体CD预算的贡献只有通过紧缩对掩膜CD的控制来维持。更严格的掩膜要求反过来又减小了掩膜成品率。

从缺陷的角度来看,掩膜制造者面临着两个挑战。在低k成像时代,对掩膜缺陷的敏感度增加了。另外,像交替式PSM这类掩膜的制备步骤有所增加,而增加的每个工艺步骤都会引入虽然不大但不可忽略的缺陷。此外,交替式PSM导致了较简单掩膜工艺中所没有的新类型缺陷(相位缺陷),并且通常很难修复。光学邻近修正以及亚分辨率辅助图形的使用均减小了最小特征尺寸,使得传递到掩膜写工具的数据量急剧增加,这样就急剧地增加了掩膜写时间。另外,较小的特征尺寸将使掩膜检查变得复杂。所有这些因素既增加了掩膜写时间,又降低了掩膜制备成品率,从而使掩膜成本上升。值得注意的是增加的掩膜写时间本身也将降低掩膜成品率,因为电子束曝光载物台的移动控制和稳定性要求将更加严格。(https://www.xing528.com)

面对掩膜成本飞涨的困境,新设计的开发能力日益成为业界的关注焦点。业已提出了几个概念和方式来解决或至少缓解日益上涨的掩膜成本问题。降低有效成本的较明显方式之一是多项目晶圆的概念[38]。芯片制造商通过将多个设计组合在一组掩膜上的方法降低了每个设计的掩膜成本。实际上,使用同一组掩膜版曝光的晶圆总数得到增加,基本等于对每个设计单独曝光的晶圆的总和。每一种设计分别通过一些必要的数据准备和OPC操作进行处理,在生成最终数据时再合并在一起。这就缓解了接收和处理多个设计时的时间安排问题。虽然多项目晶圆似乎是降低掩膜成本的理想方式,但是还有几个问题值得注意。实际上只有当不同设计对应的晶圆工艺步骤,包括所有的金属层,都完全一致时才有可能有效使用这种技术。否则,相当部分的晶圆将会无用,这就冲淡了这一技术的优点,也与采用这一技术的初衷背道而驰。如果每种芯片设计符合标准尺寸,则划片过程中使得完好芯片受到损失的数目降至最小,更加有利于这一技术的有效使用。

减小成本上升影响的另一个有效方式是将定制芯片改变为现场可编程门阵列(FPGA)、可编程ASIC、或在快速微处理器中通过软件实现一些需要采用互连实现的逻辑功能[39,40]。从芯片制造的角度来看,FPGA具有只需要使用一组掩膜版的完全标准化了的晶圆加工的优势。最终用户要求的功能被编程进了单个芯片。遗憾的是,与采用ASIC实现的电路相比,它们的面积仍然大一到两个数量级,并且功耗明显增大。

综合ASICs和FPGA的特点,有一种结构化的ASIC。对结构化ASIC,在芯片制造商那里,使用一组掩膜版完成整个晶圆加工的前道工序,包括有源区、栅、一次接触,甚至实现早期金属层的工艺加工。然后将晶圆贮存在生产线上以待进一步的处理。按照功能要求通过顶层的两层或三层金属层将芯片上的单个逻辑单元连接起来,最终实现芯片功能。这样每个设计就只要承担最后三层金属的掩膜费用,而其他层的费用则由不同芯片设计分摊。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。