交替式相移掩膜对物理版图有非常大的影响。可以使用交替式PSM的图形与不能使用交替式PSM的图形相比,工艺窗口改善是所有RET中最显著的。如果版图设计采用的是最小尺寸,绘制时必须采用相当大的倍数,但是却不能进行相移,则这种版图一般是严重影响成品率的图形。由于使用交替式相移掩膜增加了不能被相移的版图的“似然性”所带来的一系列新问题,使得这种非相移版图的严重问题进一步恶化。为了理解这些复杂性,下面首先分析与交替式相移掩膜相关的基本规则[31]。

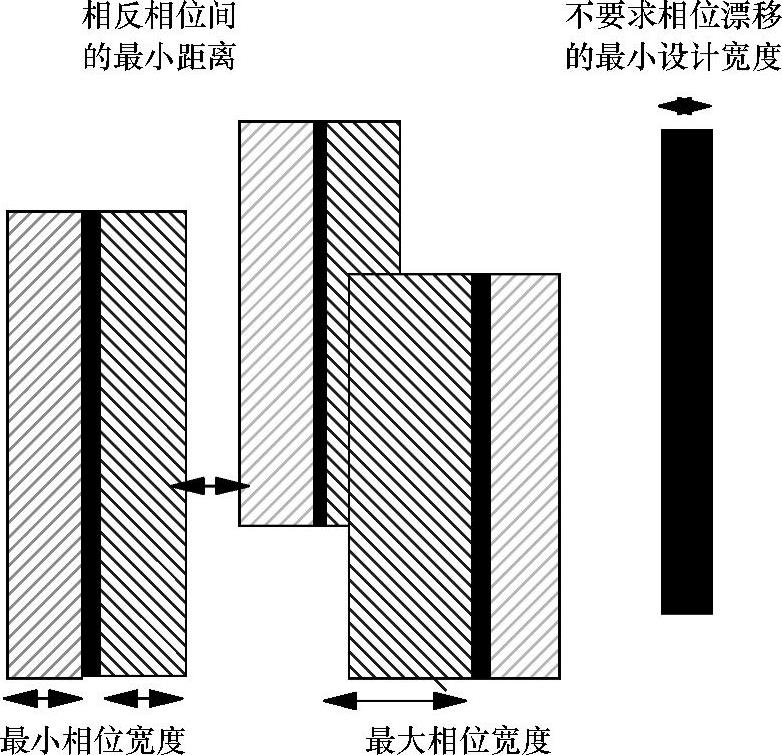

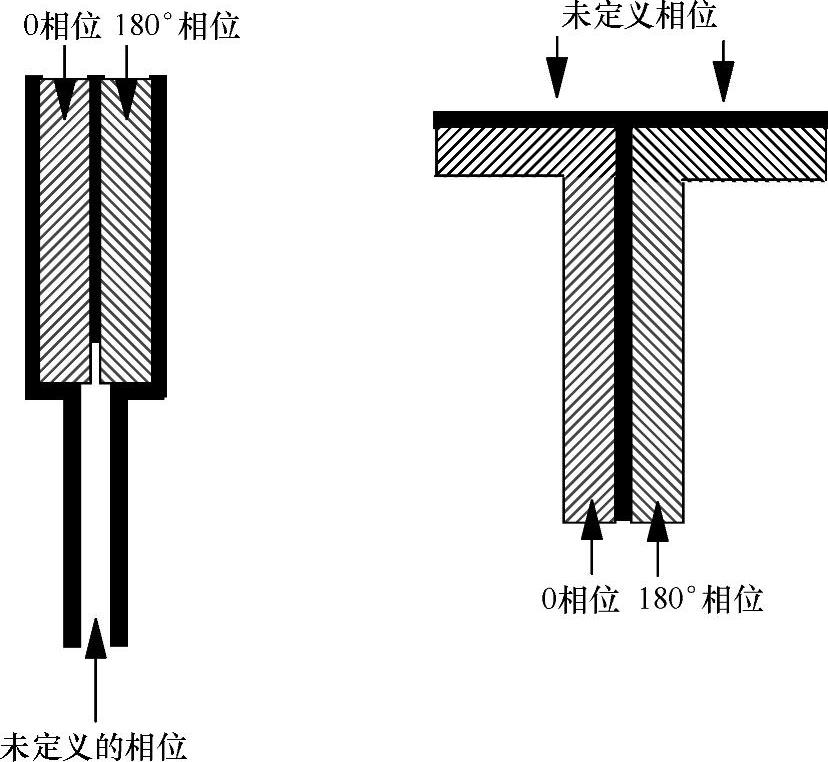

每个关键线条与两个相移区相邻,零相移区在线条一侧,180°相移区在另一侧。各种规则通常用于决定每个相移区的最小和最大宽度、以及两个不同相移图形之间的最小距离。仅在相位相同的区域之间允许交叠,因此只有在采用并列交叠排列的情况下才可能使放置密度最大。最简单的规则是考虑到掩膜制造工艺要求符号相反的相位之间距离最小。从工艺角度考虑,将决定允许的最大相位宽度以及不需要采用相移的最小线宽。图3-31说明了这些规则的基本设计含义。此外,还有一组规则用于防止在设计中使用了导致相位冲突的几何图形。相位分配是在设计中按照线性路径进行的。关键线条一侧的相位意味着该线条另一侧的相位相反。相位冲突是因为针对特殊间距安排的相位相互矛盾,这一情况与选择的是哪条路径到达相位区有关。导致相位冲突的两个常见版图实例如图3-32所示:关键T形连接以及奇偶路径情况(也称为“皮带扣”式版图)的一种图形。这

图3-31 交替式相移掩膜的基本版图情况(图中显示了交替式相移掩膜版图设计的基本规则,包括最小和最大移相区宽度、相反相移图形之间的最小距离及无需采用相移的最小线宽)

图3-32 导致相移冲突的版图情况:奇偶路径和T形连接

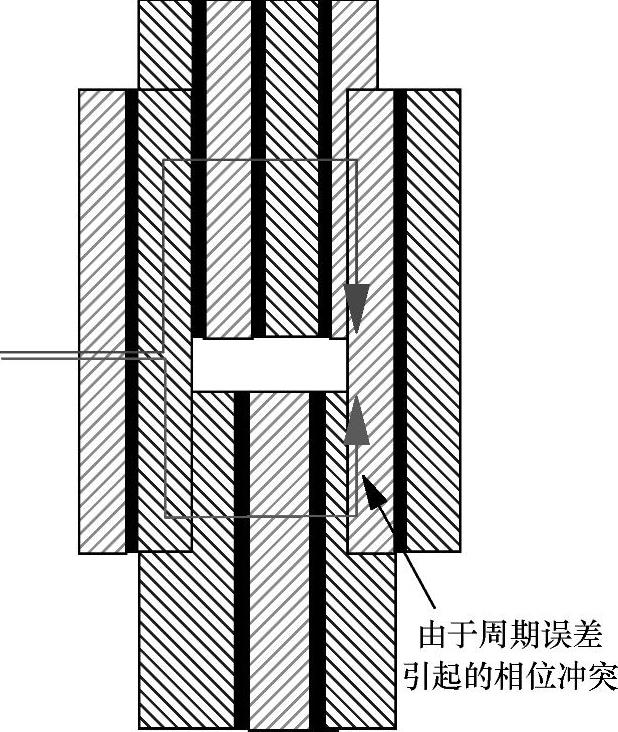

些版图仅仅是常见的设计误差的简单实例,又称为(圆)周期误差,这些误差与相移掩膜有关。图3-33所示为另一个实例。相位分配按顺序进行。在图3-33所示的版图实例中,在版图的不同位置,这些路径分开后又重新组合在一起。在路径分开的位置以及重新组合的位置之间,每条路径已经跨过的线条数目可能是偶数或奇数。如果一条路径上有偶数个相位转换,而另一条路径上有奇数个相位转换,则在路径重新组合的位置就不可能实现唯一的相位安排。这组失效着重说明了基本规则布线检查面临的重大挑战。由于误差能在相邻的图形之间被检查出,误差就不再是局部的了。(https://www.xing528.com)

图3-33 另一种错误的实例

(随着路线分岔并且最后又结合在一起,这些错误就产生了。上面一条路径穿过三根设计线条,而下面一条仅穿过两根。这些错误对设计规则检查提出了巨大的挑战,因为它们是非局部的)

与解决相位冲突相关的困难导致了设计和光刻工艺之间相互作用的典型转变[26]。先前的技术在设计空间和工艺空间之间有一个清晰的分隔,并且大部分情况下采用的RET对设计并没有影响。使用RET引起的限制和工艺关注表现为一组设计规则限制,与前面章节讨论的情况相似。相位冲突问题的复杂性驱使方法学上的变化。一种方案是把相移工具转移到设计团队手中,使他们具有检查相位分配的能力,甚至还可能检查预期的掩膜修剪形状。这样,确保交替式相移掩膜灵活性的责任就转移到设计团队手中。考虑到有时相当复杂的交替式相移规则框架,再结合标准的基本设计规则,误差的识别可能成为令人灰心的经历。需要指出的是,交替式相移规则不仅仅包括相位分配规则,还包括一些附加规则。例如,描述相反符号的相位形态之间的最小距离、相位形状交叠的规则、以及最小的修剪掩膜尺寸等等。因为这些参数可能非常特殊,它们不仅阻止了在不同制造厂之间的交流,而且也不能用于更先进的光刻方法。对ASIC设计方式来说,在两个层次上要求对相位的适应性。第一,单个库单元的版图必须具有相位适应性。一旦这个条件满足,当组合使用单个库单元时,还将出现更复杂的问题。为了避免这个相位误差,必须通过在单元边界周边提供足够大的缓冲区以保持单个单元相位不受外界影响。通过尝试寻求相对简单的单元边界特点,可以采用相对简单的并列交叠步骤将ASIC设计中成行排列的单元放在一起,就可以减缓这一需求。参考文献[33]对这种方式进行了讨论。

另一种替代方式是建立设计制约规则,可使得设计团队无需考虑相位分配的复杂性以及修剪掩膜版图,但是对传统的设计过程来说冲击则是明显的[26]。在这个方式中,有时也被称作粗网格方式,设计被局限在一个方向,并且接触节距只能采用整数倍的变化。这种框架避免了复杂的二维版图情况。这种方式有几个极具诱惑的优势。它对多种RET提供支持,解决了由二维情况引起的可制造性问题,并且当转移到新的技术节点时,能减少重新设计的需要。这种方式的主要挑战是保持面积紧缩到最小,并且为了实现栅极层次版图的简单化,应该尽量减小导致其他设计层次版图(例如局部互连层次)复杂性的增长。

如前所述,在光刻工序中更多地考虑k因子就会改变设计和数据过程之间的关系。在先前的技术节点,主要考虑生成最小尺寸的设计图形,包括互连、节距或面积,以及决定不同层次关系的一组规则,使覆盖容差不致导致芯片失效。由于100nm和70nm节点技术更加依赖RET,为了充分发挥新技术的作用,需要引入一组新的设计规则。图形方向的限制、从设计中清除特定间距范围的禁止区、以及线条图形长度的最小限制等方面的要求将日益严峻。交替式PSM将对物理版图有一个更加重要的影响。特别是栅极层次,由于对CD容限有严格要求,在这个领域处于领先位置,而其他层次也跟随其后,特别是在70nm节点。由于Foundry(代工厂)生产线存在巨大的竞争性压力,生产方将极不愿意把这些限制加到他们的客户身上。设计团队应该非常清醒地认识到,光学成像物理、曝光设备和RET的实行在业界已经相当标准化了。一个了解相关方面知识的客户(即对低k成像实施有清醒认识并且明确如何优化版图以充分发挥光刻RET效率的团队)将通过使设计更加适应工艺的波动而受益,因此更可能提高成品率。对设计团队来说,益处是显而易见的,光刻性能的重大改善将最有可能缩短产品上市时间。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。