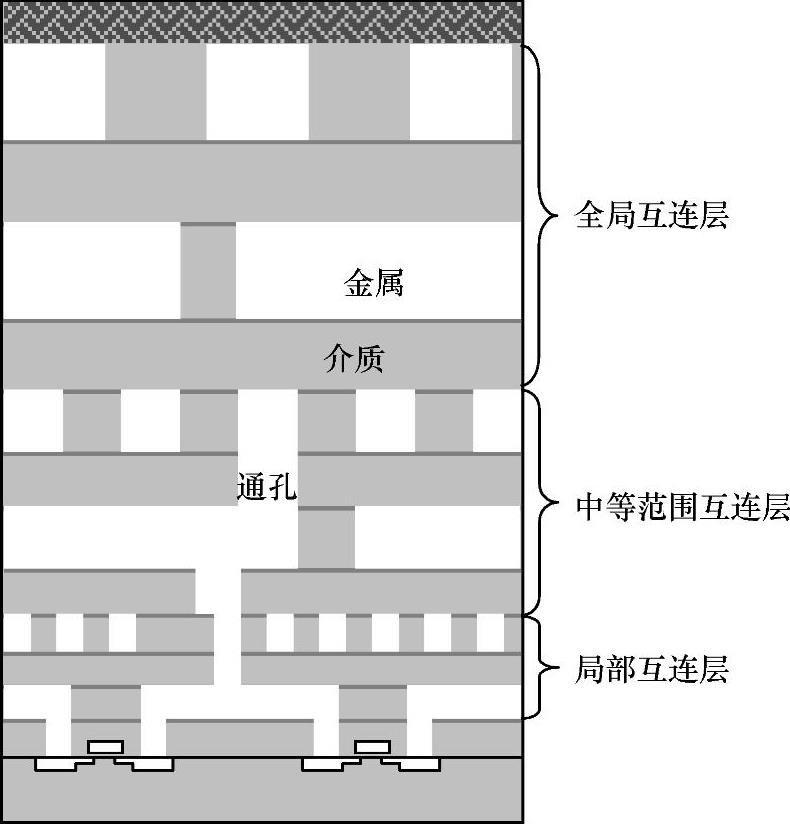

与FEOL缩放能提高电路性能相比,由于互连线横截面面积的快速减小,互连尺寸的缩小却会产生较长的时延。为了应对RC时延的增加,从几何结构和材料方面,已经采用了各种的改进。如图2-24所示,典型多层结构的特性包括:

●大纵横比(纵横比定义为互连的厚度与宽度之比)。因为金属到地的电容(Cg)约与线宽成比例,而金属阻抗(R)与横截面面积(线宽与线厚度的乘积)有关。当互连节距减小时,较大的纵横比可以实现较小的RC时延。这个趋势在全局互连中极受欢迎,而在局部互连时,较低的纵横比也是可以接受的,因为局部互连的连线较短,信号的路径时延对RC时延的增加不敏感。与高纵横比相关的两个问题需要加以注意。首先,要用金属完全填充一个深而窄的槽是很困难的。因此,纵横比大于4的互连和通孔的形成变得不可靠,特别是对于双镶嵌结构工艺。第二,对于较大的纵横比,互连线厚度的增加会导致与相邻互连之间产生较大的耦合电容(Cc),这会增加RC时延成分并且增加信号耦合噪声。这两个不希望的影响限制了未来技术换代中的这种缩放。

图2-24 90nm时多层互连结构的典型截面图(https://www.xing528.com)

●分层互连。在多层金属化中,缩减局部互连节距并增加其他互连层次中的厚度和宽度,可以满足更高的电路密度、减小的RC时延和更小的阻性损耗要求[83]。在过去的10年,可用的金属互连层数增加了3倍[84],目前工艺(约90~180nm)中有6~10层金属,图2-24为一个多层互连实例示意图。局部范围和中等范围互连一般用于连接功能块内部的门,而全局互连一般用于实现不同功能单元之间的互连。除了信号传输(如数据总线),宽而厚的全局互连也用于时钟和电源线,或构成片上螺旋电感。同一层上的金属互连一般是平行分布,而与相邻层次上的互连线走向垂直。最近,对于全局性互连,对角线走向互连的引入比传统的直角互连结构的路径时延减小了19.8%,并且线长减小29.3%[85]。然而,在以前,这个技术对数据库的大小、光学邻近修正和掩膜写时间都提出了很大的挑战。这些问题的解决是未来技术成为可能的关键;电子设计自动化(EDA)公司和掩膜制造公司正在努力工作,以实现对角线走向互连。

●局部和全局互连的不同缩小方式。为了与衬底上MOSFET的密度相匹配并维持RC时延,局部互连的节距与长度的缩小速度比垂直尺寸快得多。全局互连的缩小是由芯片边缘的长度决定的,其长度会随着栅尺寸的增大而增加。因此,全局互连的信号时延随着一代工艺到下一代工艺而增加,限制了整个芯片性能的提高(见图2-23)。为了支持高性能处理器性能改善要求的频率提升,需要采用补偿技术,如增加转发器和流水线全局信号。

●铜互连和低k介质。因为互连缩小是制约电路速度提高的主要瓶颈,业界做了很多的工作努力把新的BEOL材料整合到硅工艺中。两项主要的改进包括将金属材料铝改为铜、采用低k介质取代二氧化硅层。这些方式不仅有效地减小了单位长度互连的RC寄生参数,而且有助于改善BEOL的电迁移可靠性。另一方面,对互连最困难的挑战包括工艺集成、互连尺寸控制和电气可靠性。当工艺进入纳米时代,即使是低k铜,对于希望未来全局信号更快的要求来说也是不够的[85]。为了持续这种成功,新的BEOL技术包括材料和结构都是必需的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。