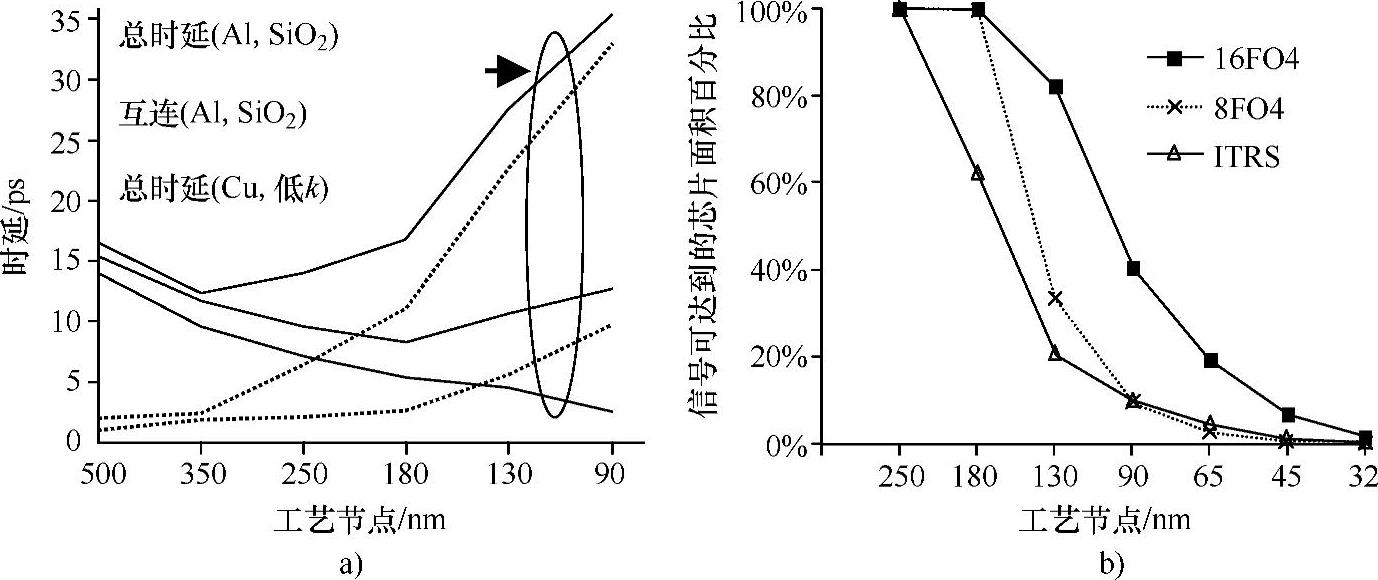

【摘要】:在350nm工艺之前,互连技术的发展在不断改善集成电路密度、性能和每项功能成本方面起着关键的作用。受性能改善的驱使,互连线缩小的连续进展导致了线条更厚、更窄、线间距减小、单位长度阻抗更低和电路工作频率更快。如图2-23a图2-23 工艺缩小对芯片性能的影响:a)铝与铜中的互连线和栅时延 b)一个时钟周期信号可达到的面积百分比所示,在130nm及更小时,即使是采用铜互连后道工艺,互连线时延会超过门时延。

在350nm工艺之前,互连技术的发展在不断改善集成电路密度、性能和每项功能成本方面起着关键的作用。受性能改善的驱使,互连线缩小的连续进展导致了线条更厚、更窄、线间距减小、单位长度阻抗更低和电路工作频率更快。多层互连及低k介质提供了比先前铝互连线工艺更快的电路速度、减小的信号干扰和更好的可靠性等优势。然而,后道工艺(BEOL)的关注仍然是电迁移、热特性、工艺控制、多层整合和在未来片上系统(SoC)中最重要的高速全局信号等几个关键问题。在纳米时代,互连线时延已经是总时延的主要部分。如图2-23a

图2-23 工艺缩小对芯片性能的影响:(总时延中占主要成分的互连线时延)(https://www.xing528.com)

a)铝与铜中的互连线和栅时延 b)一个时钟周期信号可达到的面积百分比

所示,在130nm及更小时,即使是采用铜互连后道工艺,互连线时延会超过门时延。对90nm工艺,互连时延大约占总时延的75%[1]。而且,由于芯片功能的不断增加,单个芯片的面积随着工艺的减小而增大,因而如图2-23b[83]中所示,在一个周期内将信号送到芯片的各个部分变得越来越困难。为实现频率提升,全局性信号需要采用流水线传递,当信号通路跨越功能模块时,将导致较高的等待时间和功率消耗。由于这些缩放效应,所有电路性能优化的重点就要从门级逻辑设计变成以互连为中心的设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。