器件的可靠性是CMOS工艺需要考虑的关键问题。更小的器件尺寸和新材料的使用,如铜/低k介质、高k栅介质和金属栅电极,都对CMOS器件可靠性有着重要的影响。集成规模不断增大对电路中的每个单元提出了更加严格的可靠性要求。测试低失效率复杂电路的开销和时间也是一个严重的挑战。下面简要分析与前道工艺相关的CMOS可靠性问题。

经时介质击穿 在过去的几十年,SiO2经时介质击穿(TDDB)的机制一直是一个非常活跃的研究领域,但是尚未得到一个毫无疑义的结论。随着工作电压和栅氧厚度的缩小,新的失效模式如软击穿也变得重要了。最近几年,一个重要的主题就是建立一个通过高压和高温加速寿命实验预测低压工作寿命的正确流程。一个相关的问题是:对于SiO2栅介质缩小的可靠性限制是什么?一些研究者相信随着微观和宏观栅氧均匀性的改善,SiO2栅介质可以缩小到20Å以下,这与最近的制造实践结果一致。Weir等人的一项研究结果证实,1.2V、70℃时16Å的氧化层是可能的[78]。基于目前的认识和ITRS提出的栅泄漏要求,SiO2的缩小可能被直接隧穿泄漏限制,而不是TDDB可靠性。

关于高k介质的TDDB可靠性的研究远少于关于SiO2的研究。一般地,许多高k介质都有更小的禁带宽度与更高的界面和体陷阱密度,这对它们的TDDB可靠性有不好的影响。现在已经有一些基于氟的栅介质的研究,这种介质被认为是最有前途的栅介质候选者。一些技术,如衬底和高k介质的氮化,表现出可以改善HfO2栅介质的击穿电压[79]。然而,高k介质其他不希望的效应,如迁移率衰退,是影响它被采用的主要因素。

热载流子效应 MOSFET在正常工作时,高的横向电场会在漏附近产生热载流子,这将损伤栅介质并引起器件特性的衰退,如gm衰退和Vth漂移。随着沟道长度的减小,对于给定的电源电压,沟道中峰值电场将增加。电源电压的降低将减轻这个问题。调整掺杂分布也可以改善热载流子可靠性。在现代CMOS技术下,电源电压可以减小到接近于1V,因此热载流子的能量将小于热发射和碰撞电离所需的最小能量。然而,在电源电压减小到这些关键能量水平以下时,并没有观察到载流子衰退的突然变化[80]。另外一些热载流子衰退机制被提出以解释这些实验观察结果。虽然在实际应用中,热载流子不是工艺缩小的阻碍,但是热载流子可靠性将仍然是需要给以适当关注的议题。

负偏压温度不稳定性 负偏压温度不稳定性(NBTI)是p-MOSFET中阈值电压漂移的重要原因。在NBTI应力下,源、漏和衬底接地,而栅被偏置到一个负的应力电压。在高温时,这样一个偏置将增加栅氧中正电荷的产生和界面态的产生。因此,导致gm衰退和Vth漂移。在一些模拟和混合信号应用中,需要阈值电压极度稳定。NBTI是这类电路寿命的限制因素。Reddy等人的研究报告报道了NBTI对现代数字电路的影响[81],结果表明,静态CMOS工作时主要的衰退模式是p-MOSFET NBTI。当工作频率下降时,受NBTI应力作用,环形振荡器的相对频率衰退增加。另外还发现,NBTI应力导致了SRAM静态噪声裕量退化。可以预计,随着工艺的缩小,NBTI对电路的影响日益重要。(https://www.xing528.com)

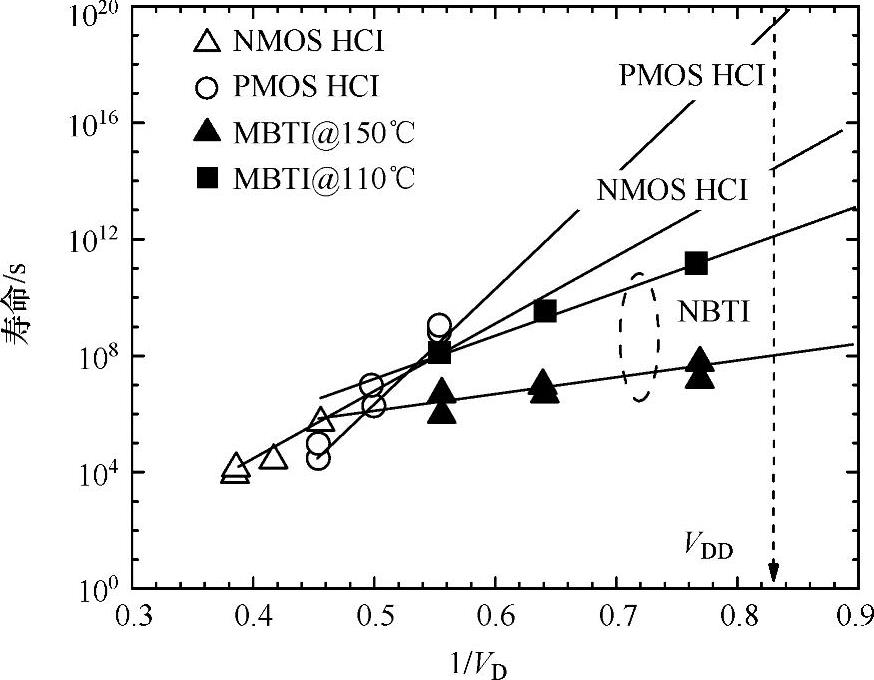

最近一项研究显示,按照Vth的漂移量达到一定值来定义寿命时,采用超薄氮化栅氧的p-MOSFET的寿命将主要由NBTI限制。在现代CMOS技术中,广泛使用氮化栅氧技术抑制硼穿通。然而,观察表明,氮化将减小p-MOSFET的NB-TI寿命。在Jeon等人的研究中[82],使用氮化栅氧厚度为13Å的0.13μm CMOS工艺制造MOSFET。图2-22所示为在NBTI应力、HCI应力下的p-MOS和在HCI应力下的n-MOS的寿命。由图可见,对p-MOS,NBTI应力下的寿命比HCI应力下的寿命低几个数量级,因此NBTI成为电路寿命的限制因素。将应力温度从110℃升到150℃,NBTI寿命将更短。对于一些待选的高k介质,仅有非常有限的数据可以使用,并且对于电路级的广泛研究也很缺乏。可以看到,对当前和未来的CMOS技术,NBTI可靠性对于器件技术和电路设计都是非常重要的议题。

图2-22 热载流子应力寿命和0.13μm CMOS技术中PMOS NBTI应力寿命

(在正常的Vdd值下,n-MOS和p-MOS的HCI寿命远长于NBTI应力下PMOS的寿命)(来源于参考文献[82])

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。