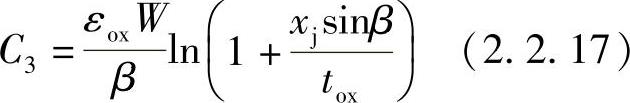

栅与源/漏之间的电容是影响CMOS器件和电路性能的重要因素。栅和源-漏之间的耦合,一部分由于直接交叠产生,其不能随着普通工艺技术的缩小而成比例的缩小。因此,对于更短栅长的器件,寄生电容变得更加严重。隔离层介质材料影响着边缘电容。另外,用高k栅介质取代SiO2栅氧化层也影响着寄生分量。虽然非常准确地计算电容要求二维数值计算,但是一个简单的物理模型可以被用来理解这些机制[75]。如图2-18中三个箭头所示,栅到漏(或源)电容包含了三个耦合途径:两个边缘分量和栅到漏的直接交叠。侧墙区两侧的边缘电容为

式中,W是器件的宽度;tG和tox分别是栅介质和栅的物理厚度;α是如图2-18中所示的角度;εSPCR是隔离层介质的介电常数。

直接交叠电容等于

式中,d是交叠长度;当α是π/2时,Δ是零。结侧面的耦合电容等于

式中,β=πεox/2εSi。注意,当栅下存在自由载流子时,耦合途径将被屏蔽,因此在强反型时,这部分不存在。在上面几个表达式中,所有的介电常数值的单位是F·cm。

图2-18 MOSFET的栅与漏之间耦合路径简图(三个耦合路径均用箭号标出,器件宽度方向与纸面垂直)(来源于参考文献[75])

C1与器件宽度和侧墙介质的介电常数有着线性关系,而与栅和栅氧之间厚度之比的关系较弱。假定α=π/2,εSPCR=3.9ε0(SiO2),tox=12Å,Xg=1000Å,可以得到C1=0.097fF/μm。更厚的物理栅介质可以稍稍减小C1。如果使用高k介质,使得tox=48Å(EOT仍然是12Å),而其他一切都与上面例子中的一样,C1只减小到0.068fF/μm。C1减小的关键是确保侧墙介质有较低的介电常数。如果用氮化物侧墙取代SiO2,由于εSiN≈2εSiO2,边缘电容将增加到大约为原来的2倍。如果在栅介质刻蚀期间,高k介质不能从侧墙区的底部完全清除,C1也会显著增加。

直接交叠电容C2随着栅沟道电容Cox缩小而线性缩小,其主要变量是交叠长度d。希望d尽量小,因为这样可以减小交叠电容。然而,结果显示,为了避免短沟MOSFET中驱动电流的衰退,d必须为15~20nm[76]。如果源漏扩展(SDE)深度或SDE到栅的交叠太小,会增加沟道的串联阻抗,引起漏电流衰退。图2-19显示了减小Miller电容(CM=C1+C2)和改善驱动电流Id sat之间的折衷。为了避免驱动电流衰退,要求交叠不能小于一个最小值意味着随着器件的缩小,交叠电容相对于栅电容Cox将变得更大。假定栅介质EOT=12Å,最小交叠为15nm,会有0.43fF/μm,而对于60nm的沟道长度,栅沟道电容是1.73fF/μm。

寄生电容的另一个来源是源漏结电容。p-n结存在耗尽区。当结偏置电压改变时,耗尽宽度随之变化,从而对电容负载产生影响。在MOSFET中,这些结的一侧一般都是重掺杂,因此耗尽宽度主要由轻掺杂一侧决定:

(https://www.xing528.com)

(https://www.xing528.com)

式中,XD是耗尽层宽度;Nsub是衬底掺杂浓度;VR是结上的反偏电压;ϕbi是p-n结内建电势。式(2.2.18)给出的是单位面积结电容。为了使总电容最小,保持结区下衬底掺杂浓度尽可能低就显得非常重要。另外,电路版图中结面积也应该尽量小。

图2-19 对给定的工艺,侧墙偏移尺寸对Miller电容

(交叠电容加边缘电容)与饱和漏电流的影响[76](实验表明,用来控制SDE注入与栅边界之间距离的侧墙偏移尺寸为0~40nm,使得SDE到栅的交叠

可以在40~0nm范围调节。当交叠长度低于15~20nm的最小值时,漏电流就会发生退化)

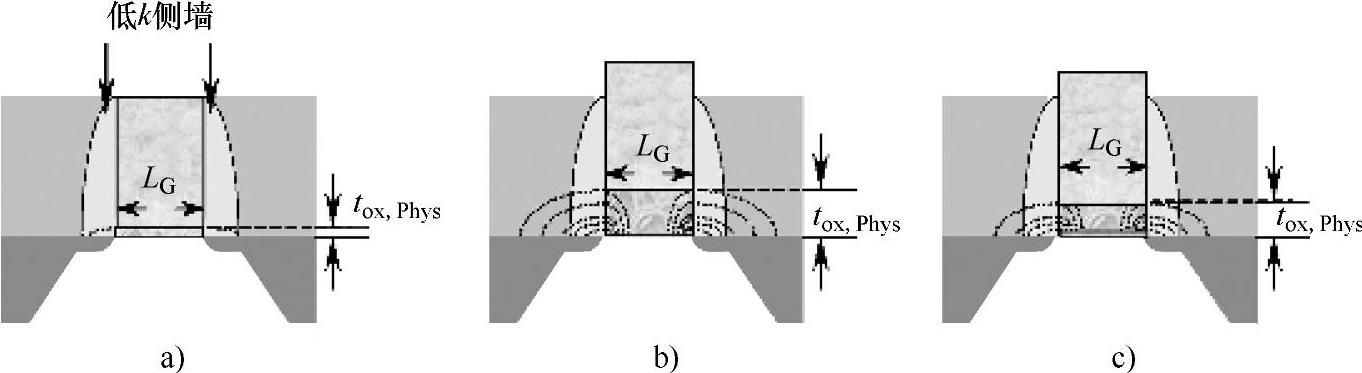

图2-20 3种情况下Vth的漂移特性

(对于给定的EOT值,单层高k介质(图b)的物理厚度比SiO2(图a)更大,一个更现实的栅介质结构是在一个薄的低k(如SiO2)界面层上加一层高k介质(图c)。对超薄SiO2来说,源-漏与沟道之间的边缘电场是可以忽略的,而使用高k介质的情况,边缘电场增强)

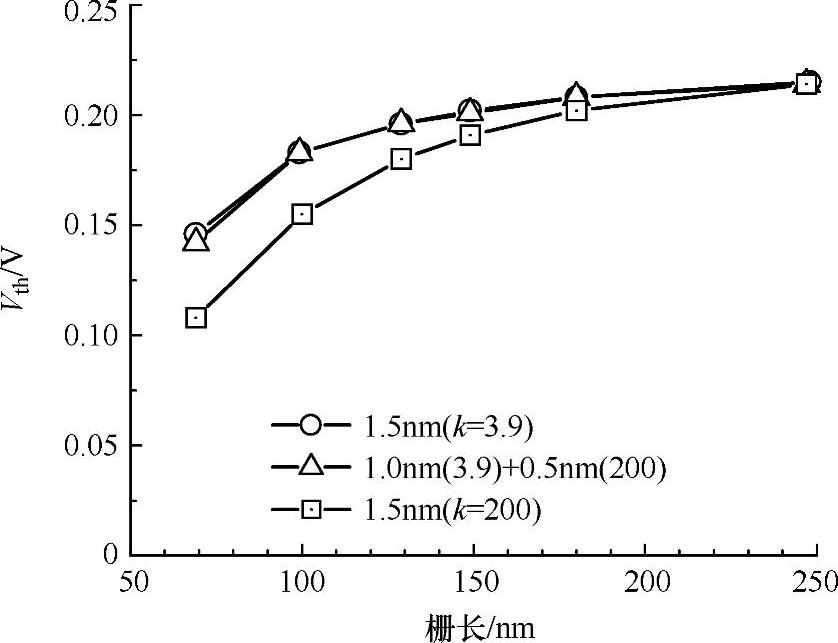

高k栅介质会增加一个附加的耦合通道,而这在SiO2中不重要。如图2-20b所示,当栅介质的介电常数很高时,为了得到给定的EOT,它的物理厚度会远大于相应的SiO2的厚度。漏和源的边缘电场通过厚栅介质的侧面影响着沟道。附加的耦合使短沟器件特性衰退。通过仿真对比了图2-20所示3种情况下Vth的漂移特性。对于相同的EOT,图2-20中栅介质分别设定为:图2-20a是SiO2;图2-20b是高k介质;而图2-20c是在一个分界层上有高k介质[77]。假定器件的参数相同,1.5nm的EOT可以采用1.5nm的SiO2,也可以采用k=200的介质,或者是在1.0nm的SiO2上采用k=200且EOT=0.5nm的介质来实现。图2-21所示为阈值电压与栅长的函数关系。由图可见,当使用k值非常高的单层介质时,Vth的漂移特性衰退很严重。而采用低k值的薄分界层可以有效避免这种不希望的作用。仿真结果也表明,即使EOT不同,如果物理tox与栅长之比相同,也会产生相同量的短沟性能退化。应该注意到,当前最有希望的高k介质也比仿真中假定的k值要低得多。因此,除非栅长变得小于40~50nm使tox/LG将变得足够大,否则这个效应不是很重要。总之,从短沟道效应的角度考虑,即使非常高的k值很有用,但是也是不希望的。

图2-21 阈值电压与栅长的函数关系

(图2-20所示的EOT均为1.5nm的三个栅层叠结构的Vth偏移特性。对于高k值单层栅介质,由于栅介质侧面增强了漏-源与沟道之间的耦合,Vth发生了明显的衰退。采用薄的低k界面层可以有效地防止退化)

从器件的角度看,使用高k介质的唯一好处就是减少直接隧穿栅电流。目前,高k介质存在大量的器件和工艺问题,例如迁移率衰退、平带电压漂移等。不管可制造的高k方案的可用性,功耗问题必须通过多个领域的前沿技术来解决,包括从器件和工艺到电路和系统设计。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。