图2-16 a)一般情况下,建立穿过薄栅氧的直接栅隧穿电流模型需要三个分量。在低栅压下, b)对n-FET主要贡献是ECB隧穿, c)对p-FET主要贡献是HVB隧穿(来源于参考文献[71]和[72])

对超薄栅氧,即使在低栅压下,由于直接隧穿过程,会有相当的栅泄漏电流存在。随着器件的缩小,考虑功耗问题时,栅泄漏电流就变成了日益严重的问题。在65nm工艺中,EOT接近1nm,要求栅泄漏电流比1nm SiO2泄漏电流小几个数量级(随着应用对象的不同有所不同)。因此,作为SiO2栅氧的替代物,高k栅介质的研究正紧锣密鼓地进行。

在低于20Å的情况下,常规的硅热氧化物不能再作为电子和空穴的有效势垒,因而会引起了不可接受的高栅泄漏电流。不像Fowler-Nordheim隧穿机制那样,对于直接隧穿电流没有一个简单的解析方程。另外,沟道载流子的量子制约效应在计算沟道电流时不能被忽略。因此,隧穿电流的严格的物理模型包括自洽求解薛定锷方程和泊松方程以及计算不同量子态下载流子的分布[70]。另一方面,一个相对简单的解析模型,对于电路仿真和栅泄漏的快速估算非常有用。Lee等人提出了一个半经验的SiO2直接隧穿模型[71]。一般情况下,需要采用下述三个直接隧穿分量组成总的栅泄漏电流模型:电子导带(ECB)隧穿、空穴价带(HVB)隧穿和电子价带(EVB)隧穿(见图2-16)。随着偏置条件的不同,一些机制可以被忽略。例如,当氧化层电压Vox小于硅带隙电压1.12V时,不会发生EVB隧穿。在低VG(<1.5V)情况下,对于n-FET,反型偏置栅泄漏主要分量由ECB贡献,而对p-FET时,则是HVB。

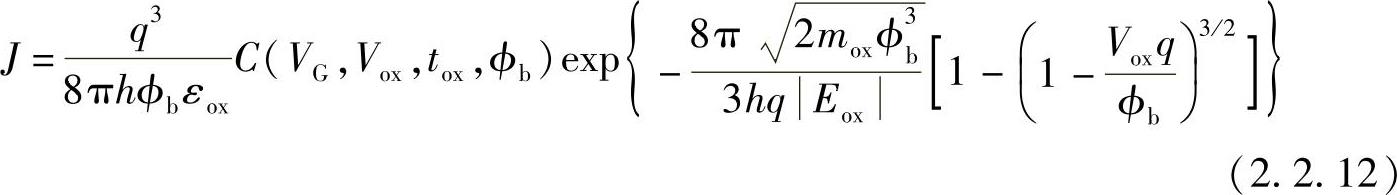

对每种隧穿机制,直接隧穿电流可以由下式表示:

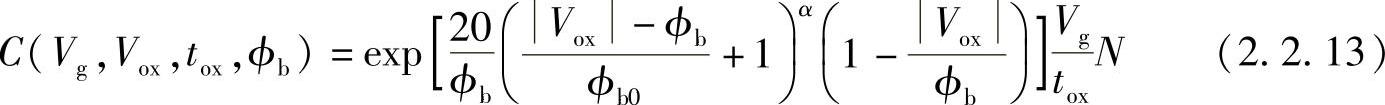

式中,指数项代表在导带边界载流子隧穿概率的WKB近似,而C基本上是为了在低栅压范围能正确描述的Jg-Vg变化关系的经验形状因子。

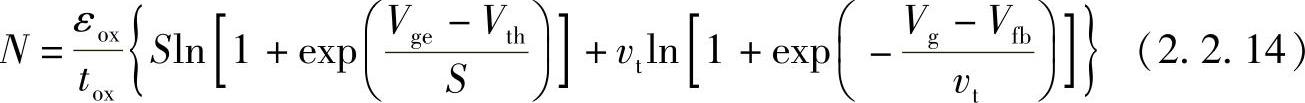

式(2.2.13)中的N与隧穿载流子密度相关。对反型区和积累区,N的一般表达形式为(https://www.xing528.com)

在式(2.2.14)中,S是亚阈值摆幅;vt是热电压;Vth是MOSFET的阈值电压。

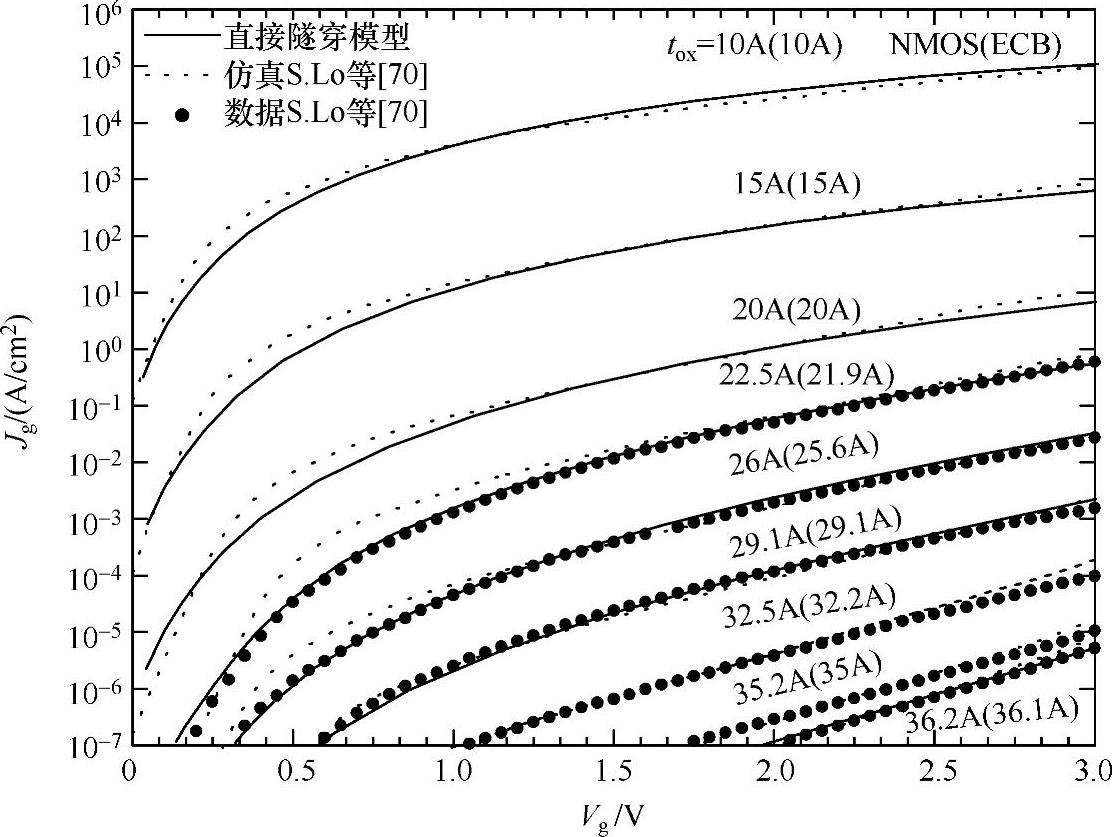

图2-17 Lee与Hu[71]的直接隧穿模型与实验数据以及仿真结果符合得很好

该模型中的拟合参数是有效质量mox、势垒高度ϕb和ϕb0以及α。对不同的栅偏置和栅与衬底掺杂类型,选用合适的参数都会使模型与隧穿电流符合。对于上述隧穿的每个分量,模型参数是不同的。图2-17所示为该模型的精度。图中虚线是数值仿真的结果[70]、实线表示解析模型计算结果,而实心点符号是实际器件的测量数据。可以看到三种结果之间符合得很好。除了SiO2,上述模型也在单层非SiO2介质应用中得到证明[72]。业已表明,对于采用喷射汽相淀积(JetVapor Deposited,JVD)技术生长的氮化硅,直接隧穿泄漏也可以与使用单独一组拟合参数的这个模型符合得很好。表2-1总结了在使用SiO2和JVD氮化硅栅介质的n-和p-FET中主要隧穿机制的参数。势垒高度可以通过其他方式获得,因此,实际上仅仅有效质量和α需要通过实验栅泄漏数据确定。为了更适合于有效的数值实现,这个模型的概念经过适当修改,被包括到BSIM4栅泄漏模型中[73]。

表2-1 SiO2和JVD氮化硅栅介质的直接隧穿模型参数

应该注意到,使用一些高k栅介质时,在高k栅介质和硅衬底之间存在一个薄界面层,这既可以是为了获得更好的薄膜质量而有意引入的,也可能是在高k层和衬底之间由不希望的化学反应生成的。因此栅绝缘层实际上包括了两个或者更多层不同的介质。由于上述模型是基于单层的概念,并不能被应用到多层介质结构。最近的一项工作将BSIM4中的单层隧穿模型拓展到了多层情况下[74]。结果表明,通过对多层中的每一层构建合适的用BSIM模型里隧穿参数表示的隧穿概率,BSIM直接隧穿模型也与多层栅介质的实验数据符合得很好。目前,对于明确知道层结构的多层隧穿的实验栅泄漏数据非常有限。随着高k栅介质工艺技术的进一步改进,模型也需要进一步提炼。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。