多晶硅栅耗尽问题在几代工艺中都是制约器件性能改善的瓶颈。如前面讨论所指出的,多晶硅栅不能符合最新的ITRS要求,使用金属栅电极将是解决这一问题的方案。通常金属栅比金属硅化物多晶硅栅有更低的栅阻抗,这将有助于减小RC时延,这是采用金属栅的又一个好处。

使用金属栅电极对工艺和集成提出了许多挑战。从器件和设计的角度看,栅的功函数是主要的关注点。沟道掺杂适当时,使用n+/p+多晶硅电极可以很容易地获得合适的n-和p-MOSFET阈值电压。对于体硅CMOS,使用金属栅很难满足同样大小栅功函数的要求。一般地,功函数高(类似P+Si-)的金属是非活性的,因此很难刻蚀掉,而那些功函数低的金属又活性太高,与栅介质接触时会带来热稳定性问题。在体硅CMOS中使用功函数大小适中的金属时,将导致n-和p-MOSFET的阈值电压大大高于希望值。但是,还是可以在两种类型的器件中使用同一种金属,然后分别调整两种类型器件上的金属功函数以优化这两类器件的阈值电压。当前,一种可接受的金属栅方案仍在研究中。除了获得合适的功函数,功函数分布的严格控制也是金属栅技术中非常重要的问题。

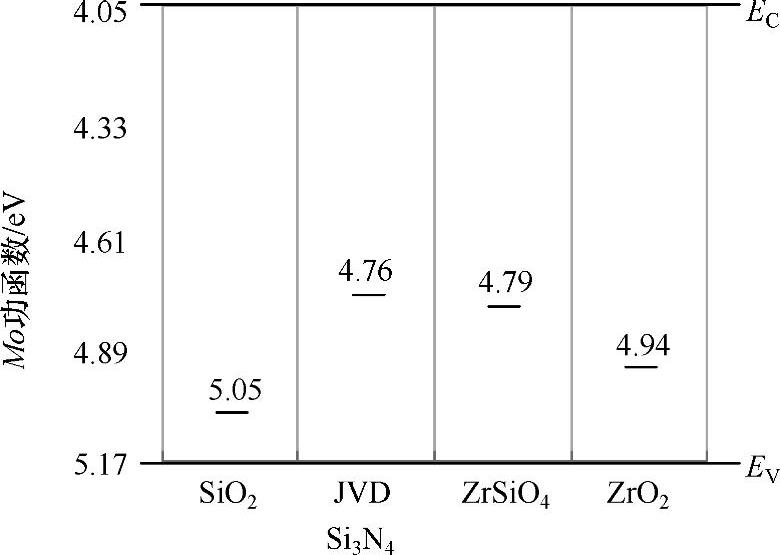

高k栅介质的使用影响着阈值电压的精确设定。许多高k介质具有高界面陷阱密度和固定电荷,这将引起显著的Vth漂移和较大的Vth变化。另外,当高k栅介质与金属栅一起使用时,将发生一项重要的物理效应。首先通过实验观测到,当使用不同栅介质时,p-MOSFET的钼栅会有不同的栅功函数值(见图2-15)。这可以用这些介质的界面偶极子具有不同的屏蔽效应来解释[68]。多晶硅栅很少受这种效应的影响,因为在禁带宽度中的能带密度可以忽略。理论模型预测,在高k介质上实现与n+/p+硅类似的功函数,需要金属功函数有非常大的范围,这给候选的金属电极施加了一个更加严格的限制。

(https://www.xing528.com)

(https://www.xing528.com)

图2-15 采用p-MOSFET测得的在不同栅介质上的钼栅的功函数视在值

(功函数随钼栅下方的栅介质不同而不同,并与真空值不同)(来源于参考文献[67])

对于沟道掺杂浓度非常低的器件,比如FinFET或超薄体SOI MOSFET,合适的Vth要求栅功函数更靠近硅禁带中央。因此,候选金属的选择会稍稍容易。据仿真预测,对于FinFET,偏离硅禁带中央±0.2eV的栅功函数是适合于p-和n-MOSFET器件的[69]。为了实现使用金属栅得到相对较小的功函数范围,有几项技术可以被采用,例如,掺杂的镍硅化物栅、在钼中注入氮,以及金属混合及合金。然而,一个完整的方案还有待研究。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。