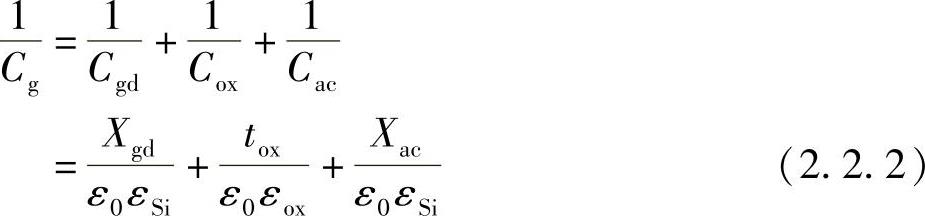

当栅氧中存在电场时,静电边界条件使多晶硅靠近氧化层界面附近的能带弯曲。当栅氧足够薄时,硅栅和沟道之间的耗尽区所贡献的电容就需要特别注意了。图2-12显示了反型区栅电容各分量的等效电路。等效栅电容(即CET)与这些电容分量的关系为

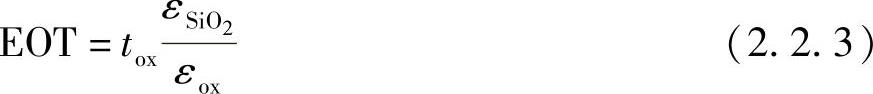

式中,变量的含义与图2-12中一致。ε0=8.85×10-12F/m,是真空介电常数;εSi=11.7,是硅的相对介电常数。在式(2.2.2)中,栅介质的物理厚度为tox,相对介电常数为εox。栅介质的EOT由下式给出:

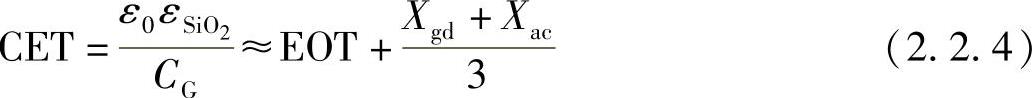

式中,εSiO2=3.9,是SiO2的相对介电常数。因此,从电容角度考虑,厚度为tox的栅介质与厚度为EOT值的SiO2膜等效。通常用CET描述总的有效栅电容

Xgd和Xac是与偏置有关的,因此CET也依赖于栅压VG。在典型的器件工作条件下,栅耗尽和量子效应对CET分别贡献有几Å的厚度,所以使用超薄栅介质时,CET将明显大于EOT(按百分比计算),具体大小由栅介质决定。较薄的CET和较高的栅压将转化为较高的反型电荷密度和较好的器件特性,因此,随着每一代工艺技术中采用的电源电压的减小,栅层叠结构的缩小不仅要求栅介质(EOT)变薄而且要求栅耗尽效应缩小(Xgd)。

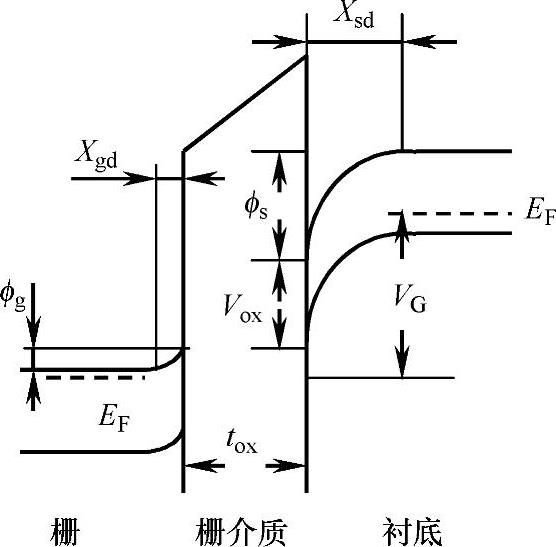

采用静电学可以简单估算栅耗尽效应和CET。考虑一个偏置到反型区的n-MOSFET的n+型多晶硅(见图2-14),平带电压(VFB)和衬底电压降(ϕs)、栅电压降(ϕg)、氧化层电压降(Vox)之和等于栅压Vg。

图2-14 n-MOSFET栅正偏置时的能带图

(靠近氧化层界面的多晶硅栅中存在着有限厚度的耗尽层)

栅的掺杂浓度一般高于沟道掺杂浓度。因此在亚阈区,氧化层界面电位移的连续性意味着栅极的能带弯曲小于衬底的能带弯曲。在强反型条件下,栅氧上界面的边界条件是

(https://www.xing528.com)

(https://www.xing528.com)

使用耗尽0000近似和假定栅的掺杂浓度(Ngate)为均匀掺杂时,栅极电场Ez可以使用高斯定理求解

因此栅的电压降为

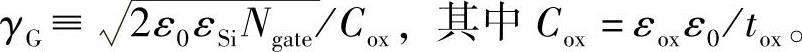

式中,

在强反型开始前,大约在2ϕb=2(kBT/q)ln(Nsub/ni)时,衬底能带弯曲ϕs达到饱和。注意

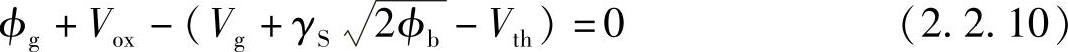

式中,γS的定义与γG的定义相似,仅用Nsub代替Ngate。因此式(2.2.5)变为

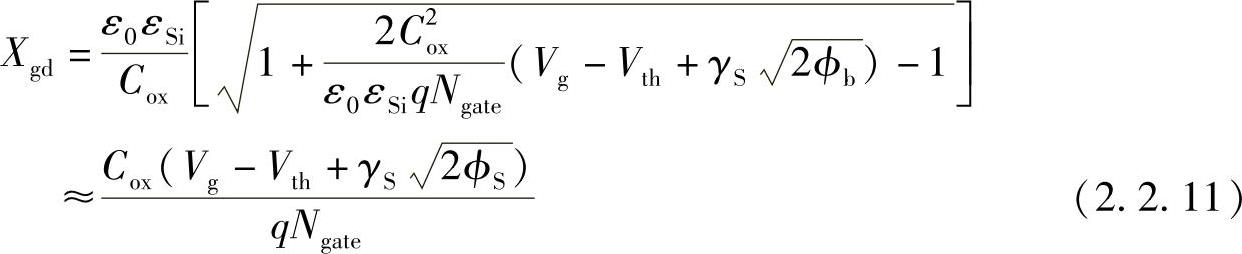

当Vg>Vth时,栅耗尽宽度Xgd可由式(2.2.6~式2.2.10)求出

对于给定的栅压、氧化层厚度、栅掺杂浓度和阈值电压,结合电荷质心模型,可以由式(2.2.4)和式(2.2.11)估计CET。例如,假定EOT=12Å,VG=1.1V和Vth=0.3V,由式(2.2.1)得到ac电荷中心Xac=9.2Å。进一步假定Nsub=3×1017cm-3和Ngate=1×1020 cm-3,可以估算得到栅耗尽层宽度Xgd=15.7Å。因此,量子效应和栅耗尽效应一起对CET的贡献为8.3Å,而栅介质的贡献为剩下的12Å。显然,对于很薄的EOT,再缩小栅介质对于减小CET作用已经不大了,因为多晶硅栅耗尽和量子效应的作用在CET中占的百分比已经很高。因为量子效应的贡献不能被减小,因此通过工艺改进或者使用新颖的栅电极材料(如金属栅电极)来减小多晶栅耗尽效应就变得非常关键。国际半导体技术路线图(ITRS)预测,在未来几年,量子效应和栅耗尽效应会给EOT附加8Å,而在2007年,65nm中将采用金属栅,它会给EOT附加5Å[66]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。