快速热处理(Rapid Thermal Processing,RTP)是一项有着十余年历史的非常重要的半导体制造技术,它的发展历程可以回溯到20世纪60年代[49]。RTP能取代传统的分批装片炉热处理有两个主要原因:优良的气氛控制和减小的热消耗。气氛控制是RTP得到广泛应用的最初动力。最初RTP工艺的应用是形成硅化锑(TiSi2),正好使得RTP特长得到充分发挥。工艺中要求氮气气氛必须严格控制使环境氧气的水平小于10ppm[1]。这种低氧含量在低流片量的单片RTP反应腔中很易实现,而在大流片量的批式炉管中则很难可靠地维持。早期RTP系统的缺点是温度控制和重复性不够好,但是生长TiSi2对温度控制和可重复性不很敏感,而RTP较短的工艺时间则具有明显优点,可以减小热退化和横向过度生长或桥接。

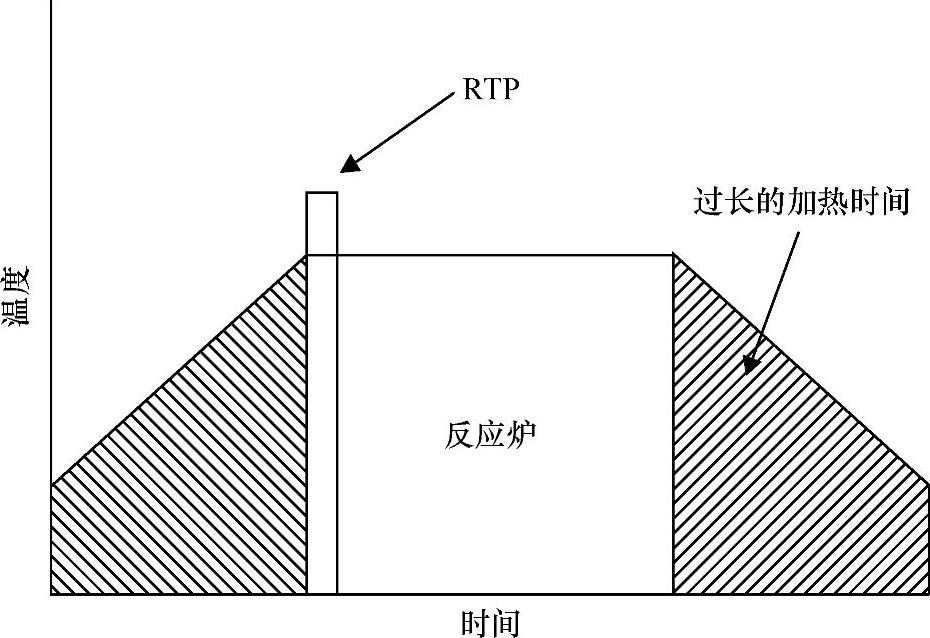

RTP取代分批装片炉的第二个动力是可以减小晶圆在高温中的暴露时间。在高温氧化或退火时,加热炉中温度缓慢的上升和下降(典型的温度变化速率为10℃/min)使晶圆长时间的处于高温下,这些过长的时间将导致不必要的掺杂和缺陷扩散。如图2-7所示,RTP使温度上升和下降加速,典型的可以达到75℃/s,这样就减小了晶圆过多的热暴露和不希望的扩散。

图2-7 在RTP和批式炉之间的“热暴露”对比

RTP技术 快速热处理要求设备具有特定的技术能力,包括精确的气氛控制、高达250℃/min的升温速度、峰值退火温度均匀性(3σ为3℃)、300~1200℃的温度控制范围和不受晶圆发射率影响的温度测量。在多数的RTP工序中都要求精确的气氛控制,包括金属的硅化处理、注入退火和热氧化。早期RTP设备的气氛控制依赖于大范围的净化,因为炉腔对生产环境是“打开的”,以装卸每个晶圆。这限制了生产量和最终能达到的气氛控制。一种改进的方式是将RTP腔装在集簇设备上,为实现纯净的氮气气氛,采用真空装载锁完成快速的气体交换。集簇设备也可以用于单腔或者多腔工序。气流模型的改进使非装载锁系统也可以在高产量的情况下达到低于1ppm的气体纯度。在腔门打开时,这些系统在晶圆输运过程中一般采用高速气体纯化以最大程度地避免氧气的侵入。

在注入退火时,为了达到要求的升温速度,RTP要求由晶圆和直接支撑晶圆的结构所组成的整个被加热物体的“热质量”尽量得小。大多数RTP设备使晶圆与腔体之间热隔离,使用灯辐射方式满足快速升温时的热需求。另外一种方式是将晶圆快速地放入到一个其热质量比晶圆大得多的已加热环境中,此时晶圆引起的环境温度变化将很小,然后晶圆逐渐达到环境温度。

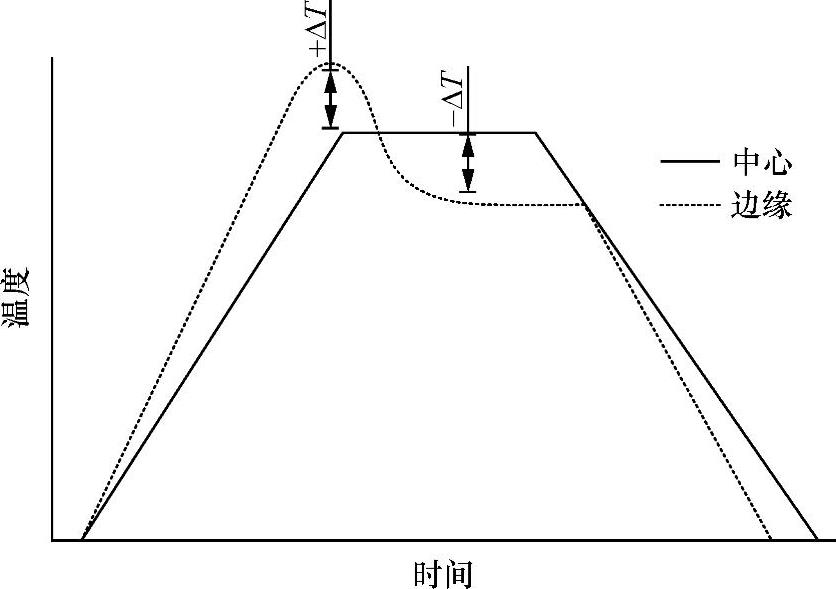

为了在RTP要求的较大温度范围内均匀性达到3σ(在一个晶圆内和多个晶圆之间所有测量点的标准偏差的3倍)为3℃的要求,需要对均匀性实现有效的控制。由于晶圆中心与边缘处表面积与体积之比不相同,在RTP加热过程中的不同部分要求不同的能量分布。如图2-8所示,在升温过程中,晶圆边缘的温度一般高于中心的温度,然而在温度稳定后和降温时,边缘的温度又会低于中心的温度。在采用灯加热方式的RTP设备中,解决这一问题的方法是在腔体的中心和边缘的不同区域采用不同的灯组合,并且在加热过程中调整不同灯的功率,保证不同时刻温度的均匀性。为实现积极实时的温度均匀性控制,最先进的系统采用高速、多点测量和多区域控制。

图2-8 未能实现有效均匀性控制的中心和边缘温度分布

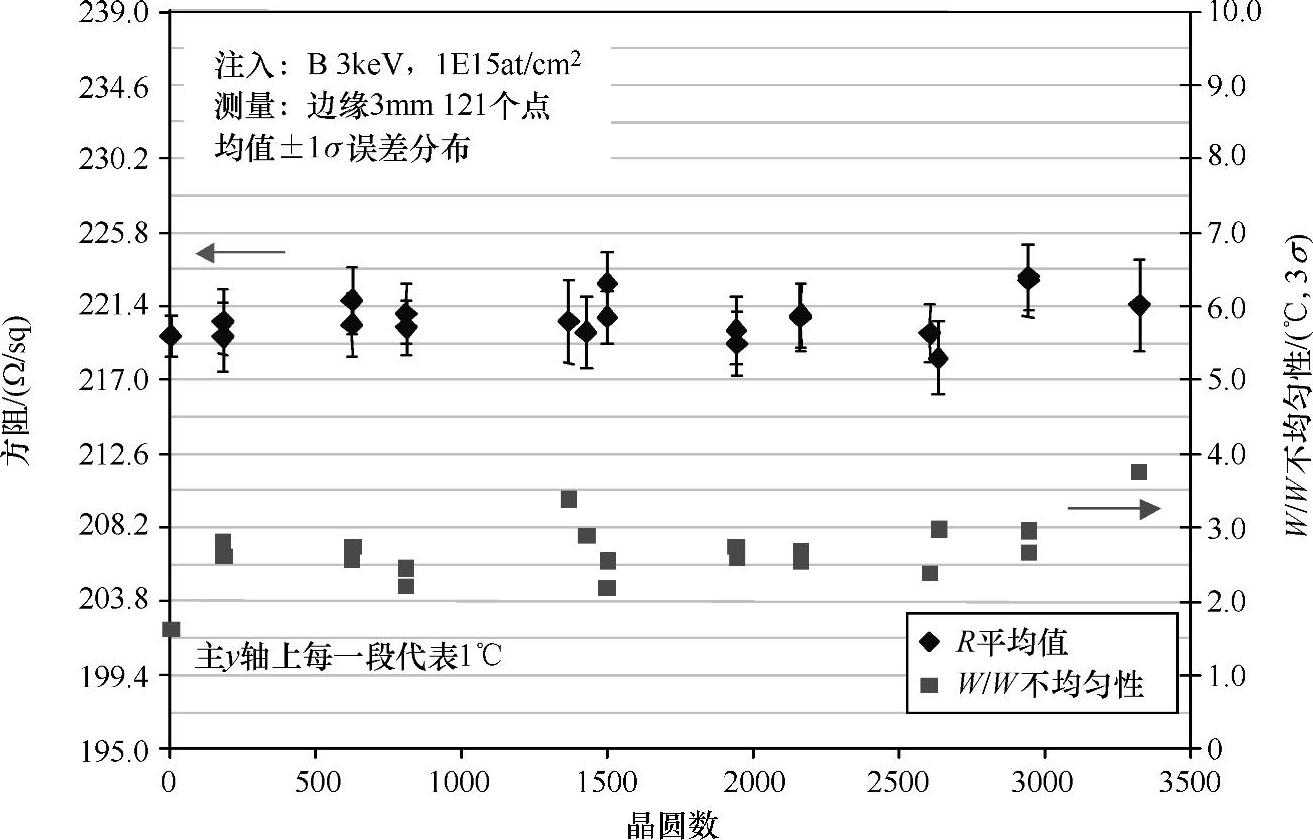

对均匀性控制最具挑战性的工艺是用于现代器件注入离子激活的高温尖峰退火。尖峰退火并不要求保持在峰值温度,而是到达预期的温度后马上降温,实现一个三角形或者尖刺形的温度-时间分布。注入离子的激活是与温度非常敏感的工艺,为了达到晶体管源漏区浅结的要求,需要实现3σ为3℃的温度控制。图2-9所示为在300mm晶圆上距边缘为3mm范围内实现了上述温度均匀性的情况。

RTP设备测温系统采用光学测温,它测量晶圆本身的灰体辐射以确定温度。在老式RTP系统中,用热电偶直接接触测量温度,但是这种方式由于热接触方式以及局部的热扰动会引起温度误差和不均匀性已被淘汰。准确的光学测量要求知道测量波长处晶圆发射率的数值(晶圆发射的能量与同样温度下理想黑体发射的能量之比)。测温装置设计采用两种主要的方式来应对这些挑战。一种方式是在晶圆下方创造一个高反射率的环境以实现理想黑体腔的特性,因为这能增强晶圆的有效发射率并减小可能出现的测量错误。另外,用一个分离的探针实时测量发射率并且对任何存在的误差进行校正[51]。第二种方式是实时测量灯功率周期变化的反射系数来获得假设无晶圆发射时的发射率(发射率=1-反射系数)。然后,用测量的发射率校正光学测温仪的读数[52]。

图2-9 RTP尖峰退火在3σ为3.2℃控制时的方阻均匀性/可重复性

这些技术,包括气氛控制、低的热质量、均匀性控制和温度测量,共同构成了RTP设备的核心,并使RTP在很宽的温度范围内得到广泛的应用。对未来的65nm到45nm的器件,RTP退火的热消耗即使是已经受到了限制,但对某些工艺步骤来说还是太高。一种方案是通过仅在晶圆的表面加热使暴露时间减小到毫秒级。这被称作热通量退火,可以用闪光灯或激光实现[53,54]。

RTP应用 随着RTP工艺设备的改进和成熟,现在具备了用于完成CMOS和DRAM制造的所有的热退火和氧化工艺。主要的退火应用包括难熔金属硅化物的形成(例如TiSi2、CoSi2、NiSi)、离子注入退火、BPSG的稳定性和回流,以及接触金属退火(如TiN)。主要的氧化应用包括栅氧氧化和氮化、隔离槽内壁隔离层氧化和牺牲氧化层氧化。(https://www.xing528.com)

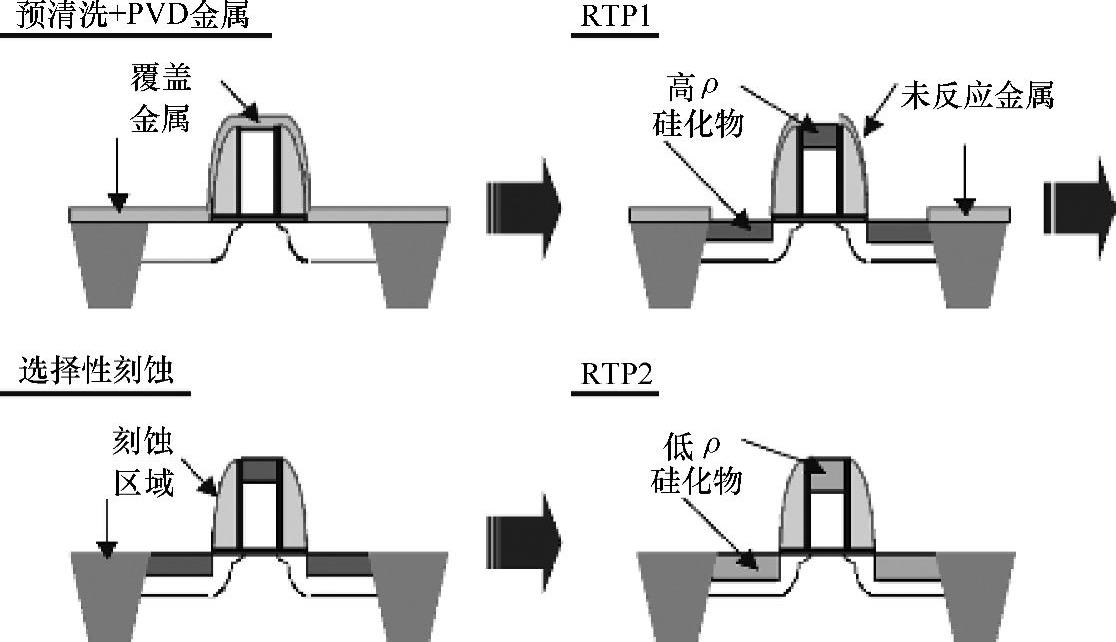

从20世纪80年代开始,自对准硅化钛技术被引入到CMOS工艺中,减小了源漏和栅区方阻,在晶体管与金属互连之间实现较好的欧姆接触。这道工艺是自对准的,因为在覆盖溅射金属后,金属仅在金属源漏和栅区位置直接与硅接触的地方形成硅化物,并不在侧墙隔离层和隔离结构上形成硅化物。近几年,为了进一步缩小器件尺寸,使用的金属已由钛变为钴再到镍。如图2-10所示,自对准金属硅化物一般经过两个RTP步骤形成。在清洗和溅射或物理汽相淀积(Physi-cal Vapor Deposition,PVD)完成覆盖金属膜淀积之后,第一次RTP退火(通常称为RTP1)形成金属硅化物。RTP1的温度必须高到能使金属-硅发生反应并且生成物要达到足够的厚度和希望的金属硅化物相,但是温度又要足够低以免金属硅化物横向生长到栅的侧墙隔离层上,否则将导致栅与源漏短路。气氛控制对RTP1来说是关键,因为如果气体氛围中即使氧的比例只有百万分之几,金属薄膜也会很快被氧化耗尽。

图2-10 自对准工艺顺序

在选择性刻蚀移除侧墙隔离层和隔离区域上未反应的金属后,第二次退火(RTP2)通过改变金属硅化物相或组分来减小方阻。RTP2一般要求温度高于RTP1几百度,这个温度太高以致于在二次退火这一步内不会生成金属硅化物。RTP2的最高温度一般受到两个因素制约。一是温度太高会出现形态衰退,称作凝聚。另外如果温度太高可能使硅化物的相或结构发生变化,导致电阻退化。

钛的硅化物是首次在逻辑应用中被广泛使用的材料。TiSi2的C49相一般在RTP1阶段,650℃、30s的条件下形成。RTP2将C49相硅化物变为C54,可以实现大约(13~16)μΩ·cm的低电阻率,RTP2的工艺条件一般是850℃,20s或者更低。随着器件尺寸的缩小,使得钛硅化物的应用范围很难扩展到0.25μm以下。当线宽和金属硅化物的厚度进一步减小时,使C49到C54相变成核过程中不出现硅化物的凝聚将变得非常困难[55]。这些限制要求高温时间必须更短,而在高温时工艺窗口最宽。

为了改善缩小变窄的线宽,作为TiSi2的替代者,选用了钴硅化物。在钴自对准硅化物工艺中,RTP1的工艺条件一般是500~550℃、30~60s形成CoSi。RTP2的工艺条件一般是750~800℃、30s使CoSi变为CoSi2,此时电阻率将降到14~18μΩ·cm。在覆盖金属淀积期间,钴一般被钛或TiN覆盖以防止其氧化。覆盖物将在RTP1与RTP2之间被选择性刻蚀掉。

在线宽缩小到50nm之下,钴硅化物也开始受到器件尺寸缩小的制约,并且驱使业界用镍硅化物取代之。一直到30nm线宽时,NiSi还可以保持较低的方阻[56]。NiSi可以用一步RTP,而不是如图2-10所示的两步RTP工艺实现,RTP温度一般在400~500℃。然而,栅长小于100nm的方阻的减小表明,这会造成窄线条产生过量的硅化。采用两步RTP控制NiSi的形成可以解决过量的硅化和由多晶耗尽及结泄漏带来的问题。第一步,RTP1,形成富镍相的硅化物Ni2Si,而RTP2完成了实现低电阻率相NiSi的反应。两步形成NiSi要求RTP设备具有先进的能力。首先,RTP1要求较低的工艺温度,250~350℃。这低于一般光学测量仪的测量范围。第二步,RTP1要求精确地控制温度均匀性。硅化物的厚度是由反应温度而不是由淀积的镍的厚度决定的,并且硅化物生成反应对温度极其敏感[57]。最后,像之前的钛和钴一样,NiSi要求精确地控制环境气氛,氧的含量要低于1ppm。

CMOS工艺主要依赖于离子注入和RTP退火以确定对器件性能有决定作用的杂质分布。热退火的作用是修复离子注入带来的损伤并使杂质原子处于替位状态,起到提供载流子的作用。由于RTP精确的热消耗控制,使得晶体管尺寸在横向和纵向的缩小成为可能,因此已取代了用于离子注入退火的批式加热炉工艺。如图2-7所示,由于减少了过多的热暴露时间,使RTP在实现与批式加热炉退火相同的方阻时,能实现更浅的结。

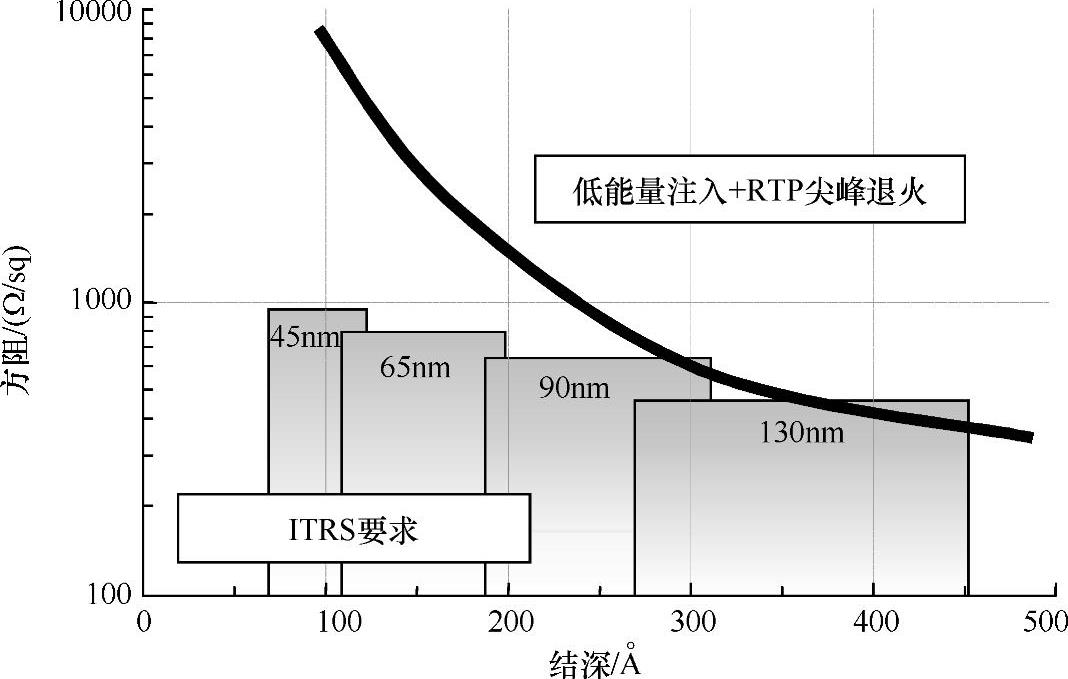

RTP热消耗已经得到连续的减小,从原先950~1050℃之间30~60s保温时间的退火变为1050~1100℃的0s尖峰退火。将升温速度从50℃/s提高到大于250℃/s,可以使RTP热消耗得到进一步减小。为了满足国际半导体技术路线图(Inter national Technology Roadmap for Semiconductors,ITRS)对源漏和其延伸的轻掺杂结的要求,热消耗还需要得到进一步减小。ITRS规定了这些结的结深和方阻的目标,如图2-11所示。图中同时显示了RTP尖峰退火的低能注入耦合的典型性能。

虽然90nm的要求可以达到,但65nm要求结深和方阻进一步减小。几个技术的应用将使这种缩小成为可能,这些技术包括热熔退火、注入区的固态外延再生长,以及能在RTP退火时抑制扩散的离子同步注入。

几个因素能将RTP拓展应用到CMOS工艺中所有的热退火和氧化。首先,整个工艺流程中热消耗控制是关键器件尺寸能实现缩小的根本。第二,所有的氧化层厚度和退火步骤都已经缩小到单片加工工艺的范围。第三,新颖的工艺,例如现场水汽生成,已经使改善器件性能成为可能[59,60]。最后,单片工艺减小了周期时间,减少了工作量,使改善生产效率和生产时间有了可能[61]。

总之,RTP在半导体中是一项关键的和促成性的技术。低温工序和毫秒级热暴露的扩展能力将使器件的继续缩小成为可能。在未来的几年时间里,单片工艺的经济性和高效率将持续的促使热工艺从批式向RTP技术转换。

图2-11 显示有RTP能力和ITRS要求的方阻与结深关系曲线

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。