持续的物理尺寸缩小增加了器件电参数的容差,并且成为对建模的挑战。在BSIM4之前,模拟软件中没有包含栅电流模型,设计人员不得不自己考虑栅电流的计算。沟道中杂质的统计波动将影响位单元中使用的小几何尺寸晶体管,但是对其建模难度较大,使得建立的模型精度较差[3]。由于邻近效应和STI应力导致的迁移率退化与版图本身的关系非常密切,因此建模难度也很大[10,11]。目前已经推出了一些新的工具,通过版图提取在这个领域提供一些帮助。最好的工作方式是理解这些效应,然后在物理设计中使这些效应对电路的影响最小。第2章将详细讨论这些效应。

由于halo注入(大斜角注入)效应与沟道长度之间关系的无规律性,导致对halo注入的逻辑过程进行的模拟建模精度很差。这样混合信号设计工程师就需要使用“模拟晶体管”[17],这将增加费用,并且有时还没有模拟晶体管可供使用。除非你能够与Foundry生产线共同工作,有能力将halo对DIBL、Vth以及厄尔利电压的影响及其和晶体管沟道长度的关系进行建模,否则明智的做法还是采用模拟晶体管。正如IEDM 2002出版的参考文献[16]中所述,这样一种模型并不是不可能的,但是并不是每条Foundry生产线都能提供这种模型。无论什么原因,如果你必须在模拟设计中使用halo工艺的晶体管,而SPICE模型又没有考虑halo效应(反型短沟道和漏感应阈值电压漂移)和输出电阻以及厄尔利电压的变化,选择合适的晶体管尺寸就变得非常重要。要求模型能够适用于选用的晶体管尺寸,以避免由于晶体管特性随着沟道长度的非线性变化而影响模拟精度。

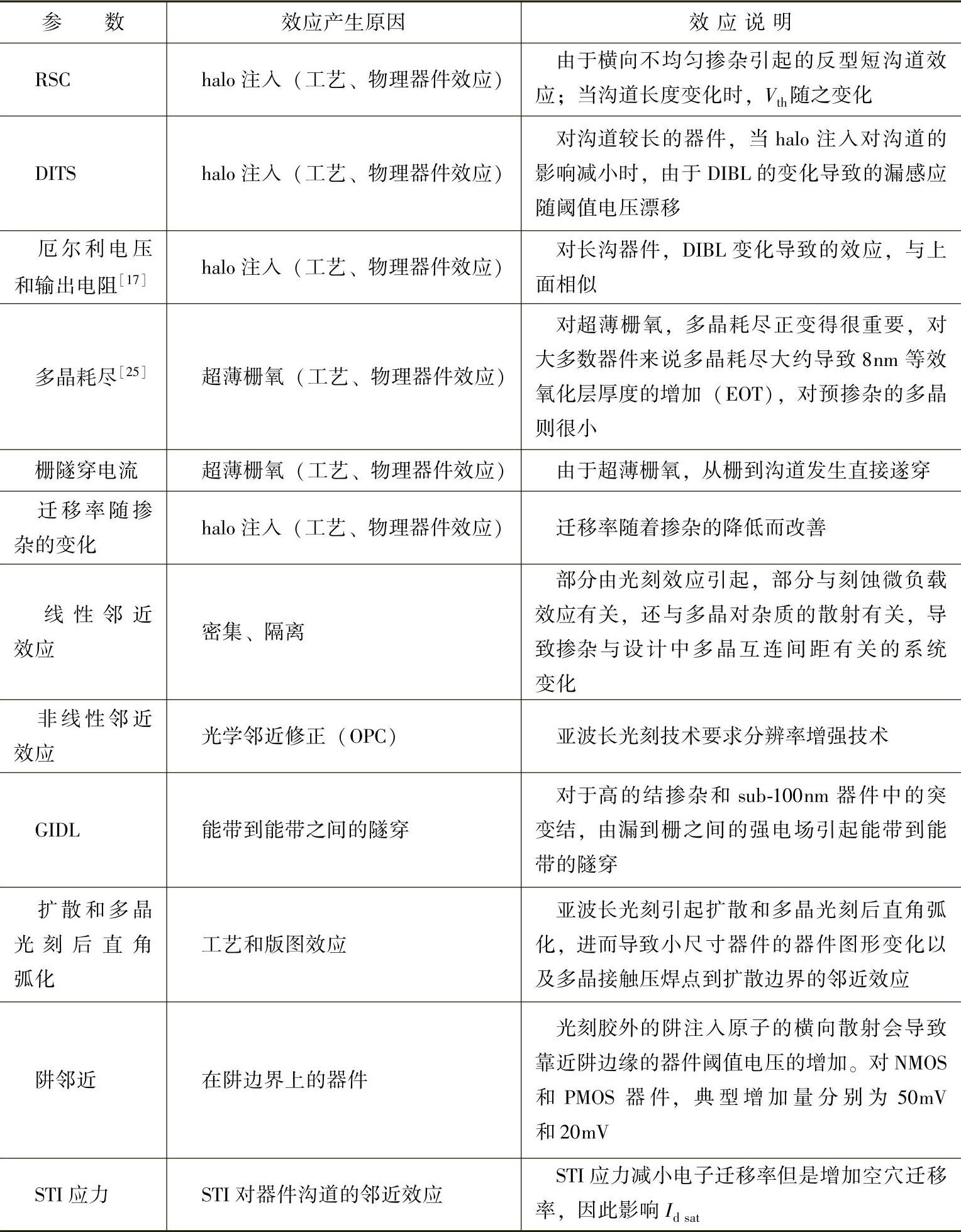

需要建立模型的新物理效应包括对Vth与晶体管多晶长度之间关系产生影响的halo注入效应(反型短沟道(RSC)效应)[16]、栅感应漏极泄漏(GIDL)、漏感应阈值电压漂移(DITS)[24]、输出电阻和厄尔利电压变化,以及栅电流[15]。在以往的模型中,仅从BSIM4开始才对其中一部分新效应建模[24]。对小于130nm的工艺节点,强烈推荐在所有的仿真中,包括在数字电路仿真中,采用BSIM4模型。

针对上面描述的注入工艺和特征尺寸的波动,统计模型对解决其中一些问题也是必需的。除非能明智地选择适合特定电路的模型组合,否则只是采用工艺角模型会以速度、功耗和面积为代价,产生不切实际的工艺组合,导致对电路过于保守的设计。另外,通过传统的五点工艺角方法并不能建立关键工艺角模型,因此对特定的电路来说,可能并没有分析最坏情况。表1-1是对建模挑战的总结。(https://www.xing528.com)

表1-1 sub-100nm工艺中器件建模挑战的总结

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。