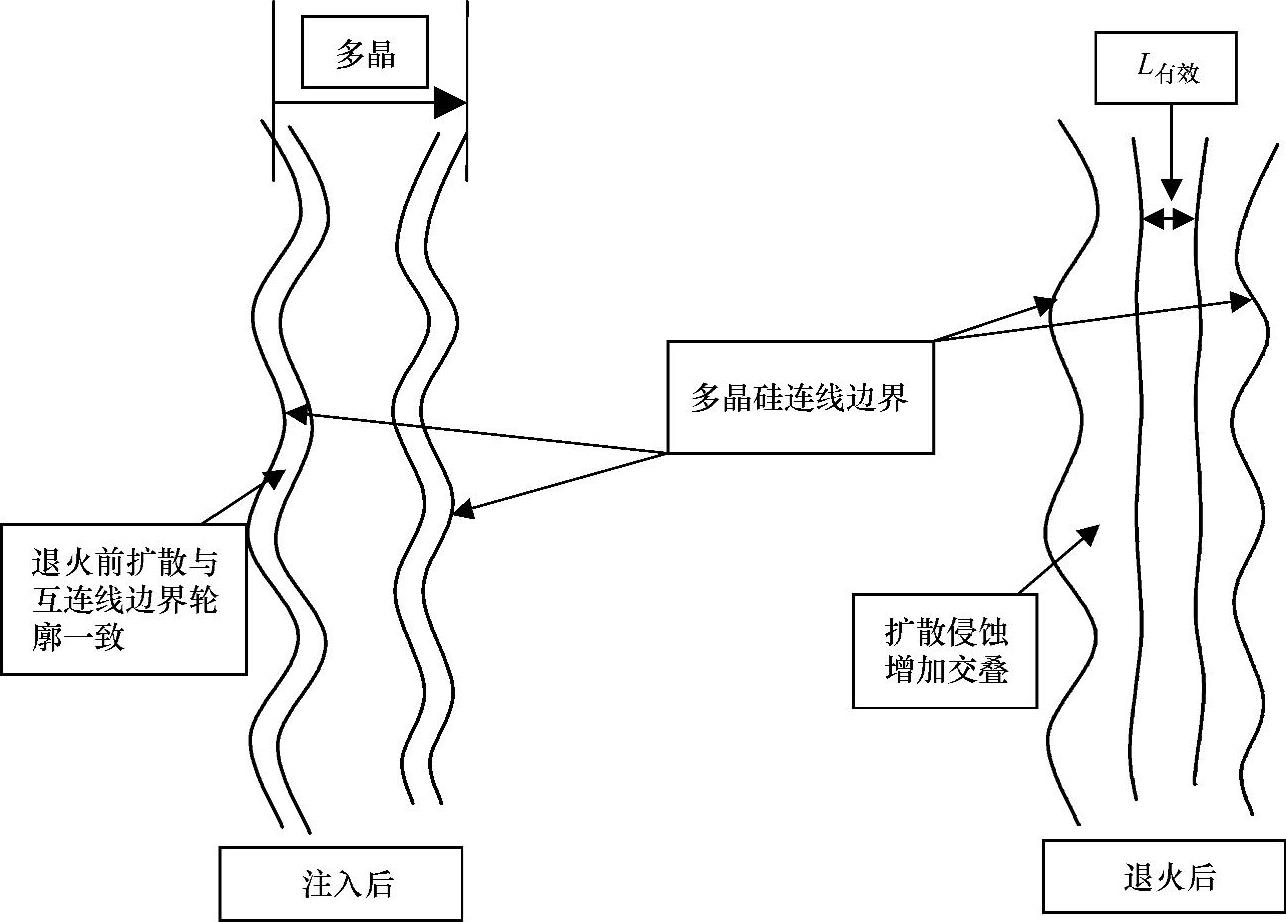

随着工艺缩小,栅长特征尺寸(CD)的绝对物理变化没有减小,因此对未来工艺节点来说,栅长CD变化的相对百分比会增大[7]。除此之外,栅长减小到100nm以下时,互连边缘的粗糙度(LER)影响着几个晶体管参数,因此受到了越来越多的关注。sub-100nm工艺中LER控制是关键,因为随着工艺的缩小,对于更短的栅长,LER对器件的影响来说非常重要。LER控制需要采用先进的光刻和刻蚀工艺,这只能通过更好的工艺控制来改善。较大LER带来的负面作用是更大的交叠电容Cgd,特别是对PMOS。受到影响的其他器件参数包括DIBL的和阈值电压,因为退火后,有效沟道长度会随着LER减小,特别是PMOS(见图1-14)。当晶体管的Leffective值由于LER效应而减小时,PMOS的Vth和穿通电压将会受到相反的影响。

Vth的变化受到掺杂的随机波动和栅CD变化的影响。薄栅氧与掺杂沟道的形成一起引起沟道杂质的波动,波动情况还与栅多晶的形态有关(参见图11-7)。

这些效应使Vth更加难以控制,特别是晶体管Vth匹配更加困难,尤其是对小尺寸器件。从图11-37可以看到,最小器件Vth的变化最大,但其会逼近一个渐进值。避免使用最小宽度的晶体管是一个明智的选择,除非Vth变化不会引起电路失效。

负偏压温度不稳定性(Negative Bias Temperature Instability,NBTI)是栅氧厚度缩小后面临的一个效应。130nm工艺节点的栅氧厚度已经对NBTI非常敏感了[18]。任何引起断键的工艺步骤都会增强NBTI。特别是等离子或反应离子刻蚀是能引起键断裂的工艺,因此会使NBTI增强。65nm工艺节点中,栅氧厚度将等于或低于10Å[1]。对这个量级的厚度,界面控制非常关键。多晶耗尽将会是制约性能进一步缩小的限制因素,为此需要采用无耗尽的栅材料。90nm及以下工艺节点的栅氧厚度控制对保持一个可预期的、较小的栅电流来说是很重要的。栅氧厚度每减小1Å,栅电流大约增加2.5倍(见图1-13)。(https://www.xing528.com)

图1-14 LER使交叠电容增加而使沟道长度减小

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。