晶体管性能 晶体管的品质因数现在正偏离与栅长倒数成正比的关系。导致这一结果的主要因素是:

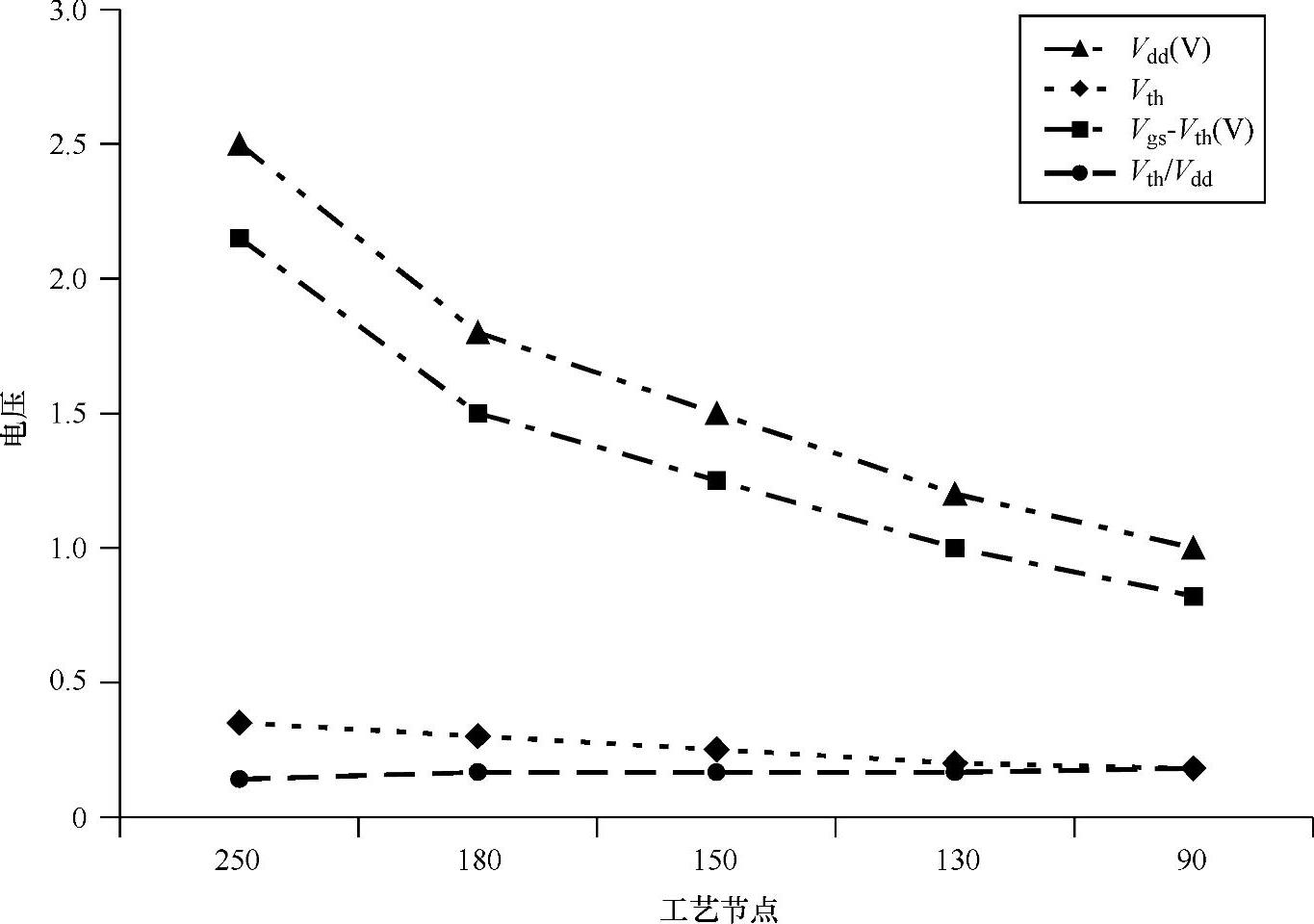

●Vgs-Vth不断缩小,而Vth/Vdd越来越大(见图1-11)。

●作为晶体管总导通电阻一部分的RSD的作用正变得更大,导通电阻部分由多晶栅与接触孔之间的间距以及RSD决定。

●浅结正使得掺杂水平达到饱和。使得RSD没有进一步减小的可能;同时,结电容却不断增加。

●由于电流的聚集,更薄的源和漏扩散使得RSD进一步增大。

●浅沟槽隔离(Shallow Trench Isolation,STI)应力感应的迁移率退化更加显著,虽然PMOS晶体管在STI应力下稍有改善,而NMOS晶体管则受到消极影响[10,11]。

●即使更小尺寸晶体管采用STI,ΔW也变得重要。

●现在漏电容的减小慢于面积的减小。

●对小几何尺寸器件,掺杂损失和掺杂的统计波动增加了器件的波动性:输入/输出、模拟和存储器设计对此特别敏感。

●为了控制漏感应势垒降低(Drain-induced Barrier Lowering,DIBL)效应而增加的沟道掺杂浓度则减小了载流子迁移率,而增加了体效应。

●薄栅氧导致杂质穿透,将影响PMOS的驱动电流[6]。

●随着栅氧厚度接近单层二氧化硅厚度,栅氧的缩小也变得越来越慢了(见图1-1)。(https://www.xing528.com)

图1-11 栅驱动与工艺节点的关系

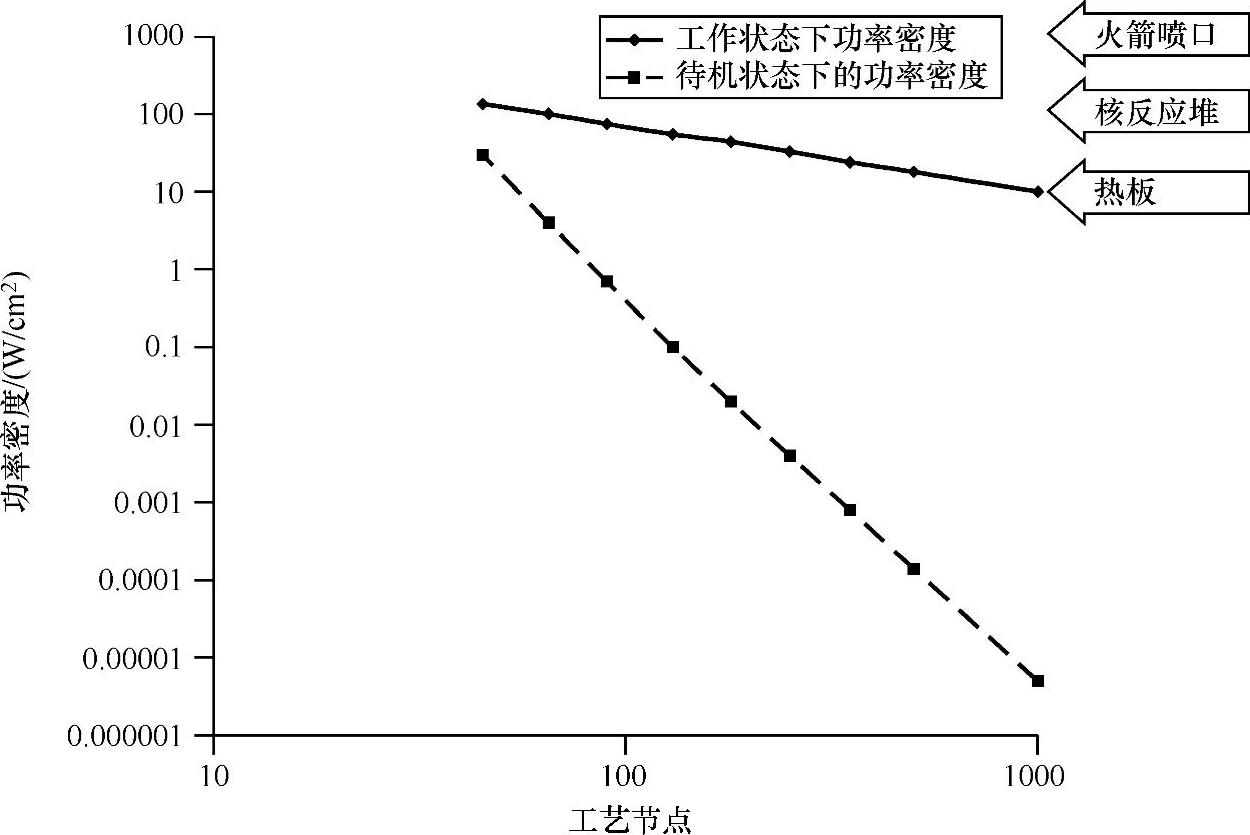

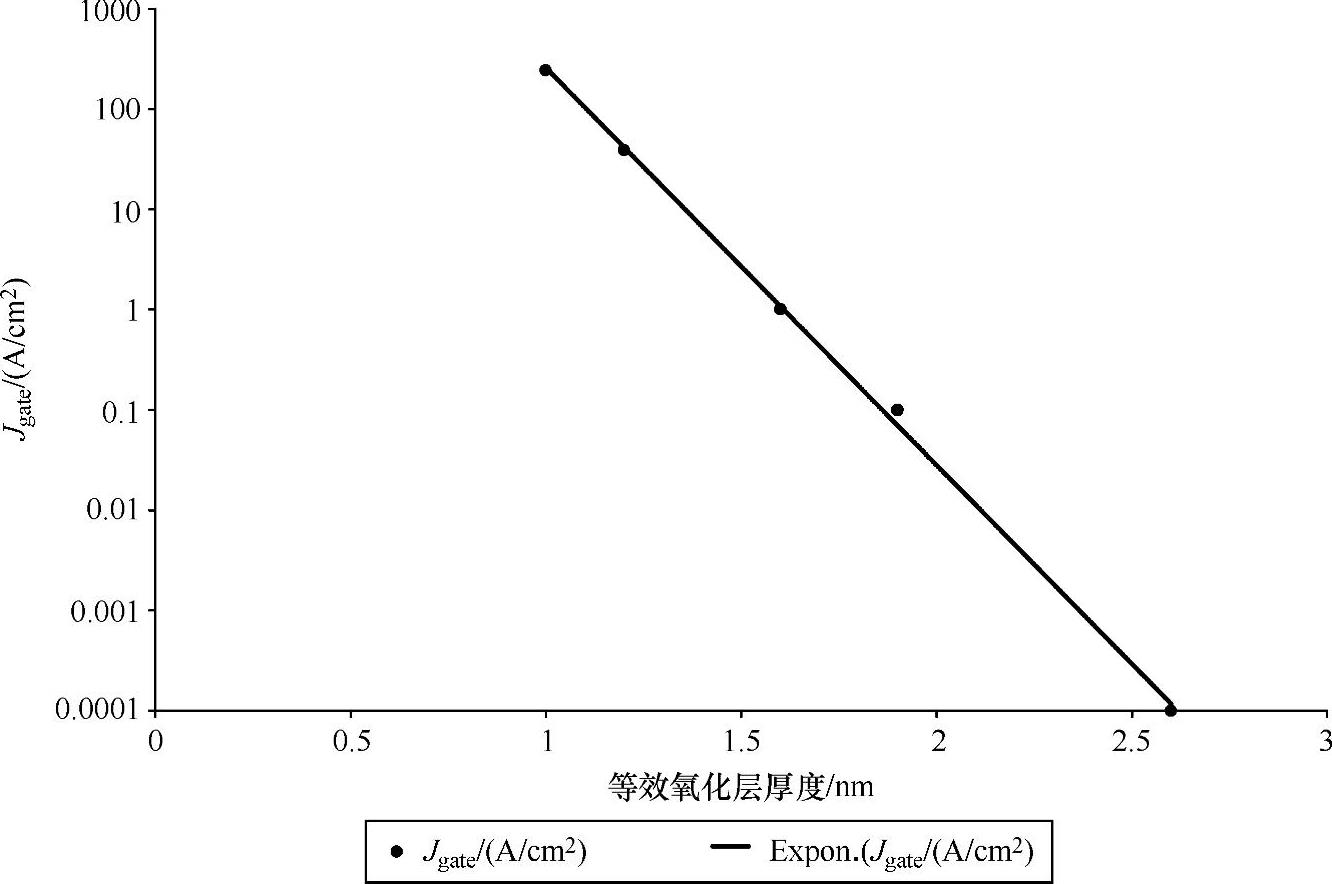

泄漏问题 如果不能通过设计方法学的改进减缓其增加的趋势,亚阈区泄漏的增加速率最终会与芯片动态功耗(见图1-12)的速率相同,特别是对几代工艺中的高性能微处理器而言。氧化层厚度每减小1Å,栅电流(见图1-13)会增加2.5倍,从130nm开始,每代技术间的栅电流变化约为两个数量级。

图1-12 CMOS功率密度的变化趋势

图1-13 NMOS的Jgate(A/cm2)与等效氧化层厚度的关系(数据源于NEC)

随着特征尺寸的减小,栅电阻不断增加,并且SD电阻也随着结的不断减薄而增加。对结泄漏来说,需要仔细地调整SD电阻,直到需要的源漏结深是采用实际工艺可以实现的。图1-4表明,从250nm减小到65nm,多晶栅厚度的变化很小,发生显著变化的只是多晶栅的长度和宽度。因此,沟道电阻随着工艺缩小而增加并且需要在晶体管模型中予以考虑。

为了继续改善晶体管Id sat,人们对应变硅沟道晶体管投入了大量的认真研究和开发努力,据报道,采用SiGe应变硅已经实现了10%~20%的改善[22]。一种初步的应变技术是采用氮化硅“帽”薄膜来提供应变沟道,只能实现适度的Id sat改善。提升源漏技术也在不断发展,但是该技术要求采用选择性外延工艺,这是一种困难的制造工艺。引入的许多新材料使高k栅氧化层成为现实,现在正采用NiSi取代CoSi[22]。尽管高k栅氧化层可以与金属栅一起使用,但是与硅不兼容,因此在集成方面提出了重大的挑战[4]。与多晶栅相比,金属栅具有的明显优点是因为它们不会发生耗尽,所以对相同的电容有效氧化层厚度(CET),工艺工程师不需要使用更薄的栅氧化层[4]。因此,对给定的氧化层CET,从理论上说金属栅技术的累积态栅泄漏更低。但是金属栅是非自对准的,因此为了采用金属栅,生产中必须进行革新。在准备本书时,预先掺杂的多晶硅正被用来减小多晶的耗尽问题,其代价是增加了刻蚀的复杂性。由于使用预先掺杂的多晶硅,一些厂商已经有了解决这些问题的方法。在集成电路生产的开始阶段,采用的材料只有5种,但是现在已经上升到20种了[23]。

由工艺技术缩小获得的性能改善已接近极限,但是尺寸的缩小有望会继续依据摩尔定律进行。现在,通过诸如新的晶体管设计和新材料及工艺改进可以改善性能,就最近开发的而言,包括高k介质、FinFET、SOI、应变硅以及纯硅衬底等。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。