金属电阻 互连线宽度小于0.1μm时,电阻率会随着线宽的减小以指数形式增加。对较窄的互连线来说,高电阻率阻挡层材料占据了导体横截面面积的较大部分。由于表面散射导致的电子迁移率减小成为电阻率增加的因素之一[2]。窄互连中形成的晶粒更小,在填充凹槽时不能再结晶为更大的晶粒,使得电阻率进一步增大。

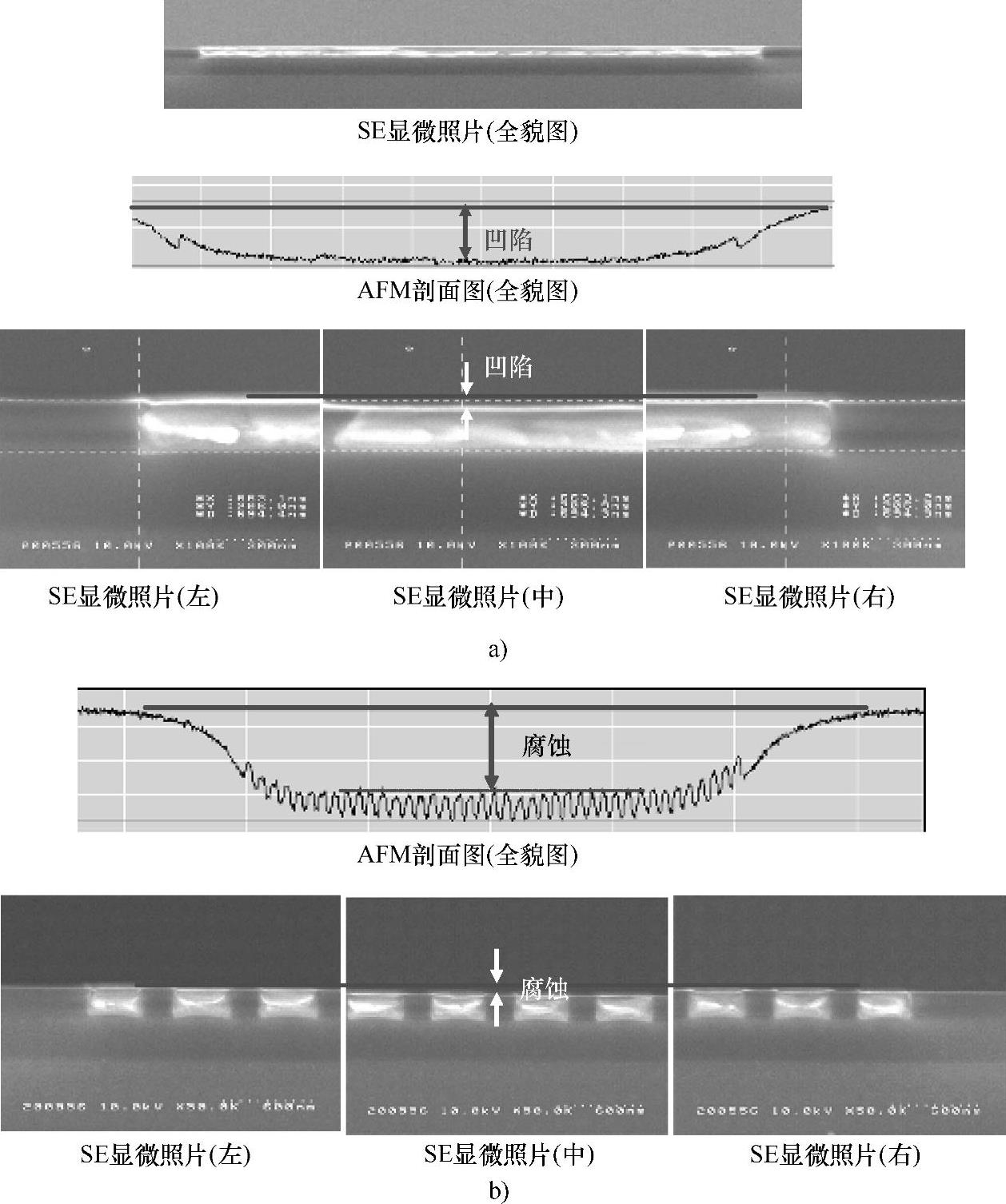

另外,阻挡层和凹槽(互连线宽度)特征尺寸(Critical Dimension,CD)的变化导致电阻的变化更大。这些因素与化学机械抛光(Chemical-Mechanical Pol-ish,CMP)形成的凹陷和腐蚀,以及光刻和刻蚀变形一起会引起互连线电阻的进一步变化[19](见图1-6)。

图1-6 a)互连凹陷:较宽互连线的面积 b)互连腐蚀:互连线和间距面积(图片来源于Trecenti/Hitachi)

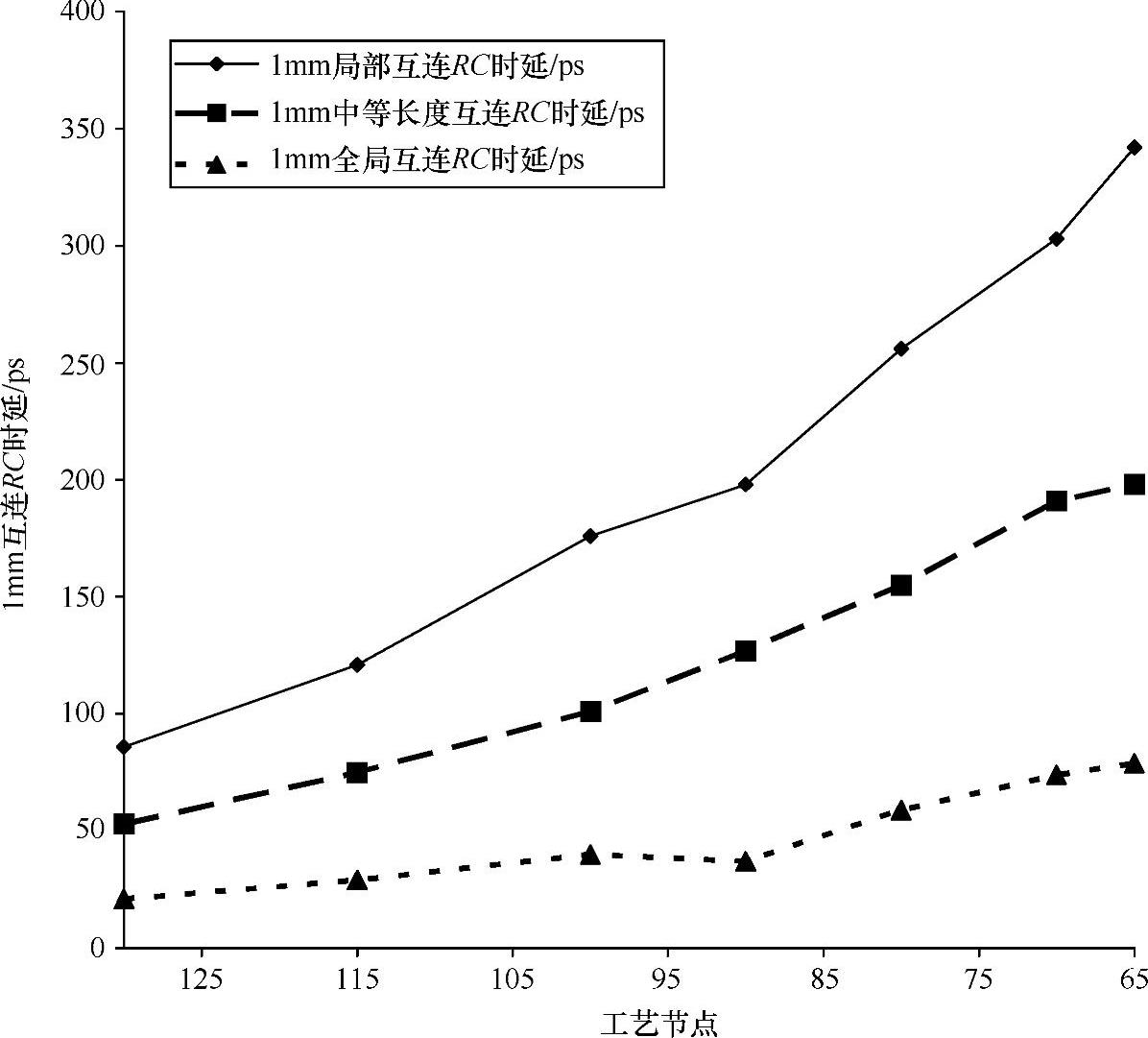

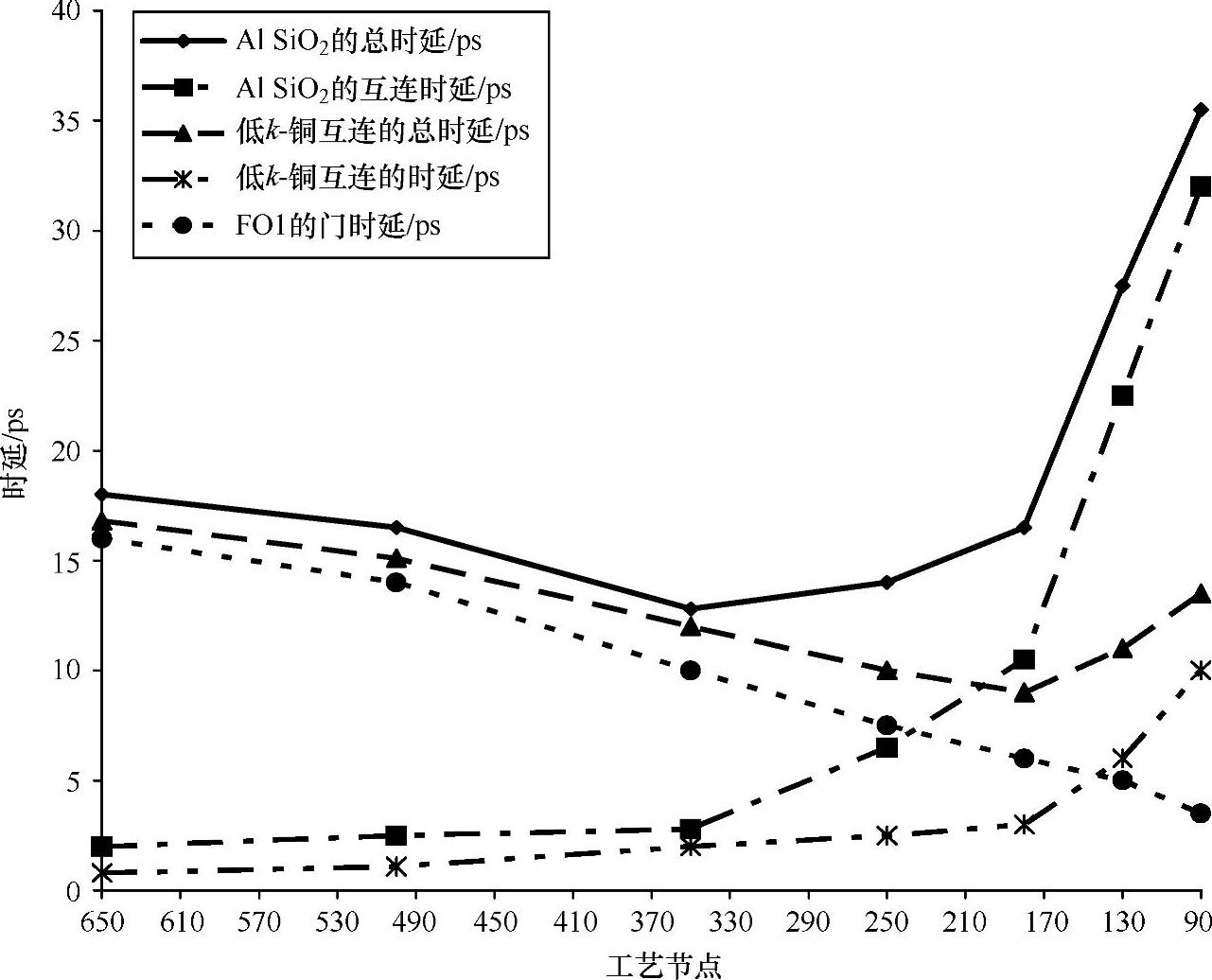

130nm工艺的互连RC值不断增加,并且对小于130nm的情况,局部和全局互连都变得更差。像上面解释的那样,随着线条尺寸的减小,电阻率不断增加(见第2章图2-25),而电容并未减小。其结果是,即使局部互连线的长度变得越来越短,而局部互连线的时延却在增加(见图1-7~图1-9)。虽然线条尺寸在减小,但是因为新的设计中增加了更多的功能,因此芯片面积并没有减小,全局互连线的长度也就没有减小。例如,180nm工艺生产的Pentium 4 Willamette core有4200万个晶体管;而130nm工艺的Northwood core的晶体管数达到了5500万个。这是因为在Northwood core中L2缓存从256KB增加到了512KB。随着工艺的发展,在一个时钟周期里信号可到达的区域与芯片面积之比正在减小。对一个采用先进工艺的设计来说,时钟频率在增加,而晶片的尺寸并没有减小,使这一问题更加严重。

图1-7 互连时延与工艺节点的关系

互连介电常数 低k介质使纳米CMOS中互连线缩小成为可能,但是随着互连线宽度和间距不断减小,使得低k介质的使用更加困难。这是由于间距较窄互连线之间的经时介质击穿(Time-Dependent Dielectric Breakdown,TDDB),使得低k介质存在着潜在的泄漏和可靠性风险。封装工艺带来的问题要求芯片上形成一层“硬外层”,使得管芯具有足够的机械强度,能够承受封装工艺施加给芯片的应力。这种硬外层的要求意味着位于层叠金属上面的几层需要采用较高介电常数的介质材料,这会稍稍减小低k金属技术的有效性。在8~9层金属的工艺中,低k介质将被限制到只能用于4~5层。具体情况取决于上层金属的使用方法。一般地,上层金属被用来作功率分布。在大多数设计中,它们也被用作时钟分布层,因此就增加了时钟网络的功耗并且也要求更多级去缓冲来自PLL的信号,这会导致更高的时钟偏差。

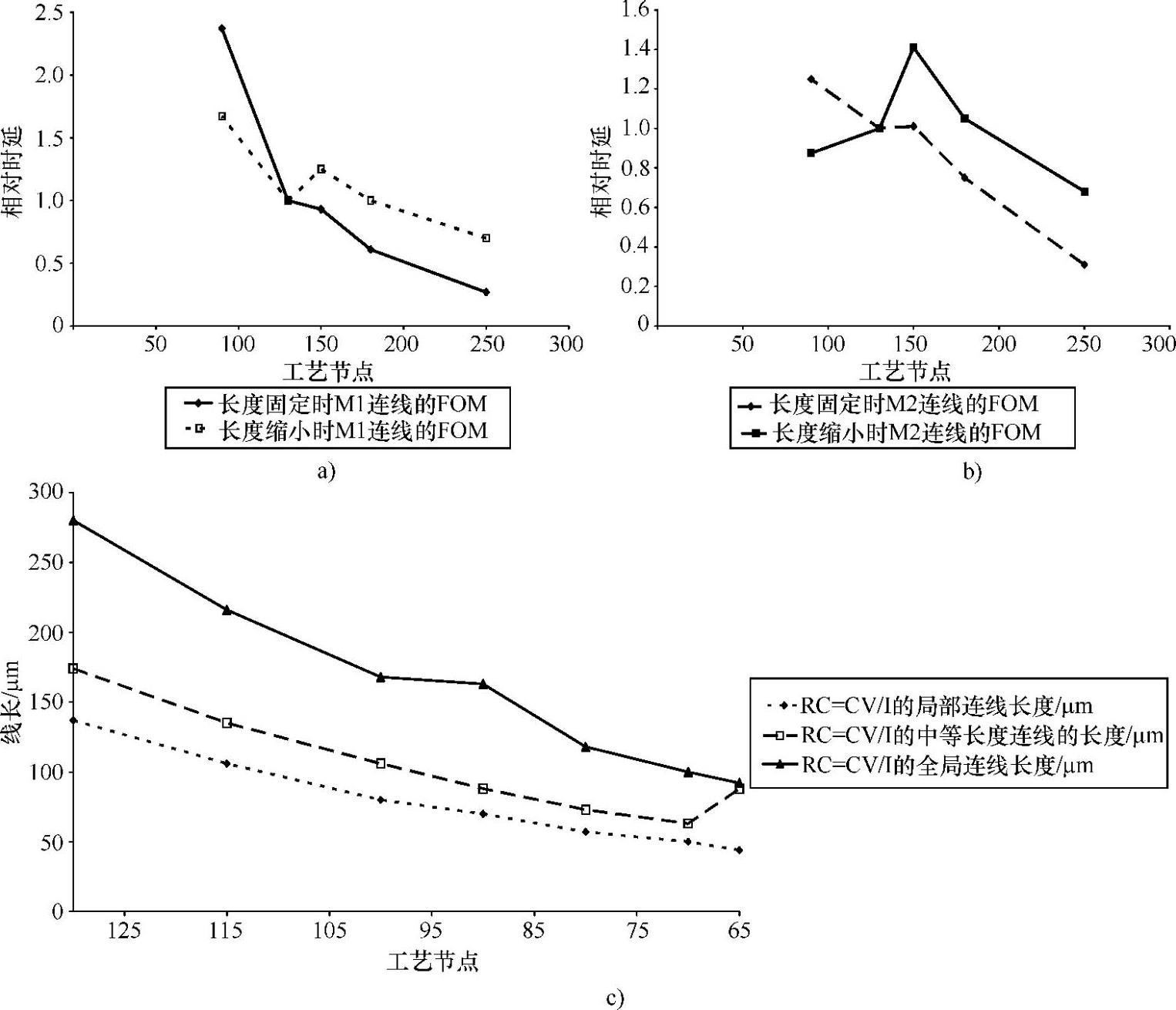

图1-8 a)M1(局部互连)的品质因数(无Miller,无重复) b)中等长度互连的品质因数(无Miller,无重复) c)等效于NMOS CV/I的互连线长度与工艺节点的关系

低k互连的应用严重缓慢 低k技术的引入比较缓慢的原因在于铜互连阻挡材料带来的问题、应对封装过程中应力的机械完整性问题以及制造过程中的一系列问题。这使得几个厂商转而采用氟硅玻璃(FSG)介质。(https://www.xing528.com)

低k介质形似果冻并且多孔,因此很容易受潮、吸附杂质并且气体也容易渗透。因为材料很软,很容易受CMP损伤,引起成品率降低和侵蚀,进而影响互连线电阻率。低k介质的导热性不良,这样会使互连的抗电迁移(EM)特性退化,在一定程度上抵消了一些铜互连EM特性好的优点。

图1-9 栅时延和互连时延与工艺节点的关系

互连的品质因数 (Figure of Merit,FOM)对每代工艺节点,按照其设计规则确定的互连线的FOM一直在下降(见图1-7~图1-9)。过去,晶体管性能滞后。现在,我们已经到达了这样一个转折点,即互连性能已成为芯片性能的制约因素。局部互连性能未得到改善,而全局互连实际上正变得更慢,特别是如果增加了附加的功能使得互连长度没有减少[12-14]。不管工艺技术如何缩小,由于在新的设计中功能不断增加,芯片尺寸却没有减小,总是维持在与以前设计相同的尺寸上。其他情况下,例如微处理器,不管工艺技术如何缩小,芯片尺寸实际上都在增加。尽管工艺技术在缩小,如果芯片变得更大,在不同模块之间就需要全局互连传递信号。

已经预见到的是,当工艺技术缩小时,时钟频率将增加,而一个周期中可达到的区域与总芯片面积的比率会下降[13]。为了使互连主宰的路径可以实现更好的缩小并且不限制频率,就迫使设计者在全局互连上插入更多的中继器,并且有时在全局信号中必须采用流水线方式。然而,这将增加芯片面积、功耗和时钟负载[14],也增加整个芯片时序的复杂性。更高的时钟负载将导致更高的时钟偏差。由于采用流水线,就增加了信号的等待时间,这对其他的微结构也会产生影响。

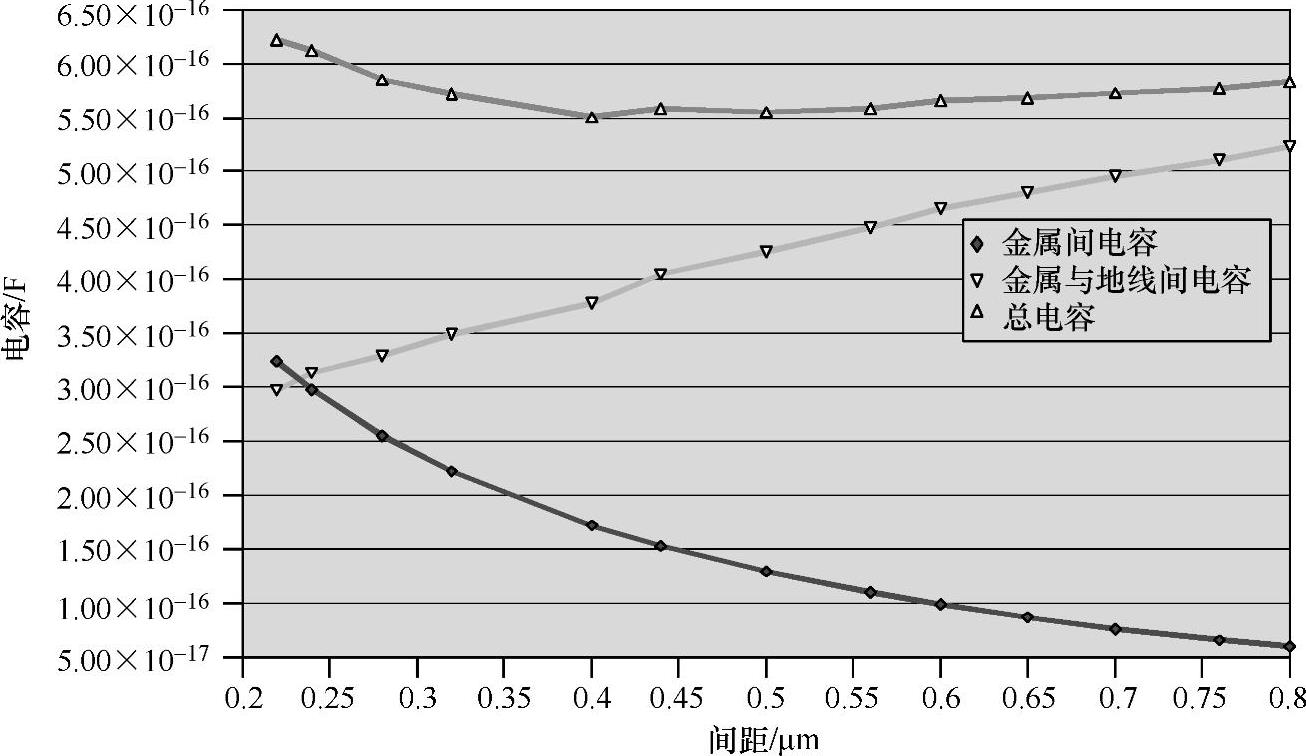

这些问题迫使设计者只好放宽节距,以改善全局互连线的性能和信号完整性。增加互连的节距可以减小线间耦合,但是电容将逼近渐进值,即随着互连线之间间距的进一步增大,电容将不再会随之减小(见图1-10)。使得电容为最小时的间距还与层间介质的厚度有关。工艺技术进一步缩小到小于130nm节点时,由于性能问题和信号完整性问题,互连密度几乎不会得到改善,这将要求对一些互连需要采取屏蔽措施,而对另外一些互连需要增大互连之间的间距。这样,对复杂芯片进行布线,会要求采用更多的金属层。

图1-10 金属-金属电容与间距的关系

接触孔和通孔不能进一步缩小 对大多数130nm技术来说,接触孔尺寸已经是0.16μm,而通孔尺寸是0.2μm。在未来的工艺中,很难使它们缩减得更多,它们将不能与其他特征尺寸一样以相同的速率缩小。另一个限制因素是接触孔和通孔电阻,随着接触孔和通孔尺寸的缩小,电阻将上升。

130nm节点中,接触孔和通孔这两层已经要求采用光学邻近修正(Optical Proximity Correction,OPC)和相移光刻。这些层掩膜版的数据以及掩膜版制作费用已经是其他不需要OPC和/或相移层次的两倍[5]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。