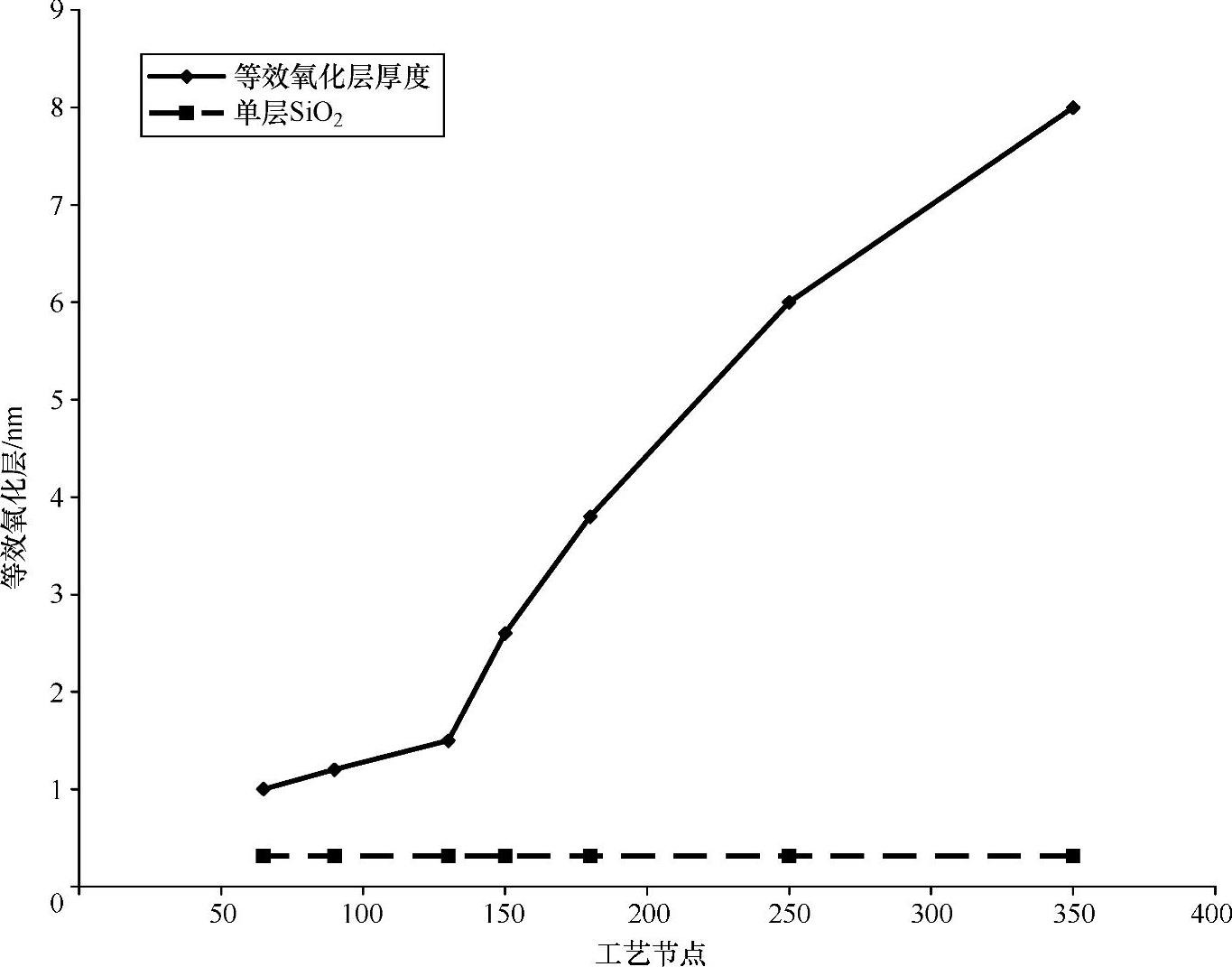

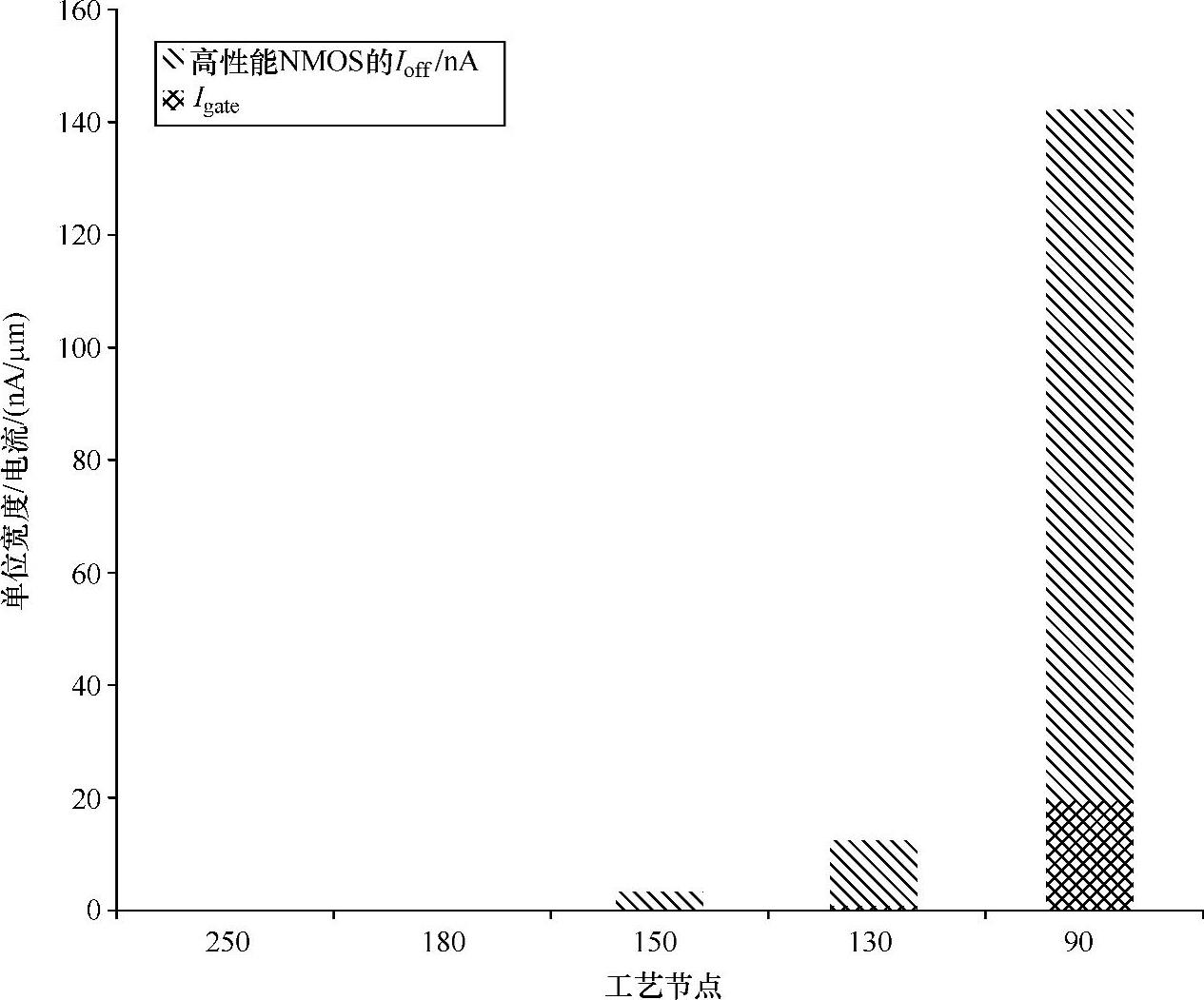

随着工艺特征尺寸缩小到100nm节点以下,对于硅集成电路,为了满足功能和高成品率的要求,需要针对工艺波动的增加、互连工艺的困难和其他一些新出现的更严重的物理效应,改变传统的设计方法。纳米CMOS中栅氧的减薄(见图1-1)致使栅直接隧穿电流急剧增加。亚阈区泄漏和栅直接隧穿电流(见图1-2)不再是二级效应了[1,15]。设计中将要考虑栅感应漏极泄漏(Gate-Induced Drain Leakage,GIDL)的影响。例如对于DRAM(第7章)和低功耗SRAM(第9章),它们的栅压相对于源极来说是负电位[15],如果不考虑这些效应,得到的SRAM、DRAM或者任何其他使用这个技术来减小亚阈区泄漏的电路会丧失功能。某些情况下甚至多路器和触发器也会受到影响。

图1-1 栅氧厚度随工艺节点的变化趋势

图1-2 Igate和亚阈区泄漏随工艺节点的变化趋势(https://www.xing528.com)

在功能级需要面对的问题不仅仅是亚阈区泄漏和栅电流,还需要应对高性能电路,如微处理器、数字信号处理器和图形处理单元等芯片中的电源管理问题。电源管理也是移动应用中需要面对的一个挑战。

另外,即使采用增强分辨率扩展技术(Resolution Extension Technology,RET),光刻也会趋于极限。这些新的光刻技术还会使掩膜版费用增加,并且使生产周期更长。经过几次修改才能得到一个值得进行生产的设计,这将明显增加研制费用。过去,处理器设计者一般在验证置信度达到98%时就可以提交设计数据,在随后的工艺过程中还可以继续排错,这样一般能够使产品的研制速度快几个数量级,从而使产品投放到市场的时间更快。现在,由于掩膜费用的增加和制造周期变得更长,在获得最低的研制成本和以最短的时间将产品投放市场之间进行折衷,将会相当困难[28]。

因为设计规则不能以相同的速率缩小,原先成功的设计在下一代工艺中必须完全重新设计,除非设计者可以预见设计规则的变化,并且在针对原先尺寸较大的工艺技术进行设计时就有意识地牺牲密度以便在下一代工艺技术中可以缩小设计而无需重新设计物理版图。但是仍然必须对关键电路进行再次仿真。如果设计者使用易于缩小的电路技术,也能实现版图的最小化。为此需要预先的计划以及对设计规则进行折衷从而获得一个可以缩小的设计,所以,可以通过工艺缩小以及很少的重新设计(如果需要的话),采用中等的投入提升性能,获得一个速度更快、面积更小的芯片。预测设计规则变化趋势的关键是要对工艺难点和工具设备的制约具有充分的理解,这将会在以后几章中详细讨论。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。