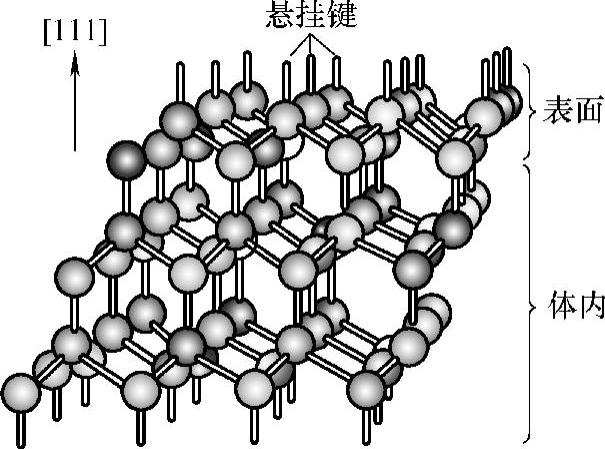

表面复合是指通过半导体表面态进行的复合现象[2]。所谓表面态,是指在晶体与真空之间的分界面,由于晶体结构在表面突然中断,因此在表面区域产生了许多局部的能态,或是产生复合中心,这些称为表面态(surface states)的能态。图4.8所示为半导体表面悬挂键示意图。表面态会大幅度增加在表面区域的复合率。表面或晶界的局域态缺陷包括:

1)悬挂键引起的晶体缺陷。

2)晶体生长过程中在界面或表面沉积的非本征杂质。

图4.8 半导体表面悬挂键示意图

表面复合的快慢通常用表面复合率Us来表示。所谓表面复合率,是指单位时间内通过单位表面积复合掉的电子-空穴对数目。实验发现,表面复合速率Us与表面处非平衡少子的浓度成正比,则在p型和n型半导体的表面,表面复合率分别为(https://www.xing528.com)

Up_s=Se (n-n0)

Un_s=Sh (p-p0)

式中 Se,Sh——分别代表电子和空穴的表面复合速度。表面复合速度很大程度上受到晶体表面物理性质和外界环境的影响。对于任何半导体器件而言,较高的表面复合速度会使更多的载流子在表面复合消失,以致严重地降低器件的性能。因而,对大多数半导体器件而言,总是希望能获得良好的表面,以降低表面复合速度,提高器件的性能。

对于太阳电池材料而言,非平衡少子的寿命受到材料表面态的影响非常大。例如,线切割后的Si晶圆,其表面粗糙度大,少子寿命很短;而进一步经过化学抛光处理后的Si晶圆,其少子寿命较未经过处理的样品长很多。实验还表明,对于同样的表面情况,实半导体材料的少子寿命同样也受到样品大小和形状的影响,即样品越小,寿命越短。可见,半导体表面确实有促进复合的作用。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。