中继终端上的功率消耗主要来自以下模块:收发机的射频前端、基带处理单元(包括存储保持)、高层协议处理和屏幕/键盘等外设。本节将对这些模块的功耗进行估计和分析。

5.5.3.1 射频前端功耗

除了在5.5.2节说明的信号处理单元的处理负荷外,中继的射频前端也受限于如下的因素:

●PAPR。WCDMA信号具有较高的峰均功率比(PAPR),这是因为QPSK调制信号在经过滤波器后表现出非恒包络特性。PAPR的数值取决于在载频上同时发送使用的码字数。PAPR的数值越高,对于功放的线性度要求就越严格,以防止信号被削波和压缩。

●信号动态范围。CDMA系统需要高的功率输出变化范围,主要是考虑消除远近效应而进行的功率控制的需要。

●FDD操作。假定在FDD全双工模式下,收发机同时工作,为了分离发送和接收码片集以降低干扰,需要的滤波器损耗要远高于TDD系统。另外,双工器的发送和接收隔离应不小于50dB。

●中继频段。辅助中继可转发多个FDD传输连接,而协同中继可以在一个FDD连接上传输自身数据,而在另外一个连接上传输中继数据。但不管哪种情况,中继都需要支持多个频段的射频收发传输。

一个典型的UMTS FDD射频收发机,采用380 MHz(发送链路)和190 MHz(接收链路)中频的超外差结构。在这样的接收机结构中,通过中频SAW滤波器和基带模拟滤波器的共同作用,一般可以达到5 MHz信道带宽下33 dB的邻信道选择抑制,而输出功率的动态变化分布在整条发送链路上。中频频率选择190 MHz的倍数,收发机需要一个本地振荡器进行射频的上下变频。另外还需要一个振荡器用于I/Q调制解调,称为中频振荡器。然而,这样的硬件结构是比较复杂的,需要大量外部组件和多级处理(镜像抑制、上下变频、中频处理、I/Q处理等),从而导致功耗升高、电池持续时间缩短。这种结构一般在生产厂家需要将产品迅速推入市场的情况下使用。

为了更好地集成,可以在接收链路上使用直接下变频,而发送链路采用超外差结构(IF=190 MHz)。事实上,接收链路设计的趋势是直接下变频,除了有一些结构上的限制外(直流偏移、ADC有较宽的带宽、增益基本决定于基带放大等),对于高集成度、功耗和成本方面都是能带来益处的。这方面一些技术方法还是可行的,比如使用高通滤波器来解决直流偏移的问题,带来的系统性能损失对于宽带信号还是可以接受的。关于WCDMA直接下变频接收机设计方面,已经有很多发表的论文[522-527]。在这种结构下,如果发送链路也采用190 MHz的中频的话,只需要一个射频振荡器就可以支持上下变频处理。

为了获得功耗的估计,我们假定:

●整个发送链路的射频滤波器(双工滤波器和双工器)的插入损耗为约3.5 dB。

●90%的发送时间内,最大功率Pout=21 dBm。

●平均接收链路损耗为PRx=85 mW[523]。

●平均接收链路损耗为PTx=215 mW[523]。

●ADC平均功耗为60 mW,DAC为30 mW。

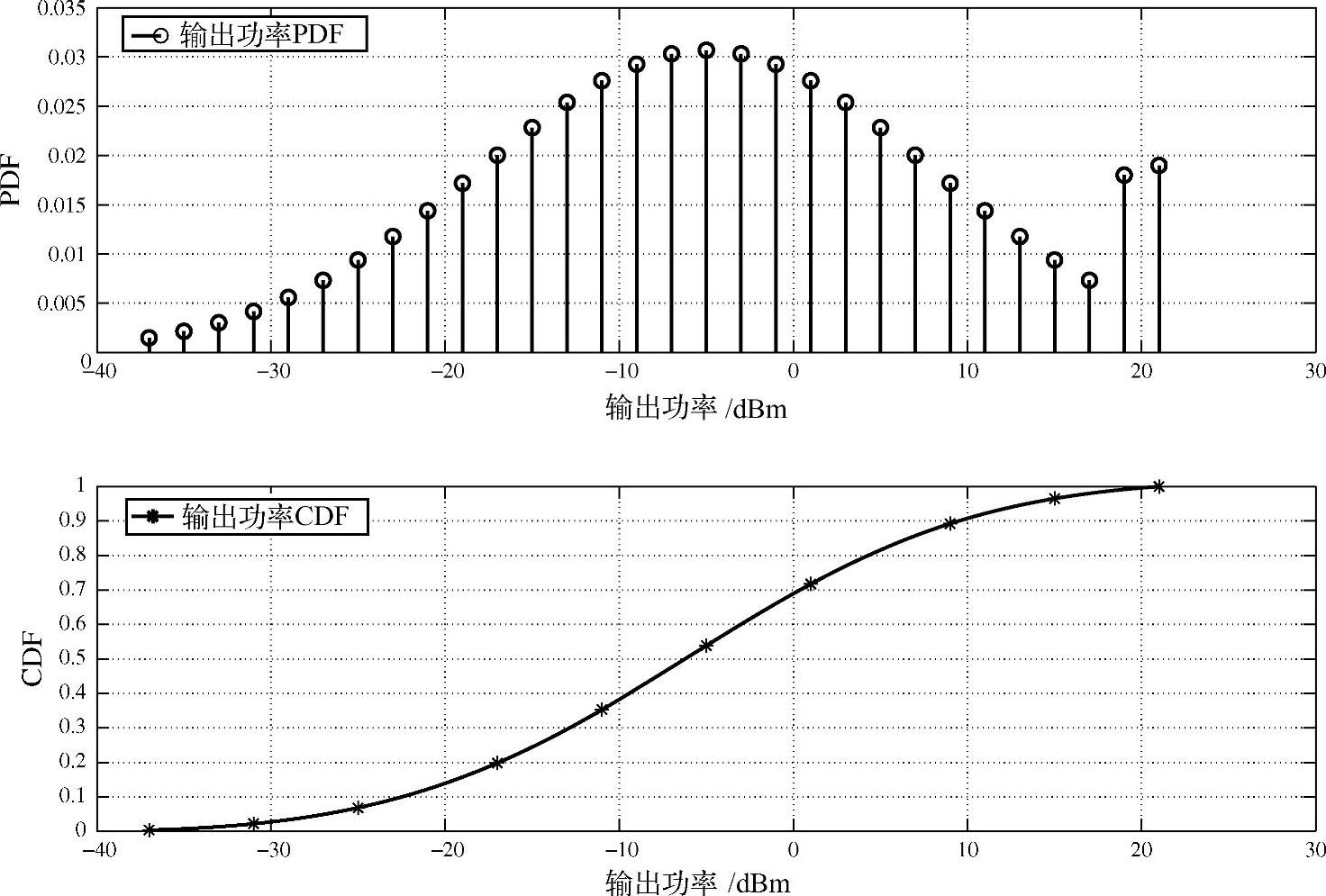

Raju在文献[518]中经过严格定量分析得出,射频前端的功耗与发射功率分布特性紧密相关。而功率分布依赖于UMTS业务、数据速率、通信环境等因素。为了简化研究,我们假定功率服从如图5.8所示的高斯分布特性[529]。发射功率限定为最大21 dBm是考虑到功控的饱和。需要注意的是,下面的分析过程可以用于其他复杂的分布模型[528]。

图5.8 典型的射频输出功率的概率及累积分布[529](https://www.xing528.com)

图5.8给出了功率输出的PDF和CDF曲线,从中我们可以得出90%的发射时间内的平均输出功率为10dBm。给定插入损耗为3.5dB,放大器需要输出功率为13.5dBm,相当于22.4mW。对于这样的输出功率,功放有效性是比较低的,只有6%[530]。要注意的是,在最大发射功率21dBm时,功放的有效性是很高的,可以达到40~50%。然而,如果是6%的平均有效性下,平均功率输出需要为22.4mW/0.06=373mW。

之前说过,调制信号的PAPR的值依赖于在同一载频上发送的码字数量;为了评估功放的输出饱和功率,需要考虑最差的情况:用户传输速率384kbit/s,3个码字同时使用,发射用最大功率。在这种情况下,PAPR的值估计为4.5dB[525],所以功放的输出饱和功率因此应至少为21dBm+4.5dBm=25.5dBm。

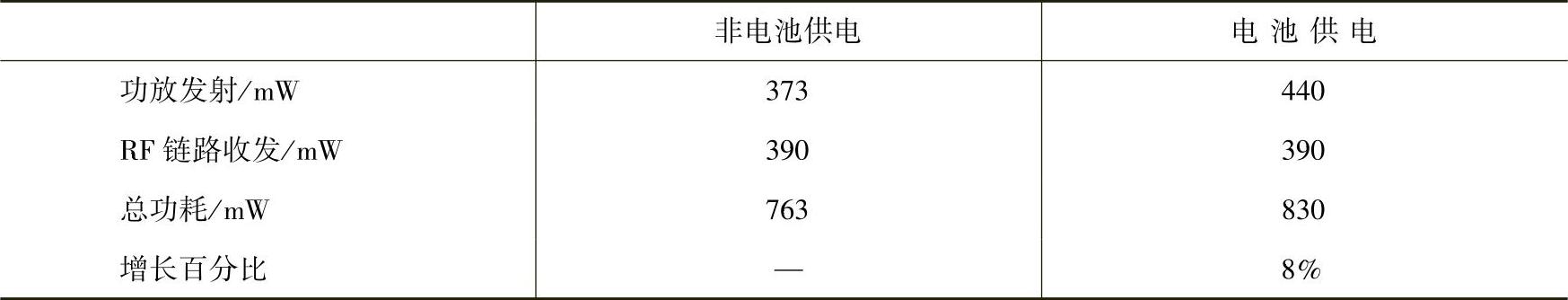

在一些情况下,例如协同中继作为一个终端也需发送自身数据,这时中继是通过电池供电的。此时存在的问题就是如何保持功放输出电压为一个常量,因为电池电压往往会随时间的变化呈非线性变换。这时电压稳压器就显得很重要了,它的效率一般为85%。功放的总功耗因此也会提高到373mW/0.85=440mW。

除了功放的消耗外,射频收发链路上也会消耗一部分功率。假定发送链路功率消耗为215mW,再加上DAC的30mW;接收链路平均功耗为85mW,ADC平均功耗为60mW。因此一个单发单收系统的总平均功率消耗(不包括功放)是390mW。

射频收发机的功耗在表5.7中总结出来,这些数值是与数据速率,以及出厂时间无关的。要注意的是,当使用多个FDD链路时,应在这些值上乘以一个所使用的FDD链路数量。同样,当在中继上增加收发机天线时,推导过程是类似的。

表5.7 一个非电池供电和电池供电的UMTS中继的典型RF功耗

5.5.3.2 数字基带的功耗

基带的功率消耗主要来自于运算操作和数据在内存的保持。功耗的大小与技术的复杂性有关,表5.8中给出了一个相应的预计[520]。这给了我们一个基带功率消耗估计的参考,基带功耗主要包括如下因素:

●内存内容保持。通过当前的数据手册可以确认,射频链路的功耗要远大于内存内容保持所消耗的功率。因此,可以将这部分功耗忽略。

●运算处理器操作。针对数字处理器的功耗,已经建立了很多模型来表示指令数和功耗间的关系,且功耗分为静态功耗和动态功耗两部分。静态功耗一般为动态功耗的10%,因此在这里的分析中忽略。动态功耗一般以mW/Mips为单位,表5.8中已给出,根据其预测的2011年的DSP功耗为0.01mW/Mips,以及由5.5.2节给出的运算次数估计,我们可以得出基带算法的功耗:将前面求得的算法复杂度除以106后即可获得每秒指令执行数(Mips),然后再乘以0.01mW/Mips。注意所得的功耗是每条指令而不是每个时钟周期。从5.5.4节给出的数值能看出,基带的功耗与射频链路相比完全可以忽略。因此,可以忽略处理器运行带来的功耗部分。

●存取操作。处理器的Load/Store操作带来的功耗是不能忽略的。因为结合内存和处理器的数据总线系统表现出一个电容特性,电容值在表5.8中给出。为了获得所消耗的功耗,一个通用的方法是将每个存储比特都建模为一个工作在3V电压的电容Cin=3pF(2011年)。那么每个时隙的平均功耗为1/2×8×Cin×V2×f,这里8是指每字节的位数,f是Load/Store操作的频率,其值等于5.5.2节得到的 除以时隙的长度。在后面章节,我们将结合具体情况来定量分析。

除以时隙的长度。在后面章节,我们将结合具体情况来定量分析。

表5.8 数字基带的功耗估计

必须明确的是,上述各部分的功耗与选择的硬件结构密切相关,所以计算在未来应用中的功耗估计是非常困难的。但是,这些定性和定量的趋势分析至少可以粗略估计出数字基带调制解调器的功耗。

5.5.3.3 高层协议和外围器件

位于法国格勒诺布尔的法国电信R&D实验室在对一台单天线的UMTS终端进行了测量后,指出多媒体屏幕、键盘、LED、语音放大器和高层协议的功耗大约为600mW。我们希望这个值在2011年前能有所降低,也希望增加其他功能和外围后这个值能基本不变。因此,对于协同中继场景中,所需的高层算法(MAC、RRM、应用程序等)和外围硬件(多媒体屏幕、键盘等)的功耗也估算为约600mW。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。