实现位同步的方法也和载波同步类似,可分为插入导频法和直接法两类。这两类方法有时也分别称为外同步法和自同步法。

基带信号若为随机的二进制不归零脉冲序列,那么这种信号本身不包含位同步信号。为了获得位同步信号,就应在基带信号中插入位同步导频信号,或者对该基带信号进行某种变换。

1.插入导频法

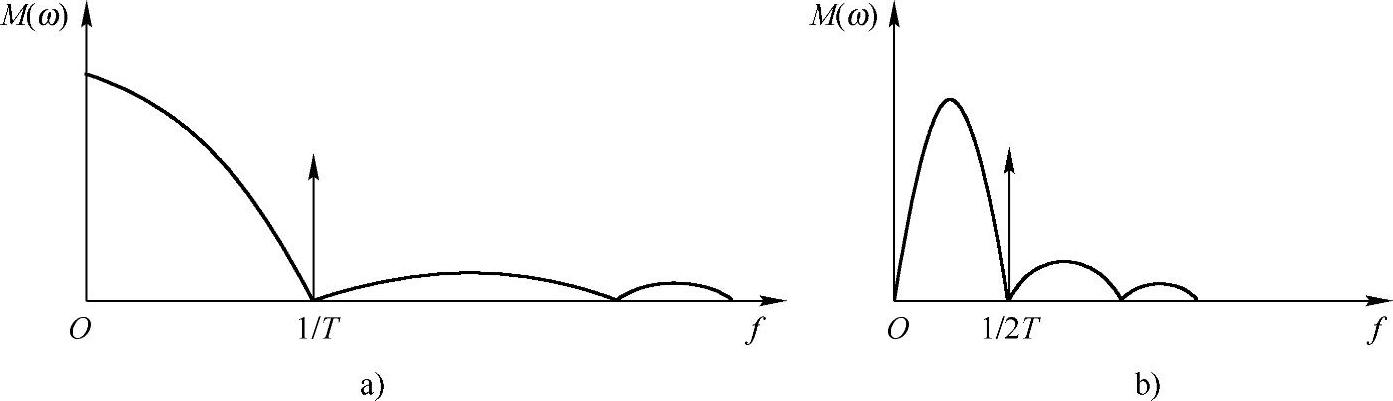

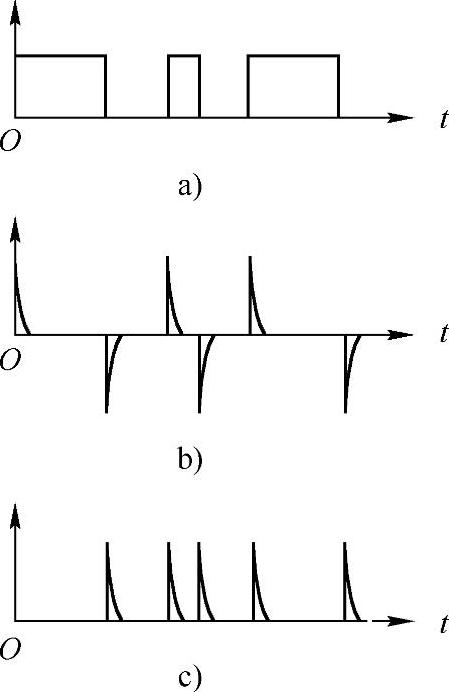

插入导频法与载波同步时的插入导频法类似,它是在基带信号频谱的零点插入所需的导频信号,如图5-4a所示。若经某种相关编码的基带信号,其频谱的第一个零点在f=1/2T处时,插入导频信号就应在1/2T处,如图5-4b所示。

图5-4 插入导频法频谱图

在接收端,对图5-4a所示的情况,经中心频率为f=1/T的窄带滤波器,就可从解调后的基带信号中提取出位同步所需的信号,这时,位同步脉冲的周期与插入导频的周期是一致的;对图5-4b所示的情况,窄带滤波器的中心频率应为1/2T,因为这时位同步脉冲的周期为插入导频周期的1/2,故需将插入导频倍频,才得到所需的位同步脉冲。插入导频法的另一种形式是使数字信号的包络按位同步信号的某种波形变化。

在相移键控或频移键控的通信系统中,对已调信号进行附加的幅度调制后,接收端只要进行包络检波,就可以形成位同步信号。

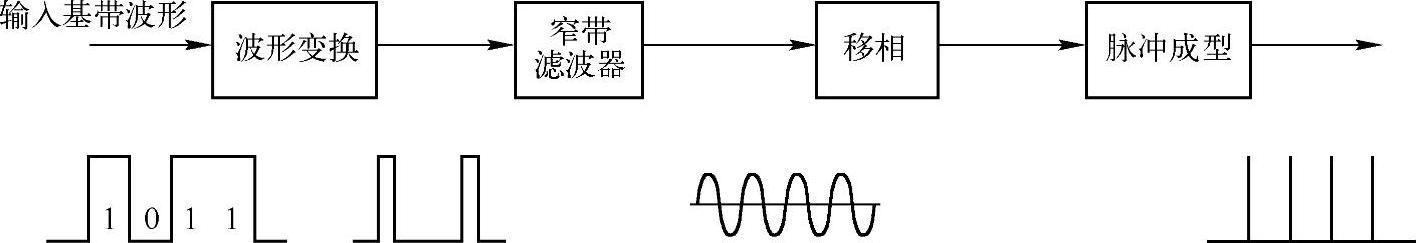

设相移信号的表示式为

s1(t)=cos[ωct+ϕ(t)] (5-17)

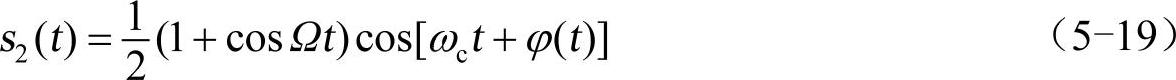

现在用某种波形的位同步信号对s1(t)进行幅度调制,若这种波形为升余弦波形,则其表达式为

式中,Ω=2π/T,T为码元宽度。幅度调制后的信号为

接收端对s2(t)进行包络检波,包络检波器的输出为 ,除去直流分量后,可获得位同步信号

,除去直流分量后,可获得位同步信号 。

。

以上载波同步和位同步中所采用的导频插入法都是在频域内的插入。事实上,同步信号也可以在时域内插入,这时载波同步信号、位同步信号和数据信号分别被配置在不同的时间内传送。接收端用锁相环路提取出同步信号并保持它,就可以对随之而来的数据进行解调了。

2.直接法

直接法是发送端不专门发送导频信号,而直接从数字信号中提取位同步信号的方法。这是数字通信中经常采用的一种方法。

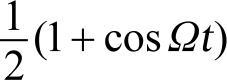

(1)滤波法

我们知道,对于不归零的随机二进制序列,不能直接从其中滤出位同步信号。但是,若对该信号进行某种变换,例如,变成归零脉冲后,则该序列中就有f=1/T的位同步信号分量,其大小可算出。经一个窄带滤波器,可滤出此信号分量,再将它通过一移相器调整相位后,就可以形成位同步脉冲。这种方法的原理框图如图5-5所示。它的特点是先形成含有位同步信息的信号,再用滤波器将其滤出。下面介绍几种具体的实现方法。

图5-5 滤波法原理框图

图5-5原理图中的波形变换,在实际应用中可以是一个微分、整流电路,经微分、整流后的基带信号波形如图5-6所示。这里,整流输出的波形与图5-5中波形变换电路的输出波形有些区别,这个波形同样包含有位同步信号分量。

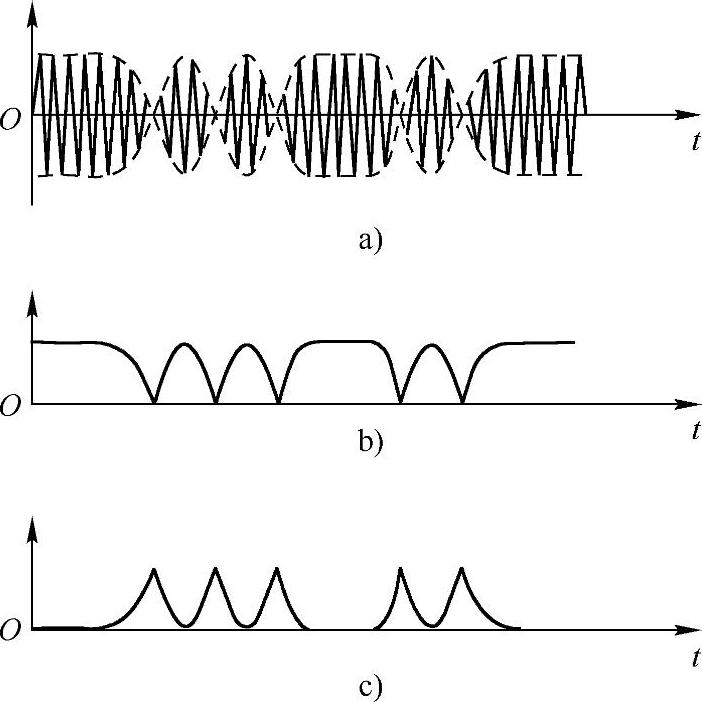

另一种常用的波形变换方法是对带限信号进行包络检波。在某些数字微波中继通信系统中,经常在中频上用对频带受限的二相移相信号进行包络检波的方法来提取位同步信号。频带受限的二相PSK信号波形如图5-7a所示。因频带受限,在相邻码元的相位变换点附近会产生幅度的平滑“陷落”。经包络检波后,可得图5-7b所示的波形。可以看出,它是一直流和图5-7c所示的波形相减而得到的,因此包络检波后的波形中包含有如图5-7c所示的波形,而这个波形中已含有位同步信号分量。因此,将它经滤波器后就可提取出位同步信号。

图5-6 基带信号微分、整流波形

图5-7 频带受限2PSK位同步信号提取(https://www.xing528.com)

(2)锁相法

位同步锁相法的基本原理和载波同步法类似。在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。前面讨论的滤波法原理图中,窄带滤波器可以是简单的单调谐回路或晶体滤波器,也可以是锁相环路。

把采用锁相环来提取位同步信号的方法称为锁相法。下面介绍在数字通信中常采用的数字锁相法提取位同步信号的原理。

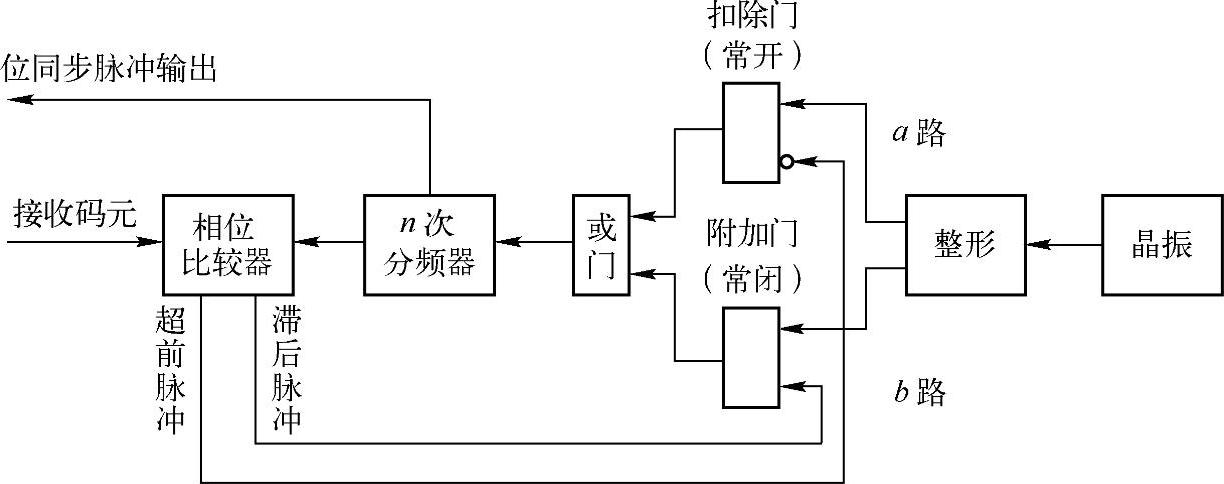

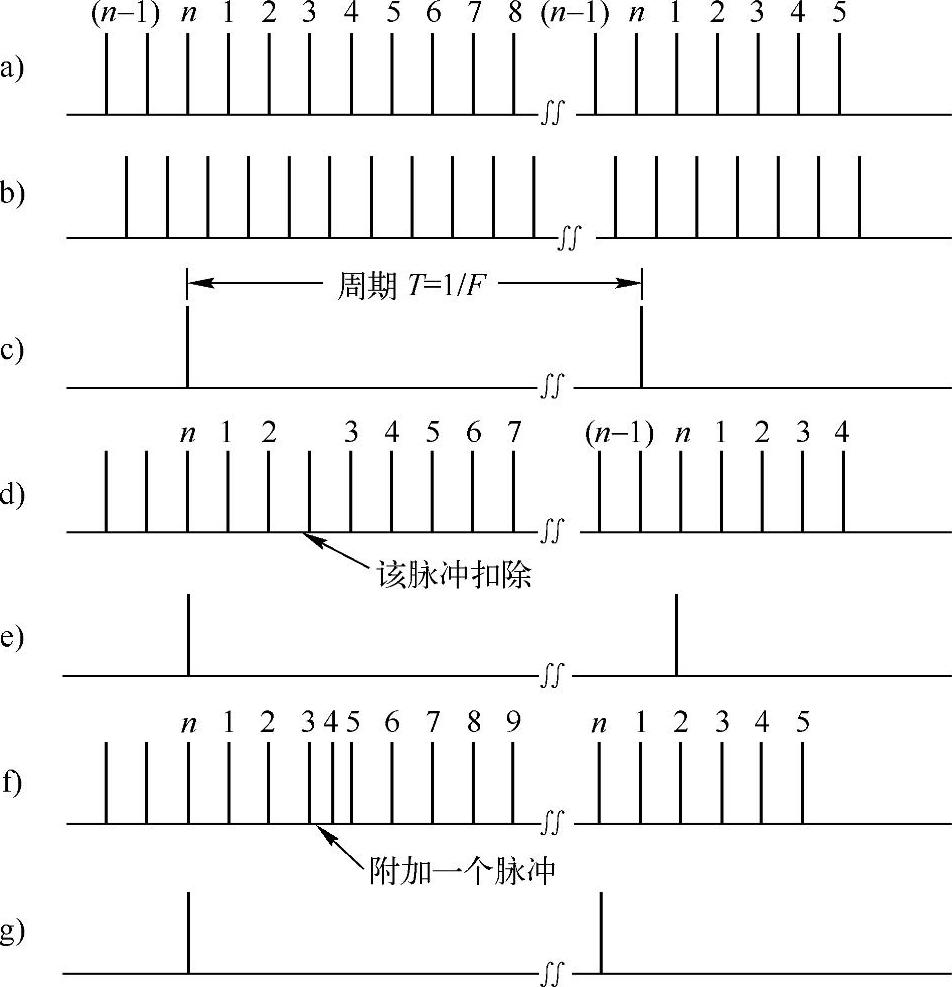

数字锁相的原理框图如图5-8所示,它由高稳定度振荡器(晶振)、分频器、相位比较器和控制器组成。其中,控制器包括图中的扣除门、附加门和“或门”。高稳定度振荡器产生的信号经整形电路变成周期性脉冲,然后经控制器再送入分频器,输出位同步脉冲序列。若接收码元的速率为F(Baud),则要求位同步脉冲的重复速率也为F(Hz)。这里,晶振的振荡频率设计在nF(Hz),由晶振输出经整形得到重复频率为nF(Hz)的窄脉冲(见图5-9a),经扣除门、或门和n次分频器后,就可得到重复频率为F(Hz)的位同步信号(见图5-9c)。

图5-8 数字锁相的原理框图

如果接收端晶振输出经n次分频后,不能准确地和收到的码元同频同相,这时就要根据相位比较器输出的误差信号,通过控制器对分频器进行调整。调整的原理是当分频器输出的位同步脉冲超前于接收码元的相位时,相位比较器送出一超前脉冲,加到扣除门(常开)的禁止端,扣除一个a路脉冲(见图5-9d),这样,分频器输出脉冲的相位就推后1/n周期(360o/n),如图5-9e所示;若分频器输出的位同步脉冲相位滞后于接收码元的相位,如何对分频器进行调整呢?晶振的输出整形后除a路脉冲加于扣除门外,同时还有与a路相位相差180o的b路脉冲序列(见图5-9b)加于附加门。附加门在不调整时是封闭的,对分频器的工作不起作用。当位同步脉冲相位滞后时,相位比较器送出一滞后脉冲,加于附加门,使b路输出的一个脉冲通过“或门”,插入在原a路脉冲之间(见图5-9f),使分频器的输入端添加了一个脉冲。于是,分频器的输出相位就提前1/n周期(见图5-9g)。经这样的反复调整相位,就实现了位同步。

图5-9 位同步脉冲的相位调整

(3)超前-滞后门同步器

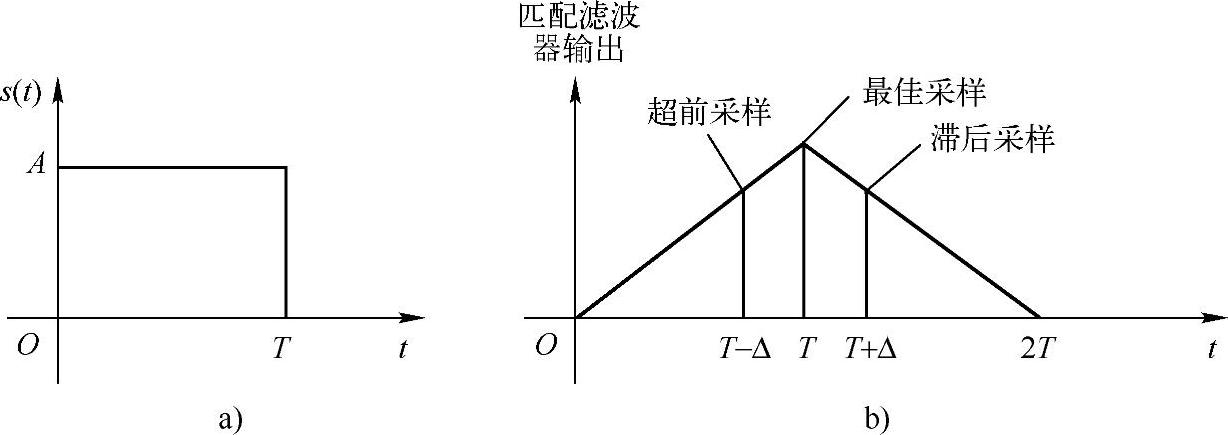

超前-滞后符号同步算法利用的是信号波形的对称性,即经过匹配滤波器或相关器后,输出信号是对称的,如图5-10所示。对于图5-10a所示的矩形脉冲,匹配滤波器的输出在t=T时达到最大值,如图5-10b所示。只要采样值在峰值上,就一定能够保证符号同步。

图5-10 超前-滞后门波形示意图

a)矩形信号脉冲 b)匹配滤波器输出

在噪声存在的情况下,如果没有在峰值点对信号采样,而在t=T-Δ时超前采样,在t=T+Δ时滞后采样。那么由于自相关函数对于最佳采样时刻t=T是偶函数,超前采样值的绝对值和滞后采样值的绝对值就相等。在这种条件下,适当的采样时刻应该是在t=T-Δ和T+Δ的中间。这一条件构成了超前-滞后门同步器的基础。

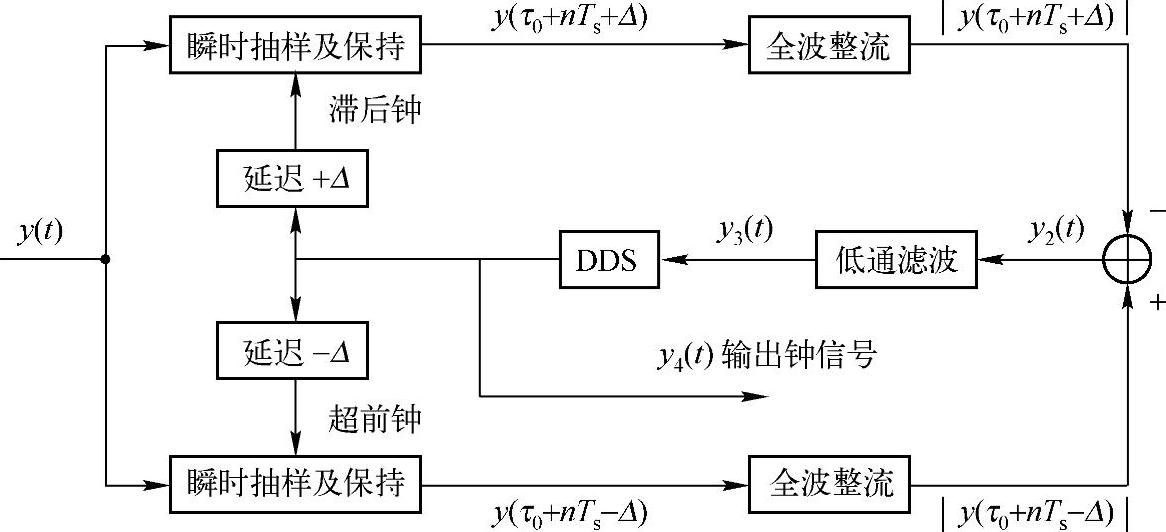

超前-滞后门同步器的结构如图5-11所示。

图5-11 超前-滞后门同步器的结构示意图

下面对其进行简单的说明。

根据信号的特点,信号的波形是对称于最佳采样时刻的。本方法是利用信号脉冲波形对称性的特点来进行符号同步的。在图5-11中,用y(t)表示接收滤波器的输出信号波形,假设在眼图张开到最大时进行采样,即在最佳时刻进行采样,得到的采样值为y(τ0+nTs),τ0是最佳定位相位。

设∆是偏离于最佳采样时刻的偏离值,如图5-11所示,在偏离值为∆的两个采样时刻是相等的,一个为超前采样,用y(τ0+nTs-Δ)表示;另一个为滞后采样,用y(τ0+nTs+Δ)表示,即

|y(τ0+nTs-Δ)|≈|y(τ0+nTs+Δ)|

但是在未同步时的采样相位τ≠τ0,此时的超前采样为y(τ0+nTs-Δ),滞后采样为y(τ+nTs+Δ),分别将它们全波整流,得到|y(τ0+nTs-Δ)|及|y(τ0+nTs+Δ)|。再将两者相减,得到

y2(t)=|y(τ0+nTs-∆)|-|y(τ0+nTs+∆)|

再将y2(t)经过低通滤波,相当于对y2(t)进行时间平均,得到输出y3(t)。

将y3(t)送给DDS,控制DDS的频率。若DDS产生的时钟是最佳定位相位,即τ=τ0,则y3(t)为0;若τ超前于τ0,则y3(t)是负值;若τ滞后于τ0,则y3(t)是正值。正的控制电压将增加DDS的频率,负的电压将减小DDS的频率。在符号同步时,DDS将输出时钟信号,同步于接收信号的符号速率。注意,该电路要避免输入数据全“1”或“0”的情况。

基于超前-滞后门的符号同步算法在无线通信信号处理中获得了广泛应用,下面我们就以此为例,用MATLAB进行实现,以期加深读者的理解。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。