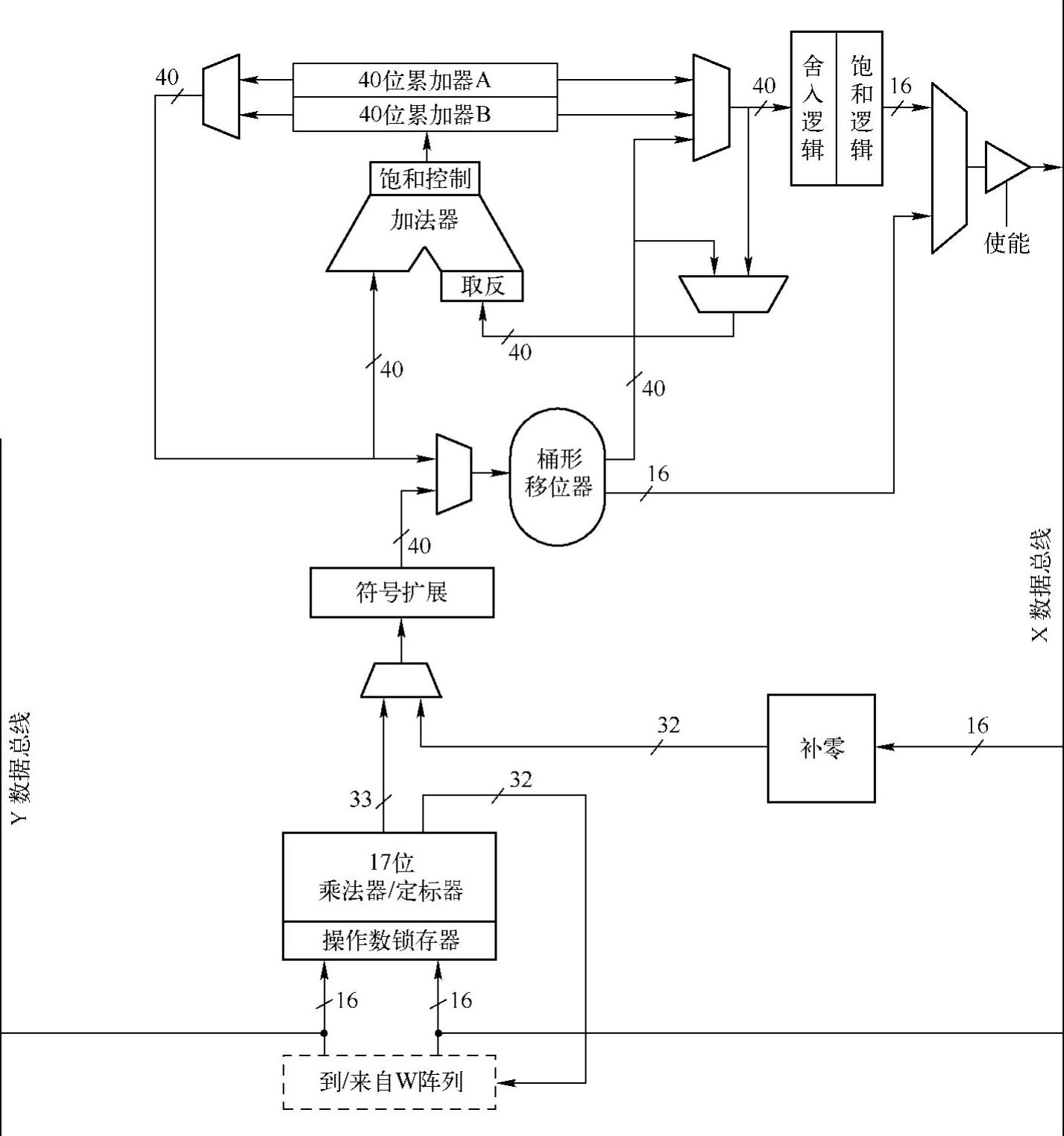

DSP引擎由一个高速的单周期17×17位乘法器、一个桶形移位寄存器、一个带有两个目标累加器的40位加法器/减法器以及舍入与溢出逻辑组成,该模块的输入数据来自于工作寄存器W4、W5、W6、W7或者X存储器区,输出数据送到DSP指令定义的目标累加器中或者X存储器区中。DSP指令可以无缝地与所有其他指令一起操作,其设计可实现最佳的实时性能。MAC指令和其他相关指令可在同一个周期内,同时完成从存储器中取出两个数据操作数、将两个工作寄存器相乘并进行累加的操作。DSP引擎能够执行固有的“累加器—累加器”的操作而无需额外数据,这些指令包括ADD、SUB和NEG等。该功能大大简化了32位或40位数据的算术运算。DSP引擎的内部结构如图1-5所示。

图1-5 DSP引擎的内部结构图

17×17位乘法器可进行有符号或无符号运算。对输出进行适当调整可以支持1.31小数(Q31)或32位整数结果,无需在运算后手工处理小数乘法运算的结果。

40位加法器/减法器可以选择两个累加器(A或B)之一作为保持运算后的结果,对于ADD指令和LAC指令,可选择通过桶形移位器在累加之前对将被累加或装入的数据进行调整。加法器/减法器产生溢出状态位SA/SB和OA/OB,这些位在状态寄存器中,它也可以选择性地产生算术错误陷阱。

桶形移位寄存器在单个周期内可完成16位的算术右移或左移。DSP指令或MCU指令都可实现桶形移位器的多位移位。移位器需要一个带符号的二进制值确定移位操作的幅度(位数)和方向,具体规则如下:(https://www.xing528.com)

●若为正值则将操作数右移。

●若为负值则将操作数左移。

●若值为“0”则不改变操作数。

桶形移位器的宽度与累加器相同,都是40位,为DSP移位操作提供了40位输出结果,为MCU移位操作提供16位结果。

DSP引擎还有一个舍入与溢出逻辑控制模块,可以控制累加器的数据饱和。该模块通过加法器的运算结果、状态位和用户设置的控制位来决定运算是否溢出,以及什么值会溢出,另外该模块还可以判断对数据空间进行写操作的溢出。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。