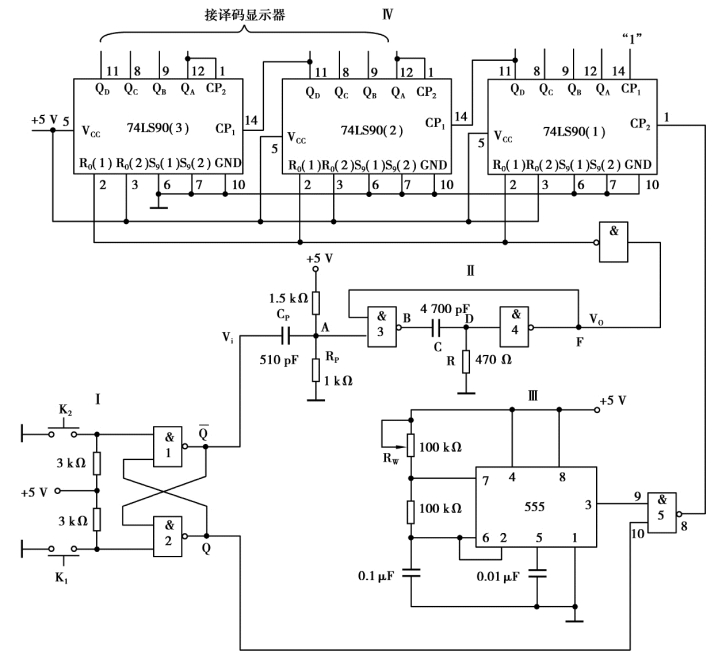

如图5.7.1 所示为电子秒表的电路原理图。按功能分成4 个单元电路进行分析。

图5.7.1 电子秒表原理图

1)基本RS 触发器

基本RS 触发器在电子秒表中的功能是启动和停止秒表的工作。

2)单稳态触发器

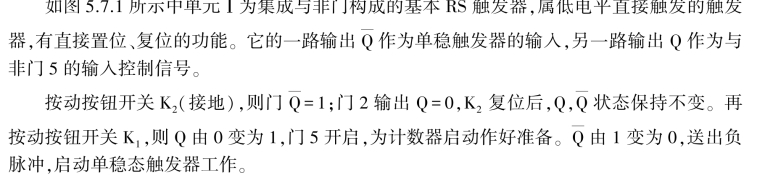

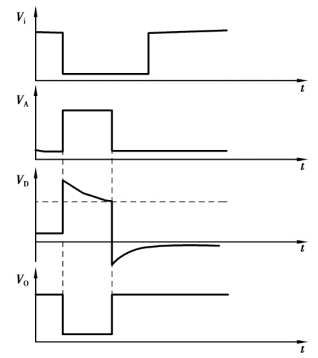

如图5.7.1 所示中单元Ⅱ为用集成与非门构成的微分型单稳态触发器,如图5.7.2 所示为各点波形图。

静态时,门4 应处于截止状态,故电阻R 必须小于门的关门电阻Roff。定时元件RC 取值不同,输出脉冲宽度也不同。当触发脉冲宽度小于输出脉冲宽度时,可以省去输入微分电路的RP和Cp。

单稳态触发器在电子秒表中的功能是为计数器提供清零信号。

3)时钟发生器

如图5.7.1 所示中单元Ⅲ为用555 定时器构成的多谐振荡器,是一种性能较好的时钟源。

调节电位器Rw,在输出端3 获得频率为50 Hz 的矩形波信号,当基本RS 触发器Q =1 时,门5 开启,此时50 Hz 脉冲信号通过门5 作为计数脉冲加于计数器(1)的计数输入端CP2。

4)计数及译码显示

二-五-十进制加法计数器74LS90 构成电子秒表的计数单元,如图5.7.1 所示中单元Ⅳ所示。其中计数器(1)接成五进制形式,对频率为50 Hz 的时钟脉冲进行五分频,在输出端Q0取得周期为0.1 s 的矩形脉冲,作为计数器(2)的时钟输入。计数器(2)及计数器(3)接成8421码十进制形式,其输出端与实验装置上译码显示单元的相应输入端连接,可显示0.1~0.9 s;1~9.9 s 计时。

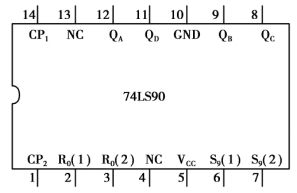

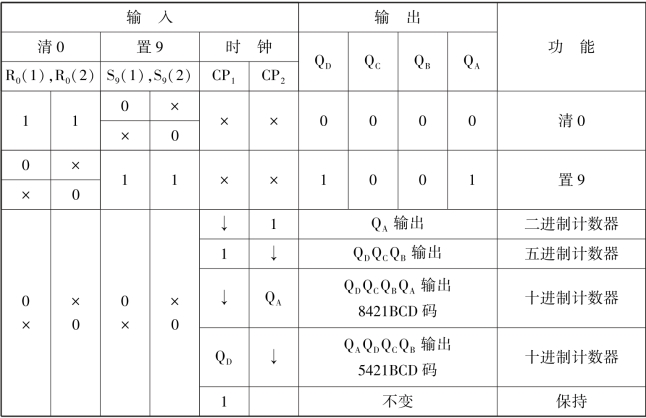

注:集成异步计数器74LS90(https://www.xing528.com)

74LS90 是异步二-五-十进制加法计数器,它既可以作为二进制加法计数器,又可以作五进制和十进制加法计数器。

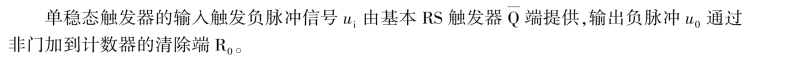

如图5.7.3 所示为74LS90 引脚排列,表5.7.1 为其功能表。通过不同的连接方式,74LS90可以实现4 种不同的逻辑功能,而且还可借助R0(1),R0(2)对计数器清零,借助S9(1),S9(2)将计数器置9。其具体功能详述如下:

①计数脉冲CP1输入,QA作为输出端,为二进制计数器。

②计数脉冲CP2输入,QDQCQB作为输出端,为异步五进制计数器。

③若将CP2和QA相连,计数脉冲由CP1输入,QD,QC,QB,QA作为输出端,则构成异步8421 码十进制加法计数器。

图5.7.2 单稳态触发器波形图

图5.7.3 74LS90 引脚排列

④若将CP1和QD相连,计数脉冲由CP2输入,QA,QD,QC,QB作为输出端,则构成异步5421 码十进制加法计数器。

⑤清零、置9 功能。

a.异步清零。

若R0(1),R0(2)均为1;S9(1),S9(2)中有0 时,实现异步清零功能,QDQCQBQA=0000。

b.置9 功能。

若S9(1),S9(2)均为1;R0(1),R0(2)中有0 时,实现置9 功能,QDQCQBQA=1001。

表5.7.1 74LS90 功能表

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。