【摘要】:3)半加器两个一位二进制的数相加时,有4 种可能情况,见表5.1.4,其中,S 表示和,C 表示进位,A,B 表示加数、被加数。表5.1.4半加器真值表①从表中可写出半加器和S 与进位C 的逻辑表达式:实现上述逻辑表达式的逻辑电路有多种形式。②自行拟订实验电路,并将实验结果与表5.1.4 对照。

1)测试与非门的逻辑功能

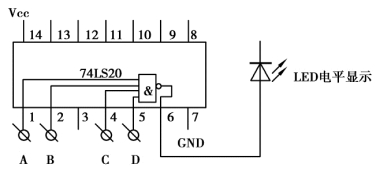

①按如图5.1.4 所示接线。

②按表5.1.2 的要求分别置A,B,C,D 的逻辑状态,并把观测到Q 端的状态填入表中,写出逻辑表达式。

图5.1.4 74LS20 逻辑功能测试图

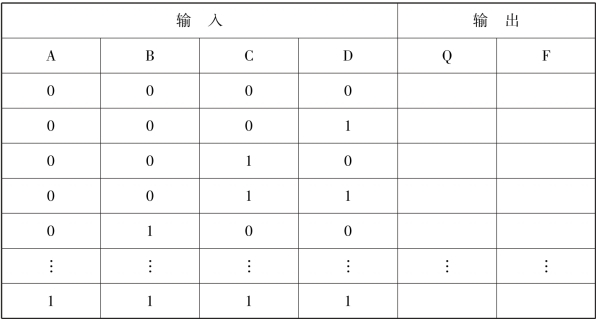

表5.1.2 与非及与或非逻辑真值表

2)利用与非门组成其他基本门电路,测试逻辑功能

(1)组成与门电路

①由与门的逻辑表达式得知![]() 与门可由两个与非门组成,要求画出与门电路,并进行实验。

与门可由两个与非门组成,要求画出与门电路,并进行实验。

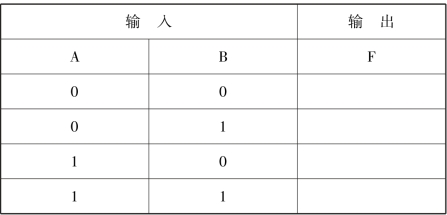

②按表5.1.3 对输入电平要求,把测出的输出结果填入表中相应的栏内。

表5.1.3 与逻辑真值表

(2)组成与或非门电路

①把与或非逻辑式化成用与非表达的形式。

![]() (https://www.xing528.com)

(https://www.xing528.com)

②自行拟订实验电路,并进行实验。

③把实验结果填入表5.1.2 中。

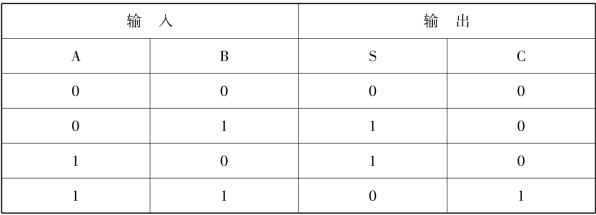

3)半加器

两个一位二进制的数相加时,有4 种可能情况,见表5.1.4,其中,S 表示和,C 表示进位,A,B 表示加数、被加数。

表5.1.4 半加器真值表

①从表中可写出半加器和S 与进位C 的逻辑表达式:

![]()

实现上述逻辑表达式的逻辑电路有多种形式。

②自行拟订实验电路,并将实验结果与表5.1.4 对照。

4)设计一位全加器,要求用与或非门实现

5)设计一个对2 位无符号的二进制数进行比较的电路

根据第一个数是否大于、等于、小于第二个数,使相应的3 个输出端中的一个输出为1,要求用与门、与非门及或非门实现。

实验中需注意以下事项:

①接插集成块时,要认清定位标记,不得插反。

②TTL 与非门使用电源电压为+4.5~+5.5 V,实验中要求使用VCC=+5 V。电源极性绝对不允许接错。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。