绘制原理图的最终目的是要设计出电路板。要设计电路板,就必须建立网络表,对于Allegro Design Entry CIS来说,生成网络表是它的一项特殊功能。在Allegro Design Entry CIS中,可以生成多种格式的网络表,可以满足不同EDA软件的要求。

在使用生成网络表的功能之前,先要确认以下事项。

(1)电路图的元件序号已经完成排序。

(2)电路图已经通过DRC检查。

(3)属性数据已经完整,每个元件的元件封装已经设置完成。

确认完成后,就可以对该电路图生成网络表了。

(1)在项目管理器窗口下,选中预创立网络表的电路图或者是根目录。

(2)单击工具栏按钮![]() ,或者是执行菜单命令“Tools”→“Create Netlist…”,弹出如图6.4-5所示的对话框。选择对应的EDA软件格式,单击“确定”按钮即可生成相应的网络表。

,或者是执行菜单命令“Tools”→“Create Netlist…”,弹出如图6.4-5所示的对话框。选择对应的EDA软件格式,单击“确定”按钮即可生成相应的网络表。

所生成的网络表包括9个标签页,每一个标签页都代表一种网络表格式接口,这里只介绍与“Allegro PCB Editor”的网络表接口设置。

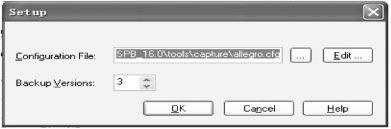

1)PCB Footprint:指定PCB封装的属性名,默认值是“PCB Footprint”。单击“Setup”按钮,弹出对话框如图6.4-6所示。可以进行修改、编辑、查看文件存放位置,这些文件包括“Allegro Design Entry CIS”和“Allegro PCB Editor”之间一系列的属性映射。也可以指定备份类型的数目,以PST*.DAT的网络表文件形式保存。

图6.4-5 “Create Netlists…”对话框

图6.4-6 “Setup”对话框

2)Create PCB Editor Netlist:产生Allegro格式的网络表,包括pstchip.dat、pstxnet.dat和pstxprt.dat。通过选中复选框,就可以在项目管理器或在目录中找到这三个文件,不选复选框,就不会产生网络表,以下的复选框也变成无效。

3)Options。(https://www.xing528.com)

(a)Netlist Files:此项的功能是指定PST*.DAT文件的保存位置,默认的位置为在设计中指定的最后一次调用对话框的目录。如果是第一次生成网络表,默认的位置为设计目录的Allegro子文件,这是首选的位置。如果网络表先于项目产生,则默认的位置为用这个对话框进行设计最后使用的目录。

(b)View Output:此项功能是自动打开3个PST*.DAT文件,当网络表完成后这三个文件会在独立的“Allegro Design Entry CIS”窗口显示,默认选项为空。

4)Create or Update Allegro PCB Editor Board:创建或更新Allegro PCB板的网络表,这个选项可以除去在Allegro中输入逻辑的需要。

5)Options。

(a)Input Board:为创建一个新的输出板放置逻辑图数据。如果没有选择Create or Update Allegro PCB Editor Board选项,则此项为灰。

(b)Output Board:新的电路板文件放置路径,输出板以输入板为模板,且在设计中接受网络表的逻辑数据。

6)Board Launching Option:电路板设计执行选项。

(a)Open Board in Allegro PCB Editor:自动使用Allegro PCB Editor打开电路板文件。

(b)Open Board in Or CAD PCB Editor:自动使用Or CAD PCB Editor打开电路板文件。

(c)Do not open board file:不打开电路板文件。

(3)单击“确定”按钮,生成网络表文件,弹出对话框如图6.4-7所示,提示建立网络表之前是否保存设计,选择“确定”按钮,将会在项目管理器窗口下生成pstchip.dat、pstxnet.dat和pstxprt.dat文件,如图6.4-8所示。

图6.4-7 提示信息对话框

图6.4-8 项目管理器窗口

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。