1.编码器

用文字、符号或数码来表示特定对象或信号的过程,称为编码.如装电话要电话号码,寄信要邮政编码等.实现编码功能的电路称为编码器.

由于十进制编码或某种文字和符号的编码难于用电路来实现,在数字电路中,一般采用二进制编码.二进制只有0和1两个数码,可以把若干个0和1按一定规律编排起来组成不同的代码(二进制数)来表示特定的含义.一位二进制代码有0和1两种,可以表示两个信号;两位二进制代码有00、01、10、11四种,可以表示四个信号;n位二进制代码有2n种,可以表示2n个信号,这种二进制编码在电路上很容易实现.

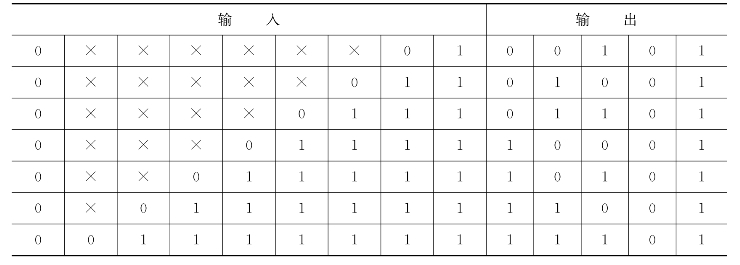

(1)三位二进制(8线-3线)编码器.

①键控三位二进制编码器.

图7-19 用按键和门电路构成的三位二进制编码器

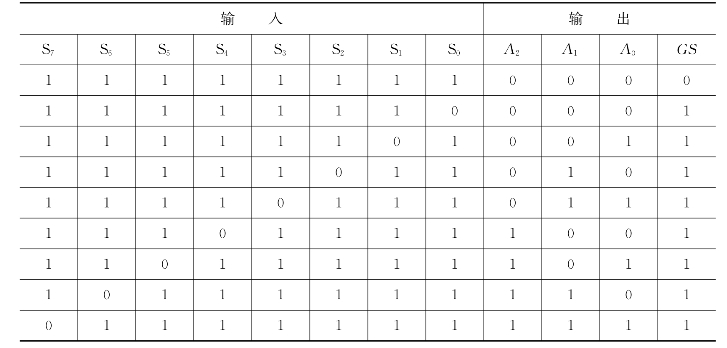

图7-32是由八个按键和门电路组成的三位二进制编码器,图中S0~S7代表八个按键,作为信号的输入,A2、A1、A0为二进制代码的输出,GS为控制使用标志.在按下S0~S7中任意一个按键时,只有在GS=1时,编码器才表示A2、A1、A0有输出,否则无输出.该编码器的真值表如表7-16所示.

由真值表可见,每组输出代码对应一个按键按下时的状态.

表7-16 三位二进制编码器真值表

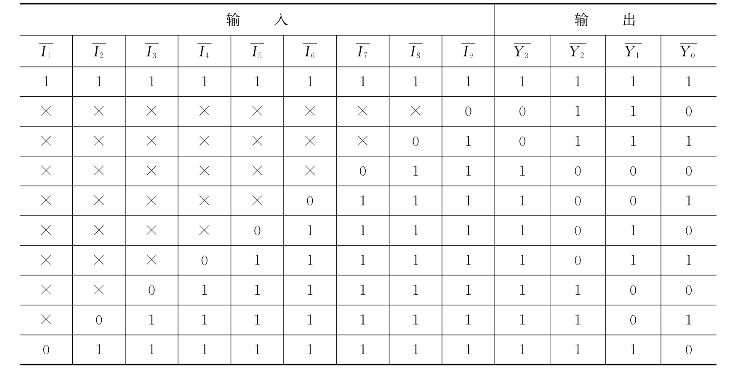

②集成三位二进制编码器.

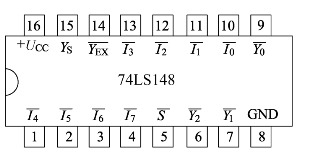

图7-20 8线—3线编码器74LS148

图7-20所示是集成8线—3线优先编码器74LS148的外引脚接线图.

它有8个不同的输入信号![]()

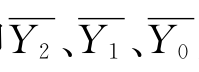

![]() ,根据2n=8,n=3,则输出信号为三位二进制代码

,根据2n=8,n=3,则输出信号为三位二进制代码![]() ,图中

,图中 为允许编码控制端,

为允许编码控制端, =0时允许编码;

=0时允许编码; =1时不允许编码.YS为使能输出端,YS=1时允许输出;YS=0时不允许输出.

=1时不允许编码.YS为使能输出端,YS=1时允许输出;YS=0时不允许输出. 为优先编码输出端

为优先编码输出端 =1时不允许编码器输出

=1时不允许编码器输出 =0时,它按哪个输入端优先级最高则优先编码,当有两个或更多个数码输入时,总是按出现的最高级数码进行编码,而不管其他数码输入与否.如出现I7 =0,则无论I6 ~I0 中哪个为0时,因I7 优先级最高,此时优先编码器只按

=0时,它按哪个输入端优先级最高则优先编码,当有两个或更多个数码输入时,总是按出现的最高级数码进行编码,而不管其他数码输入与否.如出现I7 =0,则无论I6 ~I0 中哪个为0时,因I7 优先级最高,此时优先编码器只按 =0编码,输出为Y3=1、Y2=1、Y1=1的反码,即

=0编码,输出为Y3=1、Y2=1、Y1=1的反码,即 为000.其功能表如表7-17所示.

为000.其功能表如表7-17所示.

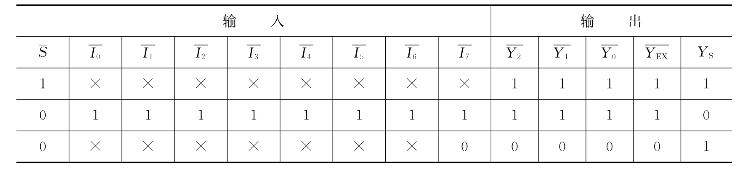

表7-17 74LS148功能表

续表

注:×表示任意态.

(2)二—十进制(10线-4线)编码器.

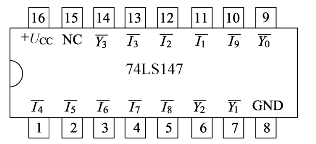

图7-21 10线—4线优先编码器74LS147

二—十进制编码器是将十进制的十个数码0、1、2、3、4、5、6、7、8、9编成二进制代码的电路.输入0~9十个数码,输出对应的二进制代码,因2n≥10,n常取4,故输出为四位二进制代码.这种二进制代码又称二—十进制代码,简称BCD码.常用的BCD码为8421BCD码.

集成10线—4线优先编码器74LS147可实现这种编码,它的外引脚如图7-21所示.逻辑功能表如表7-18所示,由表可见, 输入优先级最高,

输入优先级最高, 输入优先级最低,如当

输入优先级最低,如当 =0时,则不管其余

=0时,则不管其余 ~

~ 有无输入,编码器均按

有无输入,编码器均按 输入编码,输出为9的8421BCD码的反码0110.

输入编码,输出为9的8421BCD码的反码0110.

当 ~

~ 均为1,即无输入信号时,编码器输出

均为1,即无输入信号时,编码器输出 ~

~ 为0000的反码1111.

为0000的反码1111.

表7-18 10线—4线优先编码器74LS147功能表

2.译码器

译码是将二进制代码作为输入信号,按其编码时的原意转变为对应的输出信号或十进制数码.

(1)二进制译码器.

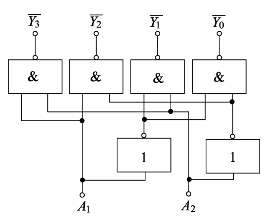

①二位二进制译码器.二进制译码器是一种能把二进制代码的各种输入状态变换为对应输出信号的电路.图7-22所示电路是二位二进制(2线—4线)译码器.

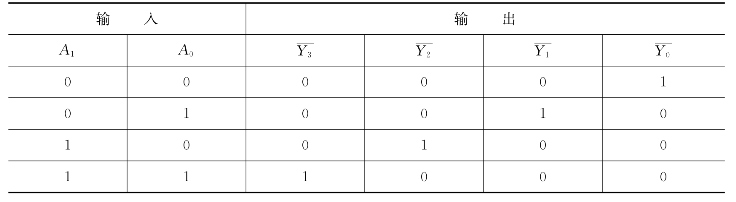

由图可得二位二进制译码器的状态表如表7-19所示.

图7-22 二位二进制(2线—4线)译码器

表7-19 二位二进制译码器状态表

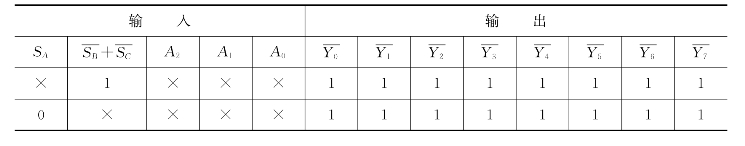

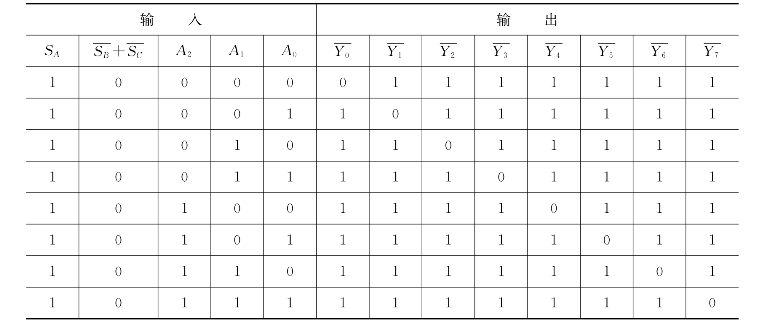

②三位二进制译码器.图7-23是三位二进制(3线—8线)译码器74LS138的外引脚接线图和图形符号.图中A2~A0为输入端, 为输出端.

为输出端. 为输入使能端,当SA=1

为输入使能端,当SA=1 =0时,译码器处于工作状态进行译码,并根据输入状态,在相应的输出端输出信号;当不满足上述条件时,输出端无信号输出.其功能如表7-20所示.

=0时,译码器处于工作状态进行译码,并根据输入状态,在相应的输出端输出信号;当不满足上述条件时,输出端无信号输出.其功能如表7-20所示.

图7-23 译码器74LS138的外引脚接线图和图形符号

表7-20 3线-8线译码器74LS138功能表

续表

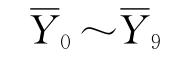

(2)二—十进制译码器.

图7-24是四位二进制(4线—10线)译码器74LS42的引脚排列图和图形符号.

二—十进制译码器是将8421BCD码译成10个对应输出信号的电路,当输入信号为1010~1111时,所有输出均为1状态,为无效状态.当输入为0000~1001时,对应的输出 分别为0(只有一个为0,其余为1).

分别为0(只有一个为0,其余为1).

图7-24 译码器74LS42的引脚排列图和图形符号

(3)显示译码器.(https://www.xing528.com)

用来驱动各种显示器件,从而将用二进制代码表示的数字、文字、符号翻译成人们习惯的形式直观地显示出来的电路,称为显示译码器.显示译码器主要由译码器和驱动器组成,通常这二者都集成在一块芯片上.

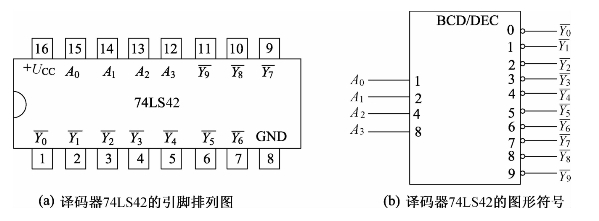

①七段数字显示器.

常见的七段数字显示器有半导体数码显示器(LED)和液晶显示器(LCD)等.这种显示器由七段发光的字段组合而成.LED是利用半导体构成的.而LCD是利用液晶的特点制成的.由七段发光二极管组成的数码显示器如下:

图7-25 数码显示器

如图7-26所示为共阴极数码显示.

图7-26 共阴极数码显示

真值表如表7-21所示.

表7-21 共阴极数码显示真值表

②七段显示译码器.

4线—7段译码器/驱动器CC14547,7段显示输出采用NPN双极型晶体管结构,因而具有较大的输出驱动电流能力,可以直接驱动LED或其他显示器件.适用于各种仪器仪表,计数器,数字电压表及钟、表定时器等方面的显示器件.

其功能如下:

消隐功能:当BI=0时,输出a~b都为低电平0,各字段都熄灭,显示器不显示数字.

数码显示:当 =1时,译码器

=1时,译码器

工作.当A3、A2、A1、A0(D、C、B、A)端输入8421BCD码时,译码器有关输出端输出高电平1,数码显示器显示与输入代码相对应的数字.

其逻辑功能示意图如图7-27所示.

图7-27 CC14547逻辑功能示意图

3.加法器

在数字系统中,尤其在计算机的数字系统中,算术运算都是分解成若干步加法运算进行的.因此,加法器是构成算术运算的基本单元电路.

(1)半加器.

能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器.或只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路称为半加器.

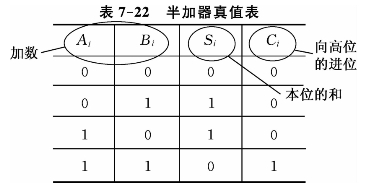

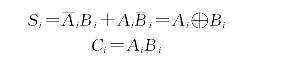

①半加器真值表如表7-22所示.

②输出逻辑函数如下:

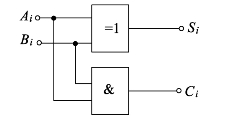

③其逻辑图如图7-28所示,逻辑符号如图7-29所示.

图7-28 半加器逻辑电路图

图7-29 半加器逻辑符号

(2)全加器.

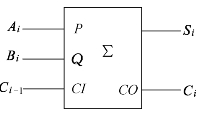

在进行数据运算时,需要对多位二进制数相加,而数字电路中的运算是一位一位进行的,因此需要把某一位的Ai和Bi两个待加数相加,还要与来自低位来的进位数Ci-1相加,这样才在本位得到一个和数Si,并产生一位向高位的进位数Ci.这种加法称为“全加”,实现这种逻辑功能的电路称为全加器.逻辑符号如图7-30所示,其逻辑状态表如表7-23所示.

图7-30 全加器逻辑符号

表7-23 全加器逻辑状态表

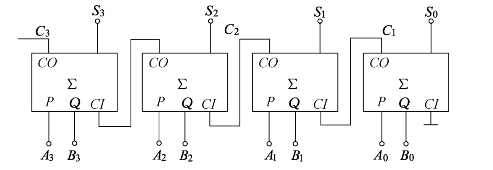

(3)加法器.

在熟悉一位全加器的逻辑功能后,就可以讨论多位二进制数相加的问题了.图7-31是四位二进制进行相加的示意图.它由4个全加器组成,只要依次将低位进位的输出端CO接到高位全加器的低位输入端CI,最低位全加器的低位输入端CI应接0.

图7-31 四位二进制的并行加法器

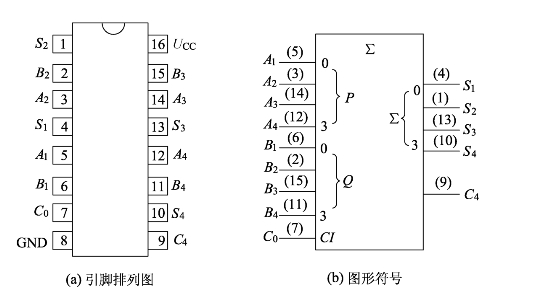

为提高运算速度,采用超前进位实现全加,图7-32是中规模集成四位二进制超前进位全加器74LS283的外引脚排列图和图形符号.该电路中只要分别接上四位二进制的被加数A和加数B,并使最低位输入数处CI为0,则在S3、S2、S1、S0可得到四位二进制数的和数,并由C4得到向高位的进位数.

图7-32 四位二进制加法器74LS283

逻辑门电路是构成数字电路的基本单元电路.最基本的门电路有“与”、“或”、“非”门.由这些基本门电路组成的常用复合逻辑门电路有“与非”门、“或非”门、“与或非”门、“异或”门、“同或”门等电路.

本章介绍了公式化简法,其优点是不受变量个数的限制,但是否能够得到最简的结果,需要熟练地运用公式和规则及一定的运算技巧.组合电路的逻辑功能可用逻辑图、真值表、逻辑表达式、卡诺图和波形图五种方法来描述,它们在本质上是相通的,可以互相转换.

TTL和CMOS集成“与非”门电路是应用最广泛的逻辑电路,它的逻辑功能是“见0出1,全1出0”.

将若干个0和1按一定规律编排组合后,组成不同的二进制代码,用来表示各种信息或操作,这一过程称为编码.实现编码的逻辑电路称为编码器.将二进制代码的特定含义转换成相应输出状态的过程称为译码.实现译码的逻辑电路称为译码器.加法器是数据算术运算中的基本逻辑电路.

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。