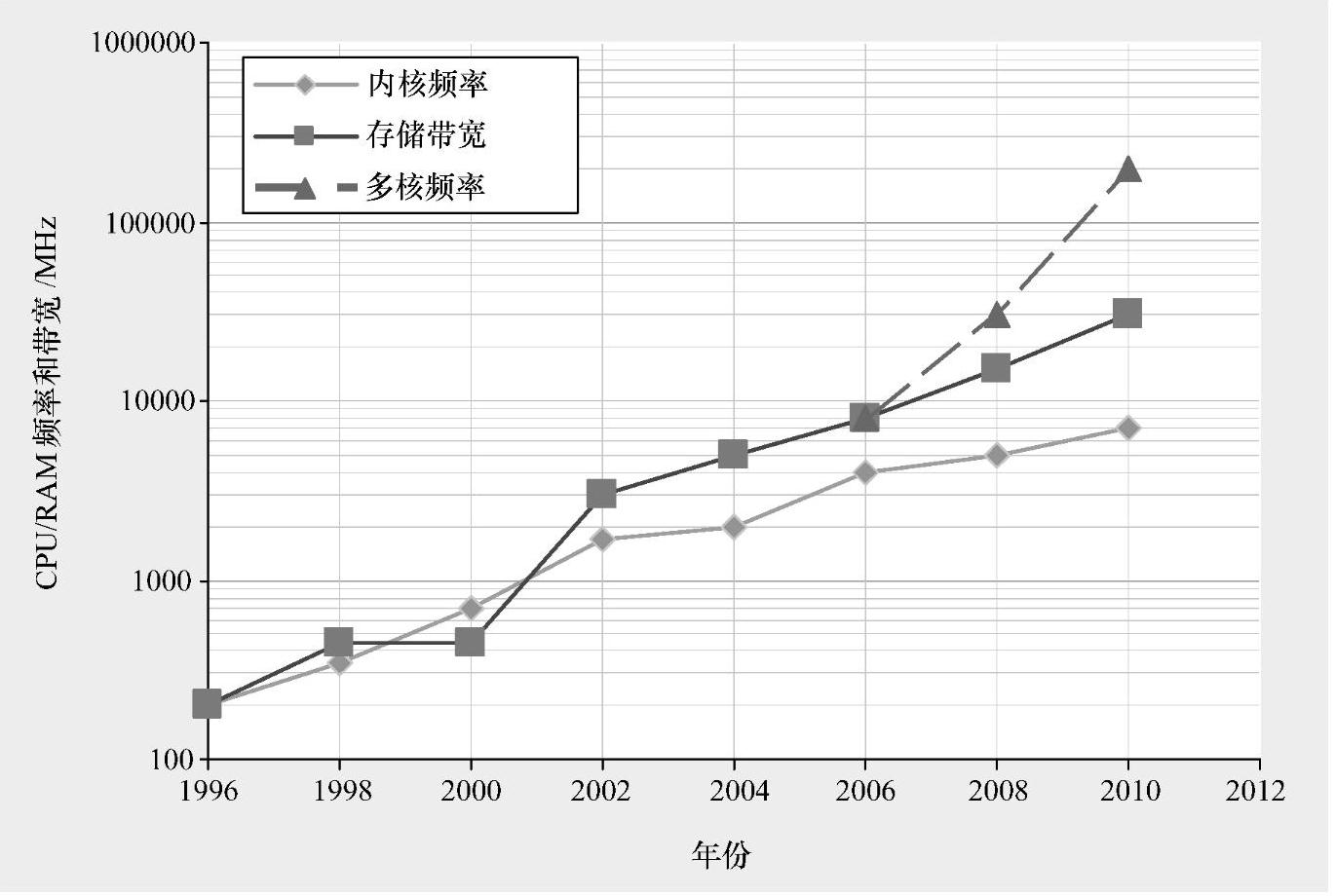

提高纳米级电子器件性能的另一个重要要求是,为计算器提供充足的数据带宽。增加晶体管数目、提高频率和改进设计,如多芯结构,推动着计算性能的日益提高。随着CPU(中央处理器)处理能力的提高,到CPU的互连需要呈指数增加的数据带宽来满足图形学等高性能的应用领域。图22.13给出了CPU内核频率、传统CPU与多核CPU结构的存储带宽的发展趋势[11]。该曲线表明多核结构的存储带宽要求远远大于传统CPU结构所需要的带宽。因此,需要革命性的解决方案来在功率和成本预算之内使数据带宽与CPU性能保持同步。

图22.13 CPU核频率和带宽的发展趋势

一般来说,可以通过提高数据传输速率和增加输入/输出接口数目来增加带宽。提高数据传输速率会给封装和插孔技术带来很大的挑战。众所周知,在低频率下,因为封装和插孔的电长度远比波长短,所以它们可以被视为R、L和C元件。高频率下,封装和插座的互连可被视为发射线。材料的性能、制造误差和信号线的设计方案,对低频数据传送中信号完整性的影响可以忽略,而对高频数据传送会造成重大影响。

为了增加数据传输速率,通常可通过管理互连损耗和控制阻抗波动增加信号频率。封装传输线中的损耗主要来自导线损耗。由于现在信号线已经用了铜材料,尽管如本章前面小节所述互连密度有所增加,但为实现导线损耗的最小化,仍需要降低其表面粗糙度,增大其横截面积。导线截断面积增加会提高信号线的纵横比,这就需要提高基板的材料和加工技术。另一个提高信号传输速度的方法是阻抗控制。其关键是减小信号线路的电容,以便提高其特征阻抗来与系统阻抗匹配,从而降低回程损耗。这一般通过改进设计和封装的介电材料来实现。当高速信号通过封装互连时,信号波会遇到各种中断或特征阻抗的改变。倒装芯片中主要的中断发生在信号线向PTH(镀通孔)和2LI焊盘[10,16]的过渡处。每一个中断都会造成信号的反射,从而增加了总的信号延滞和信号丢失。因信号速率更快,延滞和丢失可能造成数据传输的错误。PTH中断的解决方法有:采用直径更小的PTH,或采用可消除中断的无板芯层的基板。采用更小的2LI焊盘,和(或)通过在焊盘上方的金属层中生成空洞(create a void on the metal plane above the pad)来减小焊盘电容,这样可以把2LI焊盘处的中断最小化。(https://www.xing528.com)

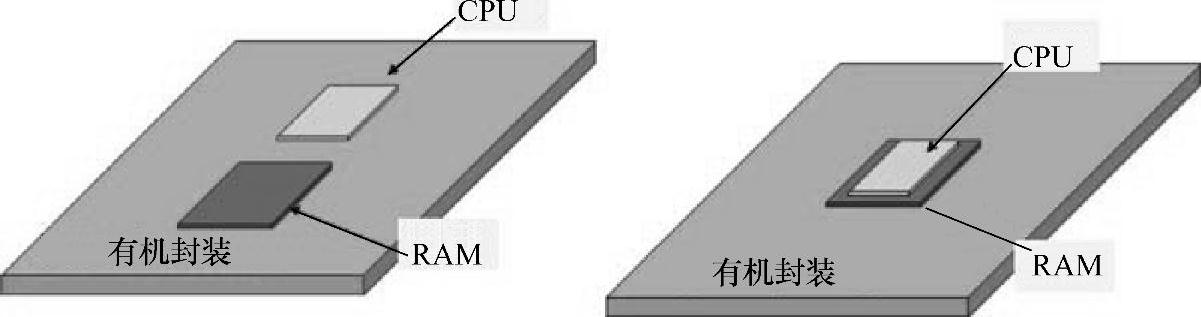

图22.14 高带宽存储器的连接方法

优化传统的互连线路,或把母板上CPU、芯片组和随机存取存储器(RAM)封装布置得更紧密,可以增加带宽,但这些方法并不能满足将来高性能计算和多媒体应用的要求。增加带宽的另一种方法是增加I/O点数,正如前文所述,这会增加互连密度,也可能增加封装尺寸和成本。因此,需要与当前范式迥异的解决方案来增加带宽。我们给出两种方法:一种是对CPU和存储芯片采用传统的多芯片封装(Multichip Package,MCP)结构,把CPU和RAM并排放置(二维结构)在单个封装上;另一种是三维堆栈方法,把CPU安装在有硅通孔的RAM之上。图22.14给出了两种方法的基本思想。根据对RAM2010年时的性能,传统多芯片封装结构能够提供的带宽可达到几千亿bit/s。但是,要达到更高数量级的带宽,就需要芯片的3D堆栈。3D堆栈一方面能提供很高的互连密度,另一方面能通过提高数据传输速率和改进功率消耗而提升带宽效率。为了使3D堆栈能够运用硅通孔技术,需要材料的大力度发展。光学互连也是获得高带宽的另外一种革命性方法[17,18]。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。