当管芯凸点间距缩小时,FLI的线宽和间距要变得更小,以便把信号从片上端点引到2LI端点。通常需要提高布线密度来使信号线避开芯片附近的拥挤区域。在我们讨论封装内部互连的发展趋势之前,我们先简单地描述一下有机倒装芯片封装基板的结构。

基板通常含有多层材料,其中心层是板芯层。板芯层的作用是为封装提供刚性结构支撑。板芯层由玻璃纤维强化聚合物层和铜导电层组成。聚合物层上有机械钻电镀通孔(PTH)。导电铜层则通过减成法光刻工艺制造,该减法光刻工艺类似印制电路板技术中广泛应用的光刻工艺。板芯层的典型厚度大约为800μm,电渡通孔的直径大约为250μm。在板芯层的两侧依次对称地设有表面积层。制备表面积层时,通常先添加一层厚约30μm的绝缘薄层,并用激光或其他方法在绝缘薄层上生成微通孔,微通孔的直径通常为小于100μm。随后,在绝缘薄层上形成大约15μm厚的铜线路,以构成互连层,并经过通孔连接到下面的导电铜层。目前,生成表面积层导体的主导工艺是半添加法(Semi-Additive Process,SAP)。与传统的减法工艺相比,半添加法能在封装中形成更细的线宽和间距。表面积层成对地依次叠加在板芯层两侧,直到达到所要求的层数。然后,在最外面施加一层阻焊剂保护层。接下来是完成镀金处理,如在基板前端的C4焊盘和基板后端的2LI焊盘上施加一层无电沉镍金层或镍钯金层。最后,在C4焊盘上生成焊料凸点,这就形成了倒装芯片焊盘栅格阵列(FCLGA)封装的有机基板。如果在芯片装配之前,把针脚焊接在2LI焊盘上,就构成倒装芯片引脚栅格阵列(FCPGA)封装的基板。如果在芯片装配之后,把焊料球施加在2LI焊盘上,就构成了倒装芯片球栅阵列(FCBGA)封装的基板。

通常,与布线线宽和间距相比,C4焊盘的尺寸相对较大。采用较大的C4焊盘直径,原因是多方面的。采用较大的C4焊盘能增加C4接点大小,这反过来提高了C4接点对裂纹的抵抗能力。C4焊盘较大也能降低通过C4接点的电流密度,并通过降低电迁移而提高了C4接点的容许载流能力。C4焊盘较大能增加焊料的体积。在C4接点的形成过程中,焊料体积增加能提高C4接点的垂直高度,并有助于提高C4接点装配工艺的产量。

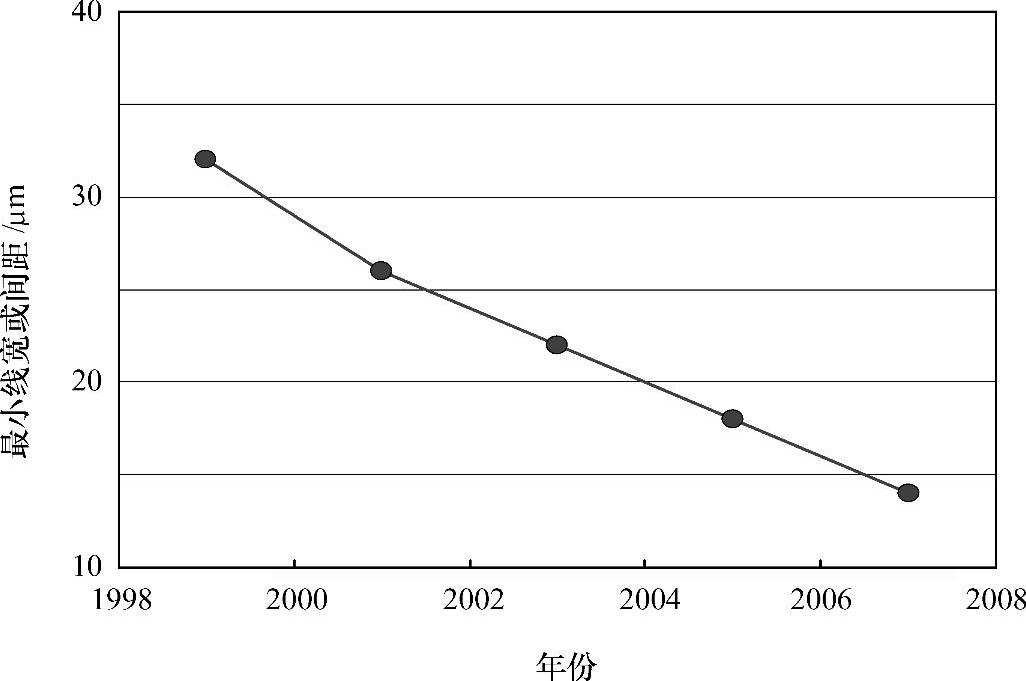

凸点间距的缩减一直促进着人们开发出更细的布线线宽和间距(见图22.8),且这种趋势有望继续下去。基板上的特征变得更细,给基板的封装带来了许多挑战。这些挑战包括:在光刻工艺中保持抗蚀剂层和导体材料层之间的可靠粘附,保持一个清洁的工艺环境以最小化异物入侵导致的产量和可靠性问题。从另一个角度看,通过大胆地减小微通孔和C4焊盘的尺寸,能降低对细布线线宽和间距的要求。这就要求基板技术、装配材料和工艺技术的革新,以此来生产具备机械鲁棒性的通孔和高载流容量的C4接点。在一定程度上,新的设计技术也能够降低对线宽和间距的要求。一个实例是,按高密度布线的要求优化凸点的布置,而不是把凸点布置在固定的网格上。另一个方法是减少焊盘间线路的数量。这种方法可能需要额外的封装层,并因此需要更高的成本,以便来实现迂回路由线。但是这也降低了对布线线宽和间距缩小的要求。(https://www.xing528.com)

图22.8 微处理器封装最小线宽和间距的变化趋势

另一要注意的特性是电镀通孔的尺寸。在直径为4000μm的焊盘上,电镀通孔的典型直径是250μm。由于路由线(目前,路由线的线宽约为15μm)和电镀通孔[10]之间尺寸的显著差异会引起电阻抗变化,因此电镀通孔的尺寸相对较大就会阻碍信号的高速传递。另外,这些电镀通孔可能会限制封装内部互连(路由线)的持续缩小。在将来可能需要减小电镀通孔尺寸或消除电镀通孔,来支持路由线的持续缩小和信号的高速传送。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。