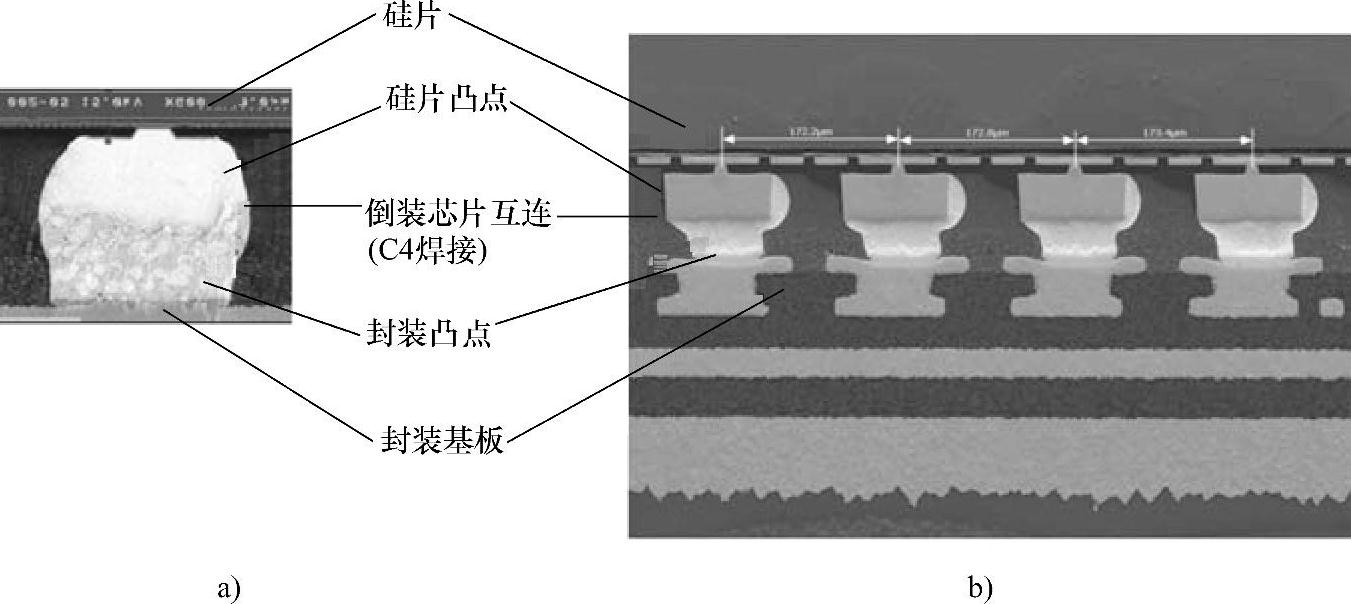

倒装芯片封装的管芯封装互连通常由称作可控坍塌芯片连接或C4的工艺制造。在最初的C4工艺中,管芯上的焊料凸点成列地布置在陶瓷封装中同位金属焊盘的顶部,然后进行回流焊以形成高度受控的接点[8]。这种芯片连接工艺的一个变体被广泛地用于有机封装中,且能把管芯上的非熔化凸点连接到封装基板上可回流的焊料凸点上。不严格地讲,这种工艺也可称为C4工艺。最初,有机封装的管芯凸点用的是高熔点的铅锡焊(3%~5%Sn和97%~95%的Pb),其熔点接近312℃,基板上的焊料凸点采用共晶的铅锡焊,熔点为183℃(见图22.6a)。出于环保考虑,人们开始采用无铅材料,如在管芯上使用铜凸点和在基板上使用锡银铜(SAC)焊料,如图22.6b[3]所示。

图22.6 倒装芯片的C4焊点示例

a)采用共晶锡铅焊料的高铅含量管芯凸点 b)采用锡银铜(SAC)焊料的铜管芯凸点

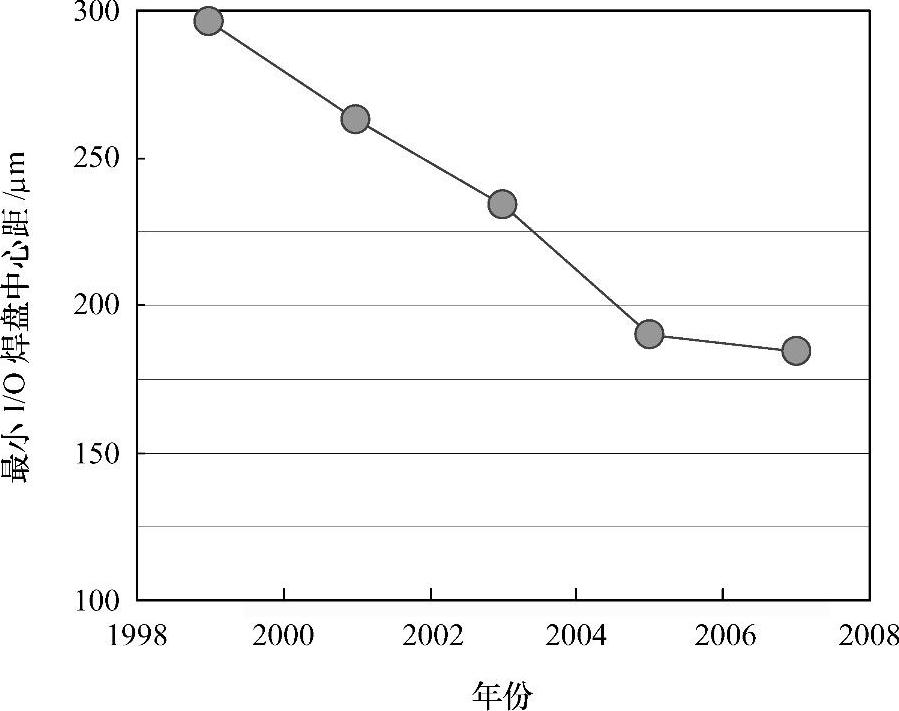

当芯片大小一定时,芯片上端点的数目增加,需要减小管芯凸点间距以便来容纳所有的凸点。图22.7给出了主流微处理器输入/输出凸点最小间距的发展趋势。凸点间距变小能减小C4接点的大小和间距,但这给FLI技术带来了挑战。在封装装配过程中,凸点间距变小需要先进的设备和材料来精确地定位管芯并保持其位置,直到C4接点形成。接点尺寸变小会减小焊球的体积,因此也会减少芯片回流焊接过程中接点处焊球的坍塌高度。这就要求管芯凸点和封装基板配合接触区有良好的共面性,以此来降低C4接点变为电气开路的风险。

(https://www.xing528.com)

(https://www.xing528.com)

图22.7 美国英特尔公司微处理器I/O凸点最小尺寸的趋势

因为C4接点水平方向间距变小和管芯与封装壳间垂直高度减小,凸点间距变小同样会影响底部填充材料和工艺的选择。这些空间减小会限制底部填充胶中填充颗粒的大小,底胶中的填充颗粒用于减小底胶的热膨胀系数,而又同时增加了其断裂韧性。而且,当凸点间距变小时,人们对底胶流动动态过程的控制减弱,因为底胶的流动速度可能对封装的制造和设计波动变得更敏感。因此,当凸点间距变小时,优化底部填充工艺和底胶材料的性能会变得更具有挑战性。同时,当倒装芯片的接点间距减少时,FLI会对空洞和其他缺陷变得更加敏感,因为缺陷会增加相邻两接点间的质量迁移。

当C4焊接接点变小时,它们还需要解决高电流密度的问题。这种电流密度变高是芯片的总电流增加(甚至在功耗相同时,由于器件电压下降,总电流也会增加)和/或片内电流不均匀性的结果。而片内电流不均匀的原因是管芯上不同位置器件的功耗波动。如果FLI的高电流密度问题不能通过恰当的设计、材料和工艺选择妥善解决,高温下硅芯片中的高电流密度最终可能使FLI因电迁移而变成开路,从而导致器件失效[9]。

C4接点设计的另一个重要考虑是C4接点对片内互连中热机械应力的影响。对过去的几代硅器件而言,硅工艺工程师都在集中精力研究如何减小片内互连绝缘材料的介电常数。这也减小了片内互连的机械强度,使得片内互连对封装热应力引起的失效更加敏感。因此,C4接点必须具备足够的柔性,以便最小化在硅片上封装产生的应力。

总的来说,需要合理选择FLI材料和工艺来保证如下四点:封装能向更小尺寸持续缩小,FLI具备足够的柔性,接点的高电流密度能够得到有效管理,封装是环保的。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。