【摘要】:可以发现,底胶脱层是引起基板上倒装芯片组件电失效的主要原因。芯片界面处的底胶脱层为焊料挤压提供了通道。图14.32 采用纳米二氧化硅底胶的倒装芯片结构横截面图图14.33 采用微米底胶的倒装芯片结构横截面图14.34 底胶和芯片界面处的脱层图14.35 底胶中焊料的挤压流动图14.36 显示焊料在底胶中挤压流动的切片SEM图像图14.37 倒装芯片界面处的失效(疲劳)裂纹图14.38 63Sn37Pb合金焊点失效的Weibull分布

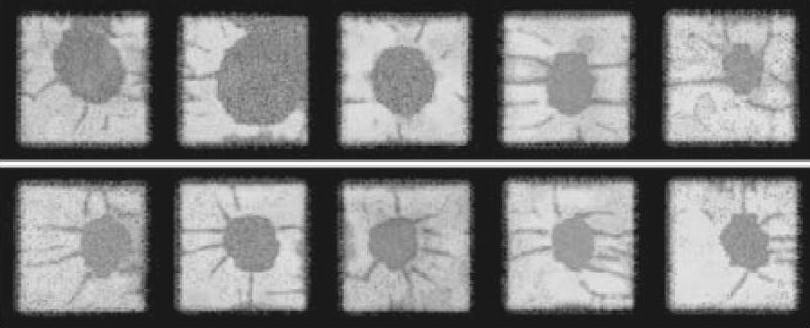

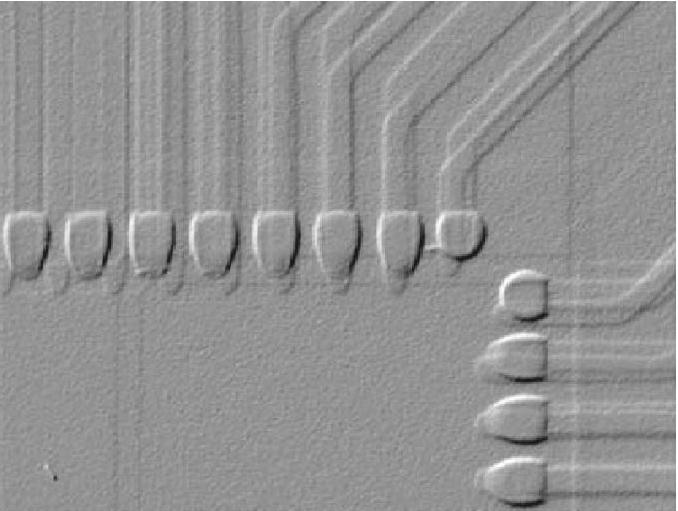

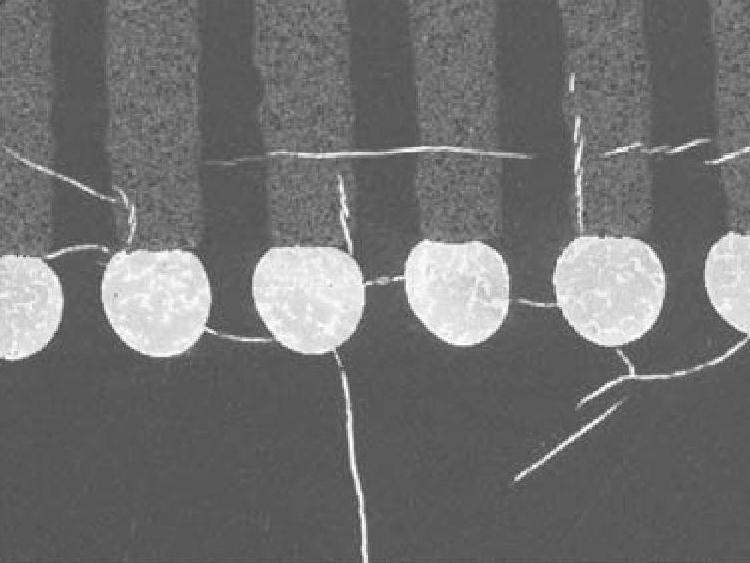

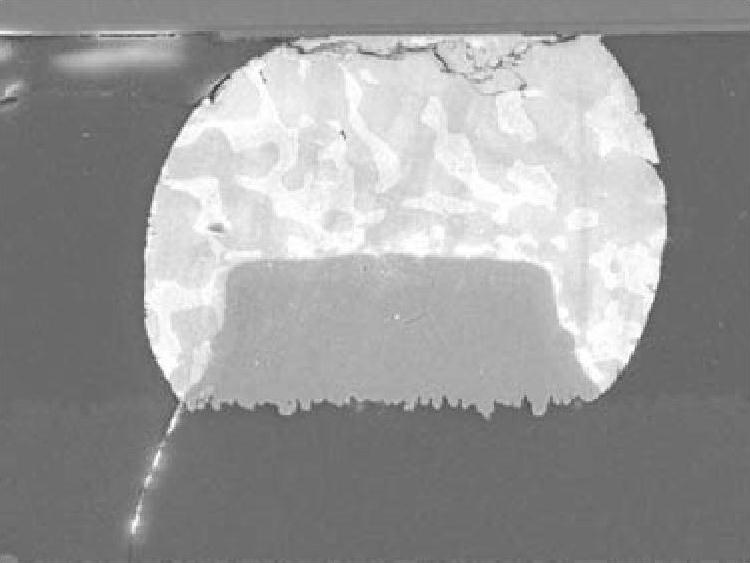

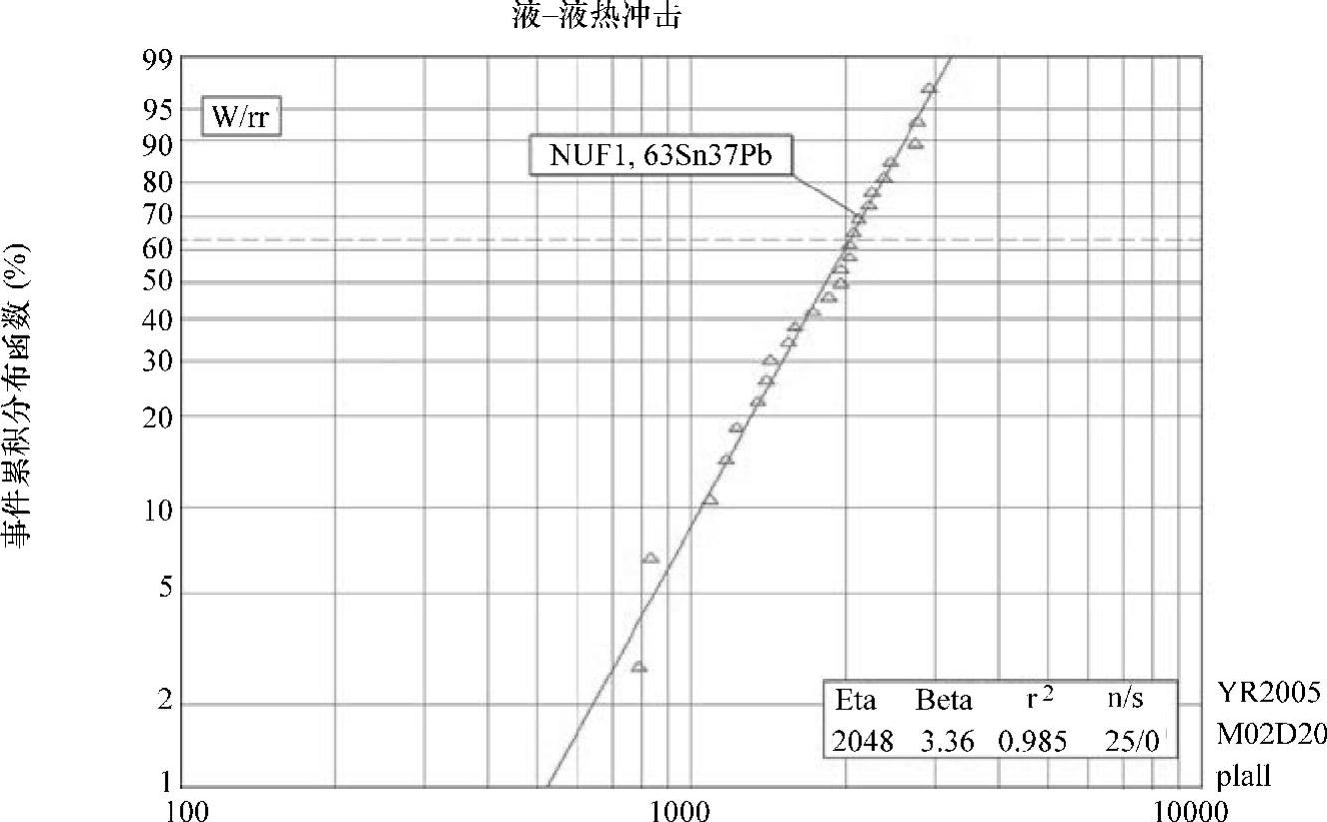

测试的温度变化范围为-55~125℃。把倒装芯片通过88个焊点焊接在PB8板(5.08mm×5.08mm)的四周,就形成了测试用的裸片。焊点间距为0.203mm。焊球直径为0.127mm。焊料合金为37Sn/Pb低共熔混合物。基底是高玻璃化温度Tg的层合板,每一层基底上有10块芯片。可以发现,底胶脱层是引起基板上倒装芯片组件电失效的主要原因。图14.34所示为进行3120次热冲击循环后失效的装置,并且在进行3120热冲击循环后,试样100%失效。Weibull失效分布如图14.38所示。芯片界面处的底胶脱层为焊料挤压提供了通道。从图14.35所示的X射线检查结果和图14.36所示的样品切片电子显微镜图中,可以观测到焊料挤压。焊点的疲劳失效是因为二氧化硅和压缩基底的热膨胀系数不匹配和底胶脱层。倒装芯片界面的失效(疲劳)裂纹如图14.37所示。

图14.32 采用纳米二氧化硅底胶的倒装芯片结构横截面图(暗色和银色区域的顶部边界是芯片和填料的边界)

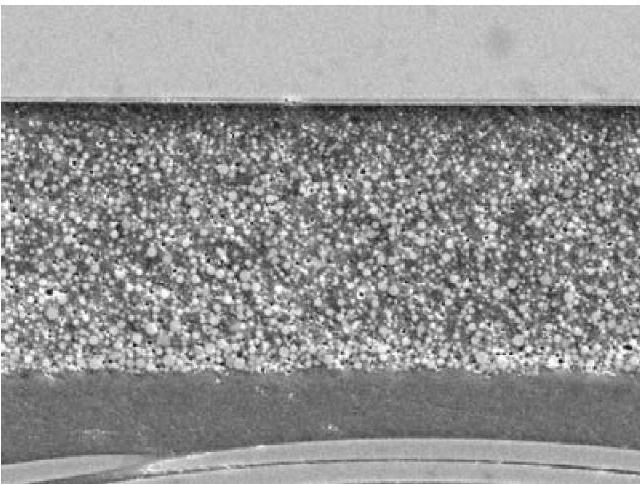

图14.33 采用微米底胶的倒装芯片结构横截面

图14.34 底胶和芯片界面处的脱层

(https://www.xing528.com)

(https://www.xing528.com)

图14.35 底胶中焊料的挤压流动(X射线衍射)

图14.36 显示焊料在底胶中挤压流动的切片SEM图像

图14.37 倒装芯片界面处的失效(疲劳)裂纹

图14.38 63Sn37Pb合金焊点失效的Weibull分布

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。