本章描述的是,运用可以分层的标准件来获得相互之间导电连接的一整套方法。其片心由各种布置好的信号层、电压层和零电位层组成。

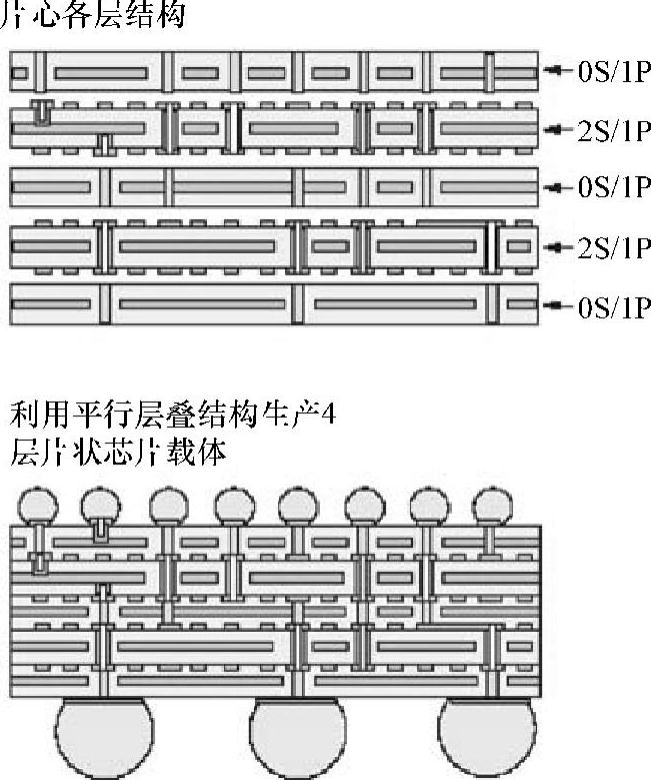

另外,信号层、电压层和零电位层可以安置在同一层。作为研究案例,Z轴方向的连接方法被用来制造焊点间距为150μm的倒装芯片的封装。这里采用了两个基本的片心模块(见图11.13)。一个是2S/1P片心。电源层(P)为35μm厚的铜金属片,夹在两层PTFE绝缘体中间。PTFE以(60wt%)二氧化硅颗粒为填料,从而减少了绝缘材料的CTE,并且和铜更为匹配。采用PTFE是由于它良好的导电、力学和热力性能。以二氧化硅为填料的PTFE的相对介电常数和损耗因数(tanδ)在10GHz条件下分别为2.7和0.003。

图11.13 平行层叠复合结构(片心)形成的片状芯片载体(此芯片载体有4层具有带状传输线结构的信号布线层)

信号层(S)包含采用半添加法(线路电镀)工艺得到的铜特性。电镀工艺制作而成的最小尺寸达到了12μm宽的线路和25μm的线路间距。基板和线路最小间隔也是25μm。若在通道中采用激光钻通孔的方法可以得到40μm直径的通孔。用激光钻盲孔的方法钻盲孔,可以得到50μm直径的盲孔。之所以选择后者,是为了避免钻通孔时纵横比大于1∶1的要求。电镀焊盘的直径在75μm左右。这样的尺寸大小,可以满足布线设计时在最稠密的芯片区域内一个线路占用一个通道的要求。(https://www.xing528.com)

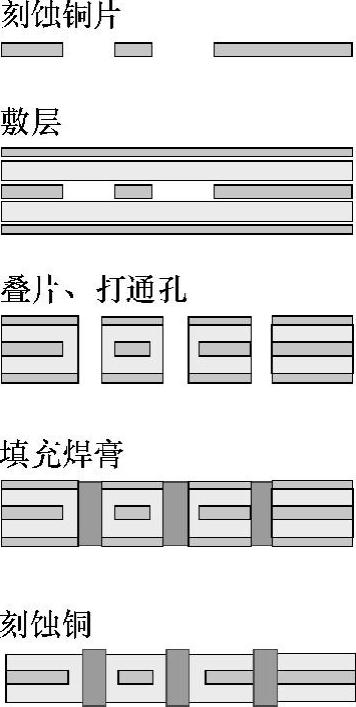

在这个案例中,第二个是0S/1P片心,或者叫“连接片心”。这个片心的结构是中间为35μm厚的铜质电源层,两边为烯丙基化聚苯醚(Allylated Polyphenylene Ether,APPE)和以二氧化硅为填料的聚合物夹层。在1GHz条件下,材料的相对介电常数为3.23,在1MHz的条件下介电损耗因数为0.003。片心中的通孔是用导电胶填充的(见图11.12)。图11.14所示为0S/1P芯片的结构和制作过程。

图11.14 0S/1P制作 的主要步骤

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。