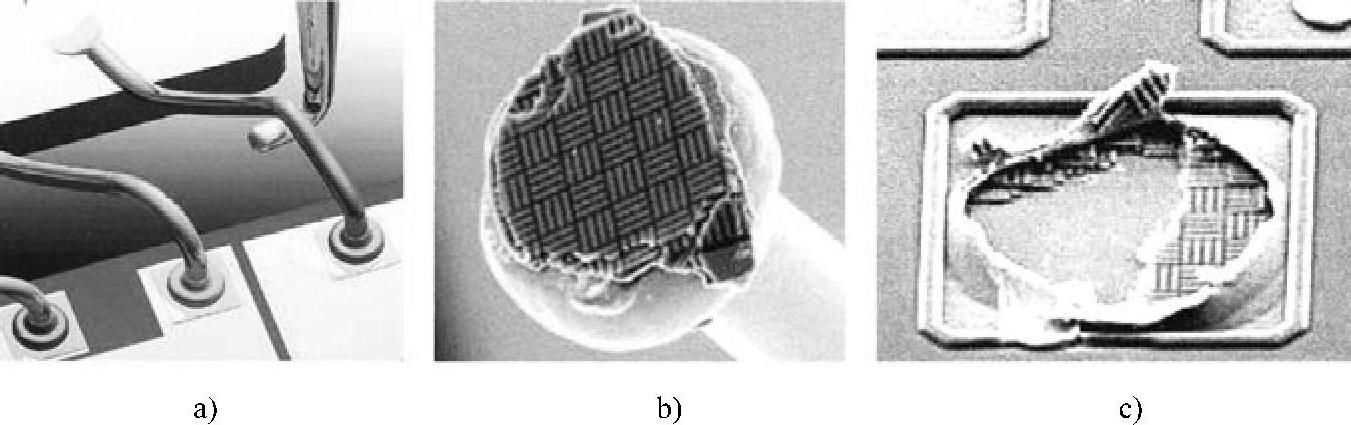

人们在电子封装中引入了低k值的介电材料以便促进Cu/低k值CMOS技术当前和未来的发展,而这也带来了一个重大问题,因为这种介电材料的硬度较低且界面粘附性较弱[43]。目前,广泛使用导线拉力条件测试来评估Cu/低k值介电材料结合衬垫的结构完整性[27],如图4.16所示。

图4.16 评估Cu/低k值介电材料结合衬垫结构完整性导线拉力条件测试及脱层实例

a)导线拉力测试 b)、c)衬垫连接脱层的实例

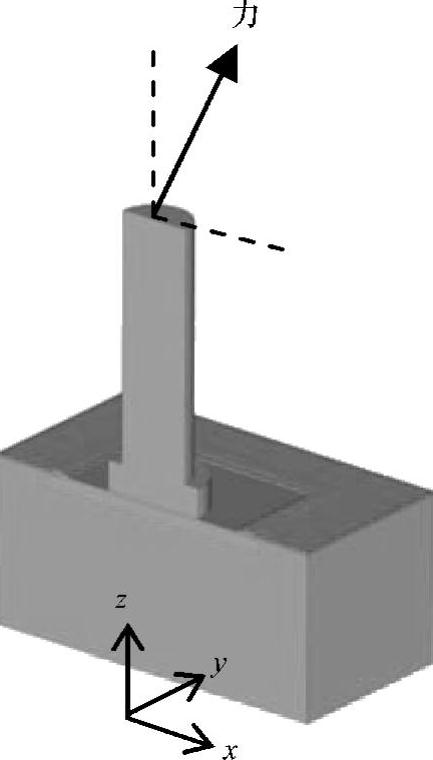

图4.17 对称导线拉力模型

为了研究在键合区连接下方不同后端设计的影响,人们提出了一种包含面积释放能(ARE)标准的多尺度数值框架[27,28]———导线拉力模型,如图4.17所示。它包括带铝层结合衬垫、钝化层、后端结构、球形连接和直径为25μm的金线。通过在(x-z)平面内与z轴呈20°夹角方向上,施加一个大小为3gf(1gf=9.80665×10-3N)的力来实现导线拉力评定测试的建模。这个力也是这种球型连接的典型条件载荷。图4.18所示为几个结合衬垫的可视化模型,其中的单位单元是按照CMOS090设计规则手册来设计的。

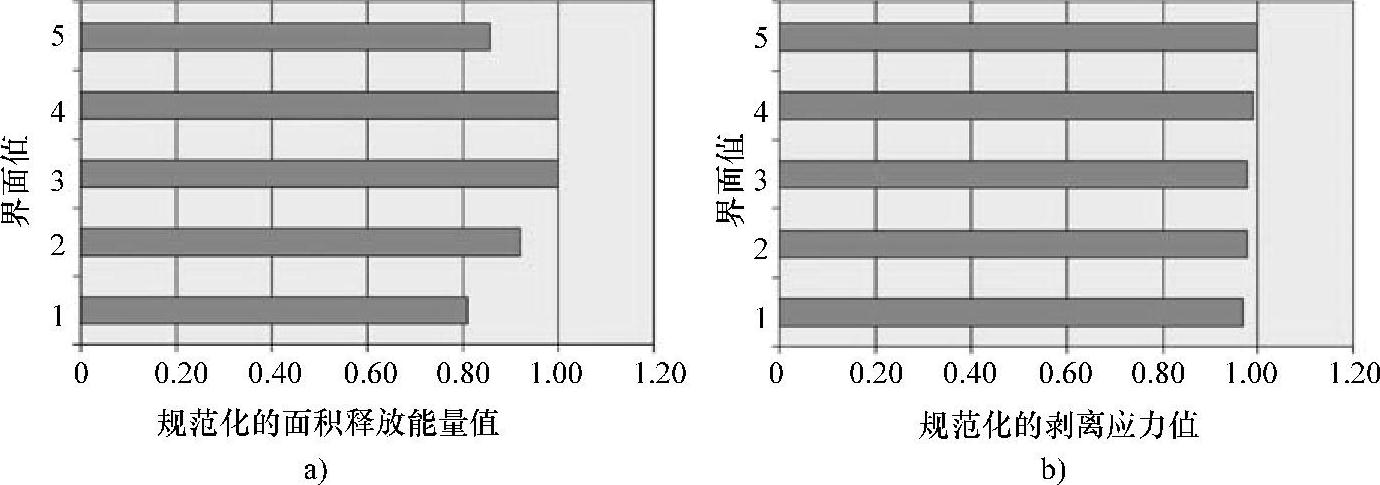

大多数临界结构和临界界面都会通过产生的最大面积释放能量来鉴别。对于这些不同结构所对应的最大ARE值(规范化的)分别是,结构A为0.86,结构B为0.80,结构C为1.00。由此可见,三种结构中结构C最差,并且已经被实验所证实。对于这种结构,图4.19a给出了最大规范化面积释放能量值,而图4.19b给出了最大规范化剥离应力值。根据面积释放能量值可知,第四个界面是临界界面,但从剥离应力的角度来看,所有界面的值都在脱层结构的正常值之内,没有显著的差异。实验FIB/SEM观察到的结果证实了界面4是临界面,脱层是从这个面开始的。从这些结果中看出,与基于应力的值对比,面积释放能量标准可以用来确定最临界后端结构(结构C)和最敏感的界面(第四个界面)。(https://www.xing528.com)

图4.18 局部后端结构(硬壳,上面的金属层没有显示出来,切去了1/4的结构)

图4.19 结构C的界面值

a)最大规范化面积释放能量值 b)最大规范化剥离应力值

在研究中,非常关键的一点是要认识到这些失效灵敏度分析对于J积分方法和内聚区模型并不可行。但是,在参考文献[29]中作者提出,在大多数临界面上采用局部内聚区模型,同时利用面积释放能量方法来识别,可以真正地分析脱层传播。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。