以太网由Zilog公司的网络发展而来,1980年由DEC、Intel、Xerox三家公司联合宣布了以太网的技术规范。以太网是著名的总线网,集散控制系统中采用CSMA/CD方式,处理数据的总线网大多采用以太网。

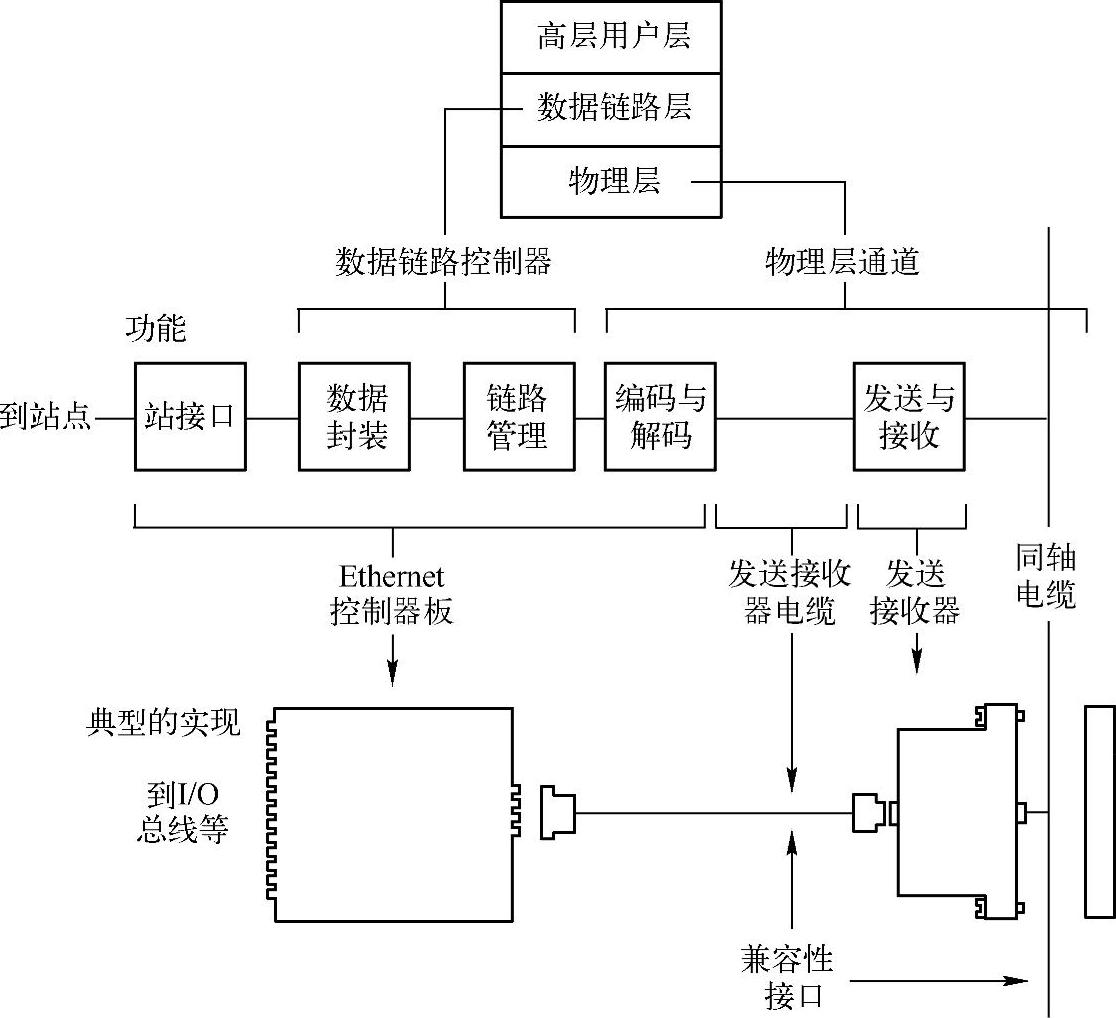

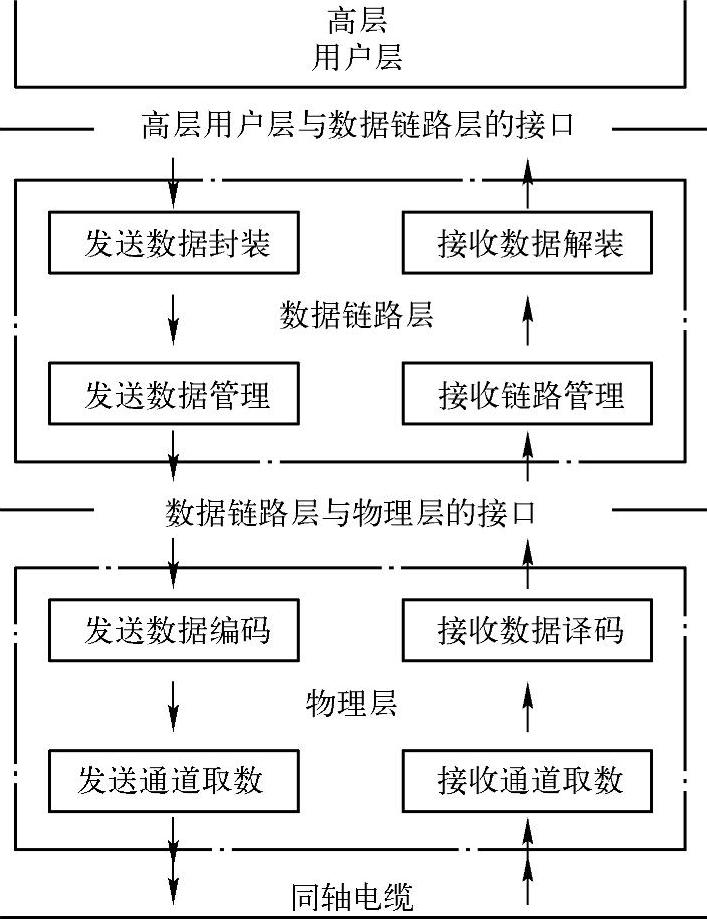

以太网的网络结构分3层:物理层、数据链路层和高层用户层。结构的实现如图3-11所示。控制器插件板完成数据链路层的功能,同轴电缆侧的收发器完成物理层的功能。图3-12详细说明了各层的功能。

1.物理层

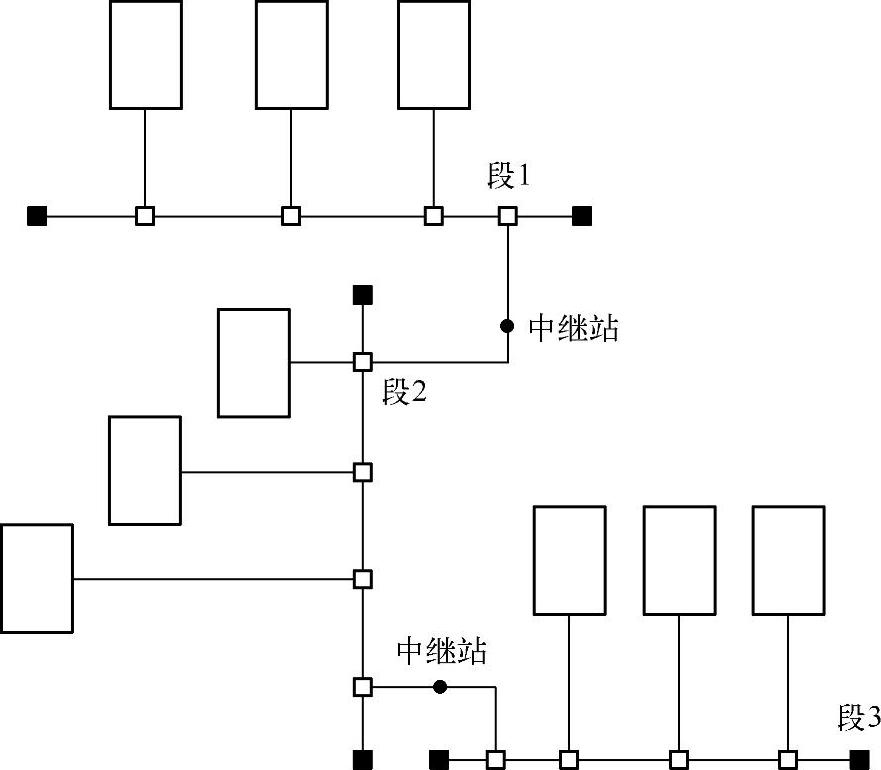

以太网的物理层采用50Ω基带同轴电缆作为通信媒体,数据传输速率是10Mbit/s,工作站最多1024个,工作站间距离通过中继站可达2.5km。每个工作站由收发器、收发器电缆、以太网接口及主机接口等组成。若干个工作站挂接在一根同轴电缆上组成分支式无根树(Branching non-rooted tree)的一个段,段与段之间用中继器连接。每根同轴电缆的长度应小于500m,收发器电缆长度小于50m,可挂接100个工作站。实际集散控制系统中,挂接的工作站数目远小于该约束数目。图3-13为以太网构成的例子。

图3-11 以太网的分层及物理实现

图3-12 以太网各层的功能

图3-13 以太网构成的例子

物理层的通信信道具有下列特点:

1)在同一网络上,两个以上的数据链路之间,具有收发信息的能力。

2)检测载波的能力。

3)检测冲突的能力。

4)最大往返传输的延迟时间是45μs。

物理层需要其硬件完成下列功能:

1)数据编码,采用曼彻斯特编码方式。

2)发送同步和时钟信号。(https://www.xing528.com)

3)载波检出和冲突检出。

4)位传送和接收,在数据帧前加入64位的前同步信息。前同步信息是如下的64位模式:前七组均为10101010,最后一组为10101011。给予收发器电缆上的交流信号电平,在差动驱动时的标称值是±700mV,(78±5Ω)。

2.数据链路层

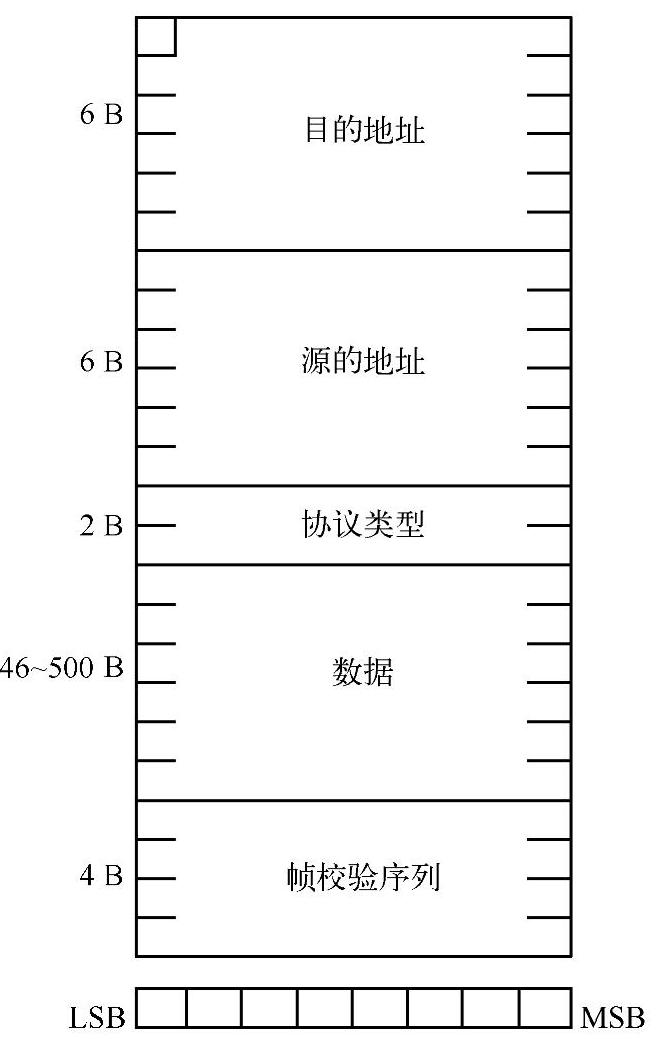

以太网的数据链路层分为数据封装和链路管理两个子层。在每个子层中,发送和接收是两个互相独立的部分。数据链路中的帧采用图3-14所示的格式。以8位为一个位组,采取从左向右的顺序传送。目的地址共6个位组,当第一位是“0”时表示物理地址,是“1”表示送往几个站的多目的地址。当全部48位是“1”时,表示送往以太网所连接的所有站。除第一位以外的47位是实际地址。源地址是发送站的地址。以太网采用32位循环冗余码作为帧校验,因此,在数据帧的最后有4个位组存放相应的位元。传送的数据是透明的,任意数据都可以,它可以占用46~1500个位组,因此,是可变长度的。

图3-14 以太网的数据帧格式

数据链路层的控制采用CSMA/CD方式。以太网得以广泛应用的原因,除了它具有结构简单、易扩充、传输速率高外,还得益于有现成的集成芯片来完成通信的功能。Intel公司推出的局部通信控制器82586及以太网串行接口82501,AMD公司用于以太网的局部网络控制器(LANCE)AM7990及串行接口组件(SIA)AM7991,富士通公司的数据链路控制器MB8795A和编码译码器MB502A等硬件的问世,使以太网的实现十分方便。

82586具有下列功能:

1)除全部支持以太网的物理层、数据链路层外,还支持高级数据链路控制HDLC的规程。

2)可配套16位或32位的循环冗余码校验。

3)0~6个字节的地址生成和校验。

4)可变长度的引导程序。

5)传输速度从100kbit/s到10Mbit/s。

6)具有8位及16位数据总线;具有4个DMA通道。

7)具有完整的诊断功能;可实现CSMA/CD的存取方式。

8)具有独立的8MHz系统时钟输入。

图3-15是82586的引脚配置。它是双列48脚LSI。在最小方式使用时,有22位地址空间,最大方式时有24位地址空间。82586的命令部件通过CPU与82586之间的提示通道,执行CPU的命令并发送帧。它的接收部件用于接收帧。命令表格和接收帧在存储器内存储。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。