半导体故障分析的目的是为利用电性测量及物性、化性、机械性能的先进分析技术去确定故障的发生及鉴定或追查出故障的模式(mode)及失效机理(mechanism),进而找出故障的根本原因(root cause)。而故障分析的流程必须有效地产出足够的结论,赖以指出故障的根本原因或提供产品制造、设计、测试或应用上改正行动(corrective action)的有效的依据,进而消除故障原因或防止故障模式或机构的重现。简而言之,故障分析的目标为以更快及更经济的方式去鉴定出故障原因。

1.故障因子

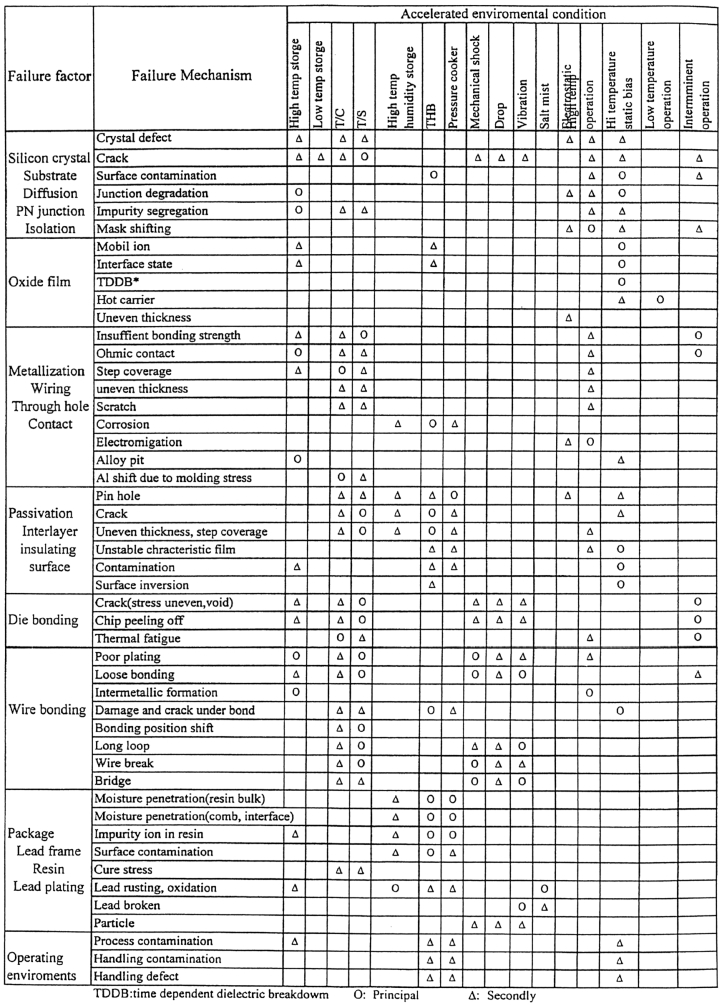

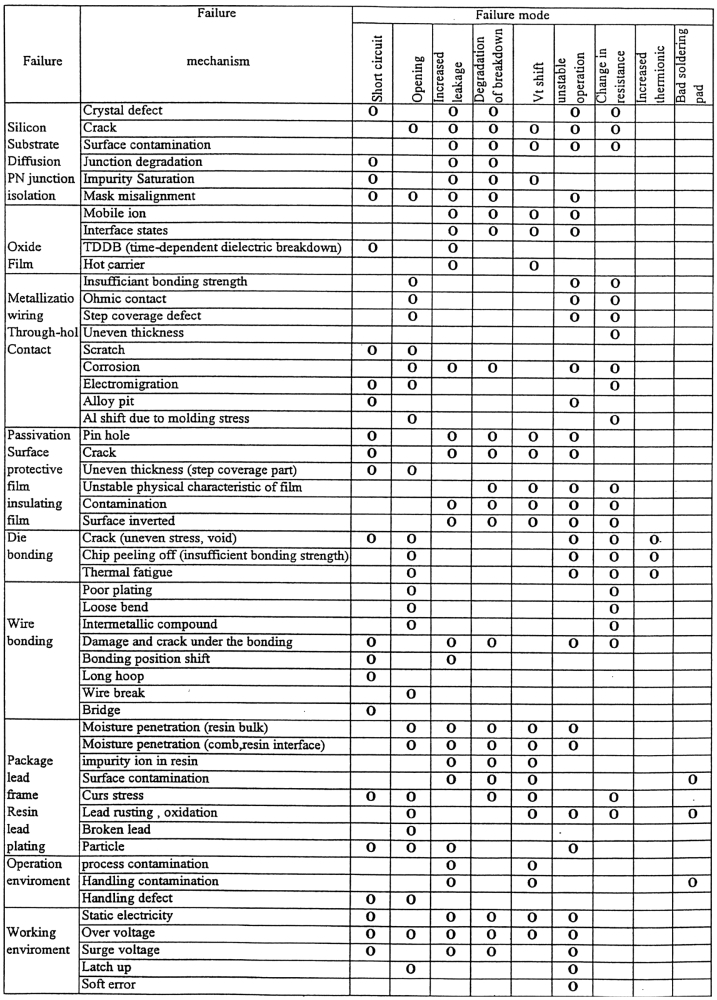

故障的成因非常多,也非常复杂。主要与测试环境或故障模式的相关性。表9-32为故障因子与测试环境项目的相关性,表9-33为故障因子与故障模式的相关性,此相关性仅供参考。

2.故障分析流程

简单的故障分析流程,可概分为①资料收集;②外部检查;③初步内部检查;④故障点定位;⑤层次去除,正面观察或横截面观察;⑥化性或元素分析;⑦故障机构及根本原因确定,分别简述如下:

表9-32 故障因子与环境测试的相关性

表9-33 故障因子和故障模式的相关性

(1)资料收集(data conditions)。资料收集为故障分析的前置作案。相关资料是否完备,关系到后续分析的进行及结论的好坏。资料包括:

①测量条件(test conditions):如测量形态(type of test)、温度及其他施加应力条件(stress conditions);

②系统条件(system conditions):包括测试机台、日期、环境及其他足以造成故障的系统异常(system anomalies);

③元件资料(device information):如产品型号(type number)、序号(serial number)、制造日期、晶粒(chip)大小、何种工艺技术、故障比例(failure rate);

④测试结果及故障模式(failure mode)。

(2)外部检查(external analysis)。包括电性故障确认(electrical verification)、封装外观检查、烘烤(bake)、X-ray及超音波检查等。烘烤是为了确认元件是否在烘烤后会复原,X-ray则是为非破坏检查封装内部是否有异常或位移,而超音波则检查封装内部是否有裂缝或剥离。

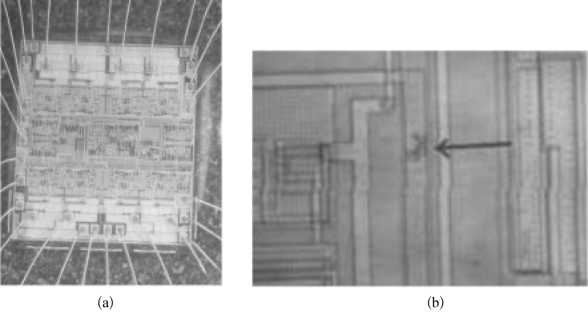

(3)初步内部检查(initial internal analysis)。包括打开封装材料(decap device)使晶片露出,如图9-98(a)所示,但不可破坏封装的打线(wire and bonding)、导线架(lead frame),以及晶片等,以确保后续测量的可行性。

图9-98 封装材料

(a)Decape前(b)Decape后

(4)故障点定点(failure site localization)。利用故障点定位技术来找出实际故障位置。目前可用的方法有:EMMI(emission microscopy),liquid crystal microscopy、E-beam test,OBIC,LIVA,(microcircuit analysis)及一些利用SEM原理的相关技术,如VC(voltage contrast),EBIC(electron beam-induced current),CCVC(capacitive coupling voltage contrast),passive voltage contrast,RCI(resistive contrast imaging),BRCI(Biased RCI),CIVA(charge-induced voltage alteration),LECIVA(low energy CIVA)等。上述的技术中有些需要将晶片最上层的护层(passivation)去处,有些则否,有些则需要借助FIB做线路隔离或跳、拉线等工作,如微线路分析。不管利用何种技术,最重要的是要根据故障模式、产品特性及相关资讯,选用最适当的技术,以期能最快速、准确地定位出故障点。

(5)层次去除观察或横截面观察(delayering or cross-sectioning)。利用研磨、劈裂、化学蚀刻液或FIB等技术将晶片的故障点显露出来,再以光学显微镜、SEM、TEM或FIB观察[见图9-98(b)],以确认故障的形态或缺陷的外观。一般来说,利用层次去除以观察正面或剖面研磨来观察横截面是不能同时进行,所以要根据故障模式及故障点定位所得的相关资讯来决定。

(6)化性及元素分析(chemical or elemental analysis)。在故障点显露及被显露之后,可能需要得知其中缺陷的成分或特性以利判断其成因或如何造成故障。常用方法有EDX、Auger、SIMS、ESCA、RBS、μFTIR,荧光显微镜等,选用何者完全取决于缺陷的大小、形态及欲获的资讯而定。

(7)故障机构及根本原因确认(failure mechanism and root cause)。经上述步骤而了解故障的位置、形态、成分之后再根据之前的测试资料及相关信息可推测缺陷或异常如何造成故障,此为故障机构,至于此缺陷或异常如何产生则为根本原因确认。如此才能有效地把资讯回馈给相关部门,并以实际行动改善或防止故障的继续产生。

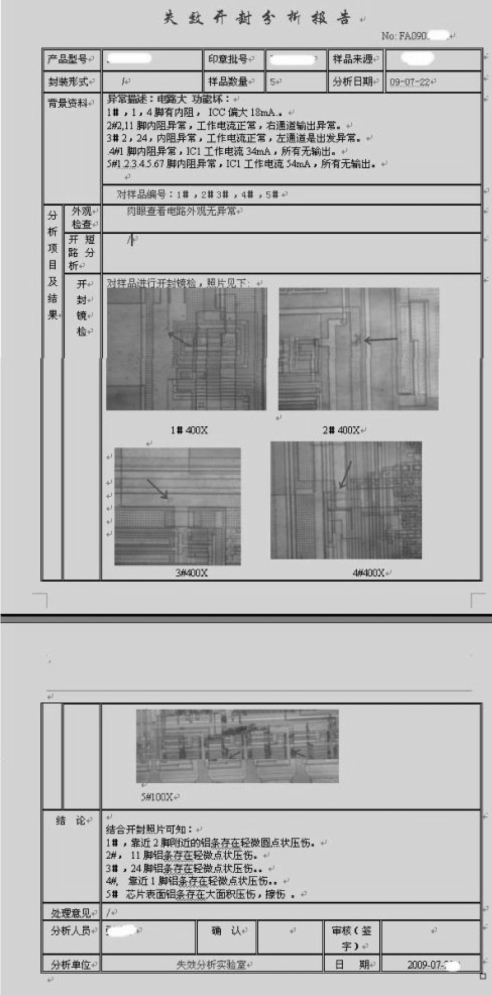

3.实际的FA分析报告

(1)举例:FA分析报告样例如图9-99所示。

(2)缺陷改造工程(defect reduction engineering)。当IC制成持续往轻、薄、短、小及高密度方向发展时,对任何缺陷容忍度将自然相对降低,也即其灵敏度将大幅提高,所以,想得到合格率的提升就必须设法降低缺陷密度。借助监测仪器系统对缺陷坐标、大小、外观等资料分析、归纳、传输功能的系统整合软件不断开发等统一应用,将可以较为有效地建立完备的缺陷来源分析归纳的回报流程,如此,也才能更为快速地找到缺陷发生的源头。

4.常用缺陷量度指标

常用缺陷量度指标是指yield、defect density(D0)和AQQ(average outgoing quality)。一般而言,合格率Yield与Defect Density间存在着一定的关系,取决于Die的大小与工艺难易度、线路设计、暴露面积等因素

![]()

式中,A:Chip面积;D0:缺陷密度;U:Layout使用率(utilization);n:工艺难易因子。但整体而言,合格率越高,缺陷密度自然也就越低,而所谓缺陷密度即单位面积上的缺陷数目,故此D0值就被用来度量工艺成熟度的指标。

每片晶片制造完成,即将出货给客户前,均必须经过光学显微镜的外观检查,而检查点通常设定为晶片上、中、下、左、右五个位置,检查结果将予以登记,并设定允收/报废标准(通常为缺陷点≤2点晶片,才达允收标准)而此AQQ值即为度量允收晶片上缺陷点数的水准,其值

(https://www.xing528.com)

(https://www.xing528.com)

图9-99 失效开封分析报告

5.常见监测缺陷源头方法

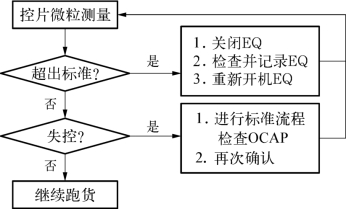

(1)设备状态微粒监测。针对制造晶片的机台,不论是以制造晶片数、批数、次数或是时间为区段,均会设定以控片(control wafer,通常为硅晶片)测量机台Particle数量的inline monitor,以检定机台状况是否处于可run货的较佳时期,并可据此设定工艺统计管制图(SPC chart)长期观察改善。此管制图上设定管制规格及当机标准,并往下展开设定超出规格的标准检查作业流程,通常称之为OCAP(out of control action plan),故能对线上机台状况提供较佳保障,其工作流程如图9-100所示。

图9-100 工艺统计管制

(2)在线微粒监控ISPM(in-situ particle monitor)。这种微粒监测方法目前正迅速发展,其最大优势就在于可以实时报告微粒的状况。这样就可以帮助机台负责人查清微粒产生时间,便于配方最优化调整,并可评估清机时机、频率及清机手法是否恰当。

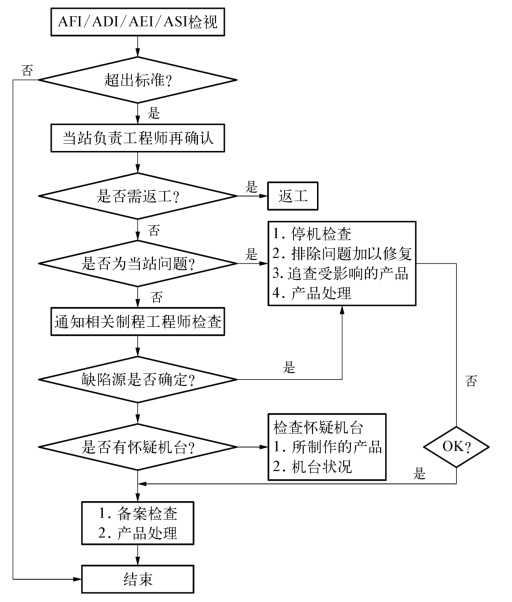

(3)工艺过程监测(in line monitor)。借由光学显微镜观察:晶片在制造过程中,往往会在较critical站别,设立检查点,透过定点外观察检查以确定晶片上是否有额外缺陷产生,或是工艺上出现异常,以便及早发现,加强gating以降低可能带来的冲击,保障产品的品质,而这些检查点因功能及站别不同分别区分为:

①AFI(after film inspection):观察淀积一层film后的外观;

②ADI(after develop inspection):光阻显像后圆形的外观检查;

③AEI(after etch inspection):layer被蚀刻后的外观检查;

④ASI(after strip inspection):蚀刻后,光阻是否去除干净的外观检查。

其工作流程图如图9-101所示。

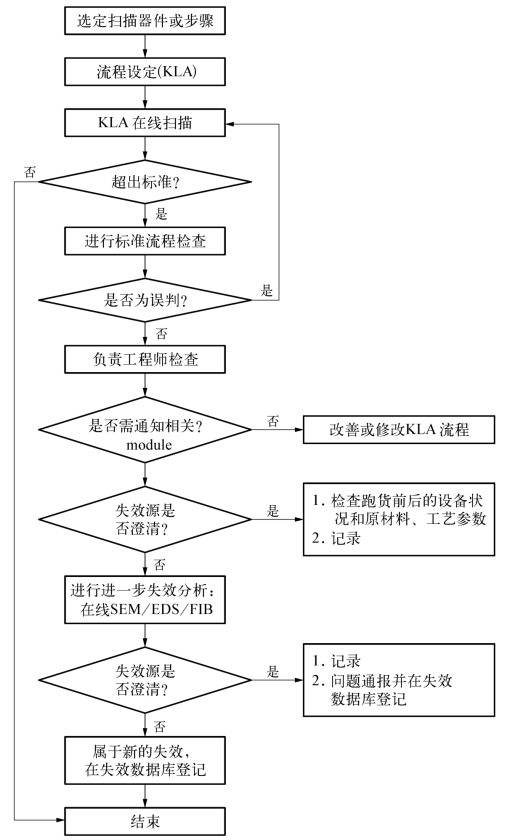

借由KLA或是Inspex或是Tencor作扫描:

KLA扫描产品寻求缺陷的方式已广泛应用于各大IC晶片制造厂,尤其是制DRAM的Fab,其配置大约呈2至3台Stepper置1台KLA,而其工作原理乃是利用影像对比方式,两两相比找出异常点。在不断改进扫描影像比对处理后,其扫描晶片时间已大幅缩短,再加上应用软件不断开发[例如,可区别聚集或非聚集缺陷的功能,可提供取样Review计划的功能,可提供当站缺陷贡献量——defect source analysis(DSA)的功能,甚至增加人工智慧来做缺陷形态自动分类——auto defect classify(ADC)]此检视仪器展现有效的缺陷源头的搜寻能力,而其扫描Data也极具代表性,其工作流程如图9-102所示。另外,线上尚有一些常被应用于镀膜后的扫描机台,如Inspex或是Tencor,其原理乃是靠入射的laser beam招致异常点反射而找到发生的位置。有些IC制造厂将其纳入KLA Scan系统,互相整合,共同担负起搜寻缺陷的重大责任。

图9-101 光学显微镜观察流程

(4)阶段性工艺考量Short loop test(Snake Pattern)。通常IC工艺愈到后段对缺陷容忍度越低,也即其对合格率杀伤力也就越强。因此,往往会额外用一小段工艺来模拟实际线上流程生产可供电性测量的晶片,以电性测量值的大小结合外观检查及进一步失败分析来定位缺陷所在,达到线上缺陷监测的目的,常用的圆形为相互交错的绵延细线,外观状如Snake,故以此称之。

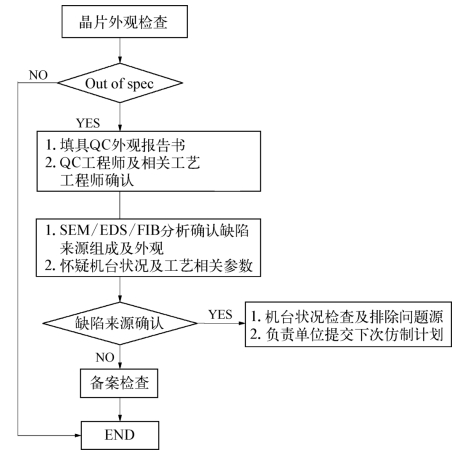

(5)QC Outgoing检查。QC是英文QUALITY CONTROL的缩写,中文“质量控制”。每片晶片制造完成后均会通过品管的外观检查,而检查后的结果均可提供线上所在的线索,方便进一步的解析,其检查流程如图9-103所示。

图9-102 KLA扫描流程

图9-103 Quality ciugoing control检查流程

6.监测与缺陷分析系统集成

前面已提及现行用以反映和监测缺陷的途径与方式很多,而它们之间如何互通信息,如何与最终合格率测试结果对比,以及如何与分析仪器串接,将缺陷位置快速且准确地定位,以利于进一步检查与分析等,这样的需求越来越紧迫,也越来越重要。

这方面集成的系统,已在市场上被不断地开发。目前已商业化的有KLA的“Quest”系统,YMS的“Knights”系统及Inspex的“DMS-Ⅱ”系统。它们的主要理念就是可在线看到任何缺陷,并可通过网络存入资料库。如果需进一步分析就可通过网络从资料库中提取,以方便定位,连接到线上的SEM、FIB、EDX、……,也可经过运算对比其最终的合格率测试结果,估算出各层次各类型缺陷杀伤合格率的能力(killer ratio),并可进一步建立起合格率预估的经验式。可以方便整体资源更有效地运用,以更快速根除缺陷进而提高产品的合格率。

7.缺陷改善的方法

缺陷数量多少与合格率高低极为相关,因此降低缺陷密度,将带来合格率的提升,但是,这项改善的工作将会是一项持续不断永无止境的差事,由此,如何形成有效正向回馈的回路,将是此工作未来能否成功的最重要因素所在。

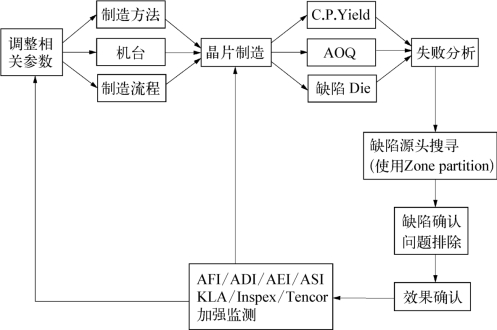

首先,确立与有效执行缺陷监测系统,这些系统包含在线AFI/ADI/AEI/ASI及KLA/Inspex/TencorScan,出货前的外观检查,以及合格率测试完成后的Failure Bit分析,当这些耳目确立后,接下来就是如何于缺陷被发觉观测到后,能以最快速有效方式加以归纳分析对比,找到可能的缺陷发生源,这时,最常被引用的手法就是区段法,这种方法是将整段工艺分割成数段区间,通过确认区段贡献量来将缺陷可能发生源头凸显出来,从而一举找到缺陷的源头。

而这些缺陷源头的发现,通常会再加以效果确认,以确定问题是否完全被排除,另外这些缺陷产生机构及机台均会再反馈到线上以便加强监测,防止再次发生,其整个持续改善的回路如图9-104所示。

图9-104 缺陷改善回路

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。