在IC工艺中用来制作薄膜的技术有化学气相淀积法(chemical vapor deposition,CVD),物理气相淀积法(physical vapor deposition,PVD)及旋转涂布法(Spin Coating)等。当IC的线路愈来愈细小时,使用物理气相淀积法已无法达到薄膜平坦度及均匀度的要求,而CVD确拥有薄膜厚度均匀性及平坦度的优点,因此CVD已变成薄膜淀积法技术的主流。而旋转涂布法则较常用于光阻,SOG和Polyimide的制作。

所谓CVD工艺是利用化学反应的方式,将反应物淀积成晶片表面形成薄膜的一种技术。目前在IC工艺的研究上用CVD技术来淀积薄膜可分为下列如下三类:

①绝缘与隔离类薄膜材料:如Si3N4、PSG、BPSG、FxSiOy,以及Parylene等;

②栅介质薄膜:SiO、SiON、HfO、铁电体系列等;

③金属膜:如Al、Cu、W等。

以下着重介绍这三类材料的基本性质。关于这三类材料的制造工艺,请参考薄膜淀积和薄膜刻蚀相关章节。

1.介电材料

介电材料是指一物质当施加一电场于其上时,物质内会产生电荷流动,而当移去电场时,电荷流动的方向恰与原来相反,具有此种性质的材料称之介电材料。高分子材料通常为介电材料。而介电常数通常可定义为在两片平行板间置一介电物质与真空下电容之比值。由莫耳折射与分子结构的关系可知若高分子材料的分子结构单位体积中拥有较多的极性基,则其介电常数较大,如硫、氮等,若拥有极性较低的氟原子,则其介电常数较低。因此在设计一低介电常数高分子材料时可依据上述理论先行估算其介电常数。

介电常数通常会受到湿度极大的影响,如当湿度由0%增加至100%时,聚酰亚胺的介电常数可由3.1增加至4.1。这是因为聚酰亚胺的分子结构中拥有羰基的缘故,此可由聚奎林(Polyquinoline)的介电常数因湿度而增加的比率较聚酰亚胺为少可得知。

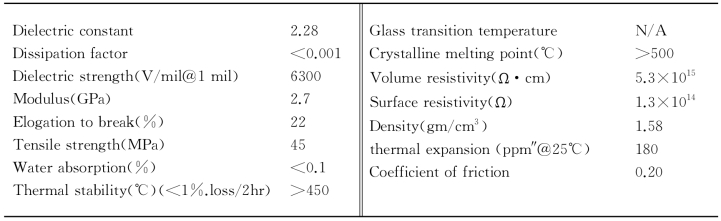

电绝缘、隔离类、低介电常数类材料在其电气性质、机械性质、化学性质及热性质有严谨的要求,如薄膜材料的介电损失要低,拥有良好的平坦度、与其他材料接触良好,吸湿性低、耐热性良好,且能够由低毒性的溶剂加工成膜等。高分子材料若要成为电绝缘、隔离类、低介电常数薄膜材料的候选者,须经由分子设计、合成及加工制作出各种性质均能合乎要求的材料。各种不同类型的介电材料有如下几种。

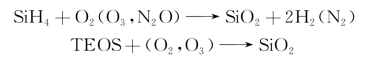

(1)SiO2。使用CVD技术淀积的SiO2薄膜通常可使用两种前导化合物,一种是SiH4,另一种是四乙氧基硅烷TEOS(tetraethoxy sliane),其化学反应式

SiH4为气体,较不稳定且危险,而且其所生成的薄膜阶梯覆盖的能力较差,因此目前已较少被半导体业界所使用。而TEOS是有机液体较稳定且可拥有良好的阶梯覆盖能力,因此是目前用来成长SiO2薄膜最常用的前导化合物,缺点是需较高的裂解温度(650~750℃)为其弱点。

(2)BPSG,硼磷硅玻璃(Boron Phosphate Silicate Glass)。若在SiO2薄膜中加入少量的硼和磷,可降低其玻璃转化温度,而再借由高温的热流增加其平坦度。目前在半导体工业上通常是将TEOS与三甲基亚磷酸TMPI[trimethylphosphite P(OCH3)3]及三甲基硼酸TMB[trimethyl borate,B(OCH3)3]使用CVD技术而成长掺杂硼和磷成分的BPSG,其反应式

![]()

其中的TMPI可使用TMPO(trimethyl phosphate,PO(OCH3)3)取代。这三种前导化合物均属于稳定的液体,而因BPSG含有硼及磷降低了玻璃转化温度,因此再经由热流处理后,可得到相当好的平坦度而广泛地使用于半导体工艺中。

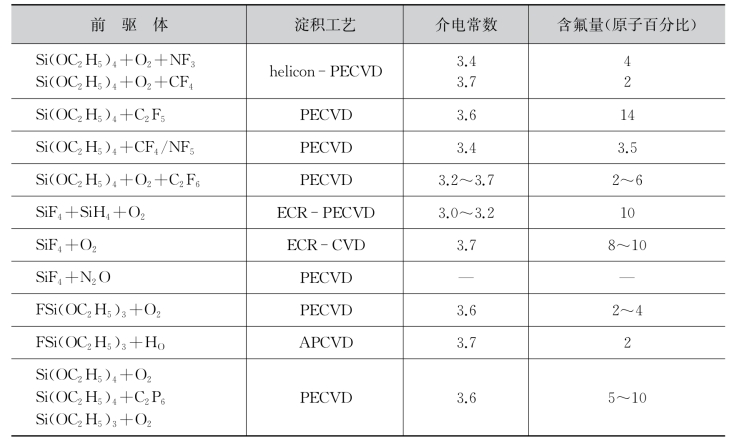

(3)FxSiOy,氟化二氧化硅。在IC元件趋于复杂及多重金属导线工艺的需求下,低介电常数的介电材料已是目前研究的热门题目,因其可降低电容及防止Crosstalk的干扰。而作为一低介电常数的材料通常必须具备下列条件:低介电常数、低机械应力、高耐热性(>450℃)及低吸湿性。目前最符合上述条件的材料为氟化二氧化硅。氟原子因其极性较低,因此加入SiO2后可大幅度降低介电常数。表9-5所列是目前使用CVD工艺所得氟化二氧化硅薄膜,介电常数约在3.0~3.7之间。而所使用的CVD工艺包含等离子体激发(PECVD),高密度PECVD及常压PECVD等,其前导化合物包含TEOS及各种氟化物如NF3、CF4、C2F6及FTES(fluoro triethoxy silane)等。虽然目前有关于FxSiOy薄膜的制作已相当成熟,然而其介电常数大致仅可降低至2.0左右,这对于0.18μm及0.13μm IC工艺所需的介电常数并不符合需求,因此相信未来将有更多关于低介电常数、介电材料的研究。

表9-5 薄膜制作使用的前驱化合物工艺种类、介电常数及含氧量

(4)Si3N4。Si3N4主要是用来作为SiO2层的刻蚀幕罩(mask)是半导体工艺中常见的介电材料,由于Si3N4拥有不易被氧渗透,对碱金属离子的防堵能力很好且不易被水气渗透,所以广泛地被用为半导体的保护层。

一般而言Si3N4的淀积是利用SiH2C12搭配NH3,在适当温度及低压下而得薄膜材质,如下式

![]()

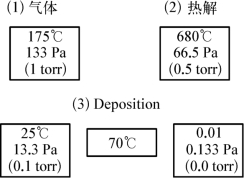

图9-23 Parylerie制造过程[12](https://www.xing528.com)

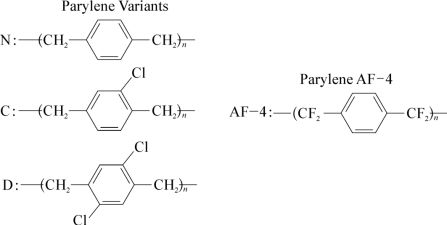

(5)Parylene(聚对二甲苯基类高分子)。Parylene已在印刷电路板工业被广泛地使用近20年,而近年它亦被视为内连线低介电常数材料的优良候选者,因它拥有低介电常数、低应力、低吸湿性且抗化学药品性极佳,而其较大的缺点是其加工过程较繁复及平坦度的控制。图9-23是Parylene的制造过程,首先将对二甲苯的二聚物气化,而后于气相中聚合再淀积成膜。一般常见的Parylene系列材料为Parylene N,C及D(见图9-24)。由specialty coating system,Inc.所推出AF4,其不仅拥有低介电常数2.28,且抗湿性及平坦度极佳,目前已推广至半导体厂试用中。AF4之结构如图9-24,而其性质如表9-6所示。

图9-24 Parylerie系列介电材料之基本结构

表9-6 Parylene AF4的基本性质

2.高介电常数栅薄膜材料

随着对IC元件等比例缩小(Scaling Down)的需求,当半导体技术进入45 nm时代以后,传统的单纯降低SiO2厚度的方法遇到了前所未有的挑战,因为这时候栅介质SiO2的厚度已经很薄(<2 nm),栅极漏电流中的隧道穿透机制已经起到主导作用。这时,随着SiO2厚度的进一步降低,栅极漏电流也会以指数形式增长。当栅偏压为1 V时,栅极漏电流从栅极氧化层厚度为3.5 nm时的1E-12 A/cm2陡增到了1.5 nm时的1E-2 A/cm2,即当栅氧化层的厚度减小约1倍时,漏电流的大小增长了12个数量级。而抑制栅介质SiO2厚度减小的趋势之一,就是提高栅介质的介电系数k。因为传统栅介质SiO2的k值是3.9,而HfOx系列的高k栅介质值可达20左右,因此发展高介电常数的介电材料成为关键问题。关于高k栅介质请参阅“第五章集成电路工艺的‘加法’:薄膜生长与淀积”这里不再赘述。

3.金属薄膜材料

使用CVD法来制备金属薄膜通常需要先导化学品(precursor)再经CVD工艺得到金属薄膜,请参阅薄膜淀积一章的详细介绍。

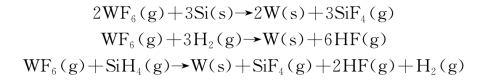

用来制备金属膜如钨、铝、铜及铁的CVD工艺分别如下数式。

(1)WCVD:

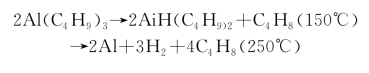

(2)AlCVD:

(3)CuCVD:

![]()

Cu(II):Cu(II)bis(b-diketonate)and Cu(II)bis(b-ketoiminate)

L:Single charged ligand(b-diketonate…)

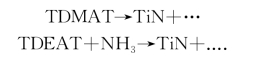

(4)TiCVD:

TDMAT:(tetrakis dimethye amino titanium)

TDEAT:(tetrakis diethyl amino titanium)

使用CVD来制作金属膜目前以Cu及W最吸引人注意,因为铜的导电度及抗电移性比铝高,所以未来深亚微米技术取代铝的可能性很高,而W-CVD则因其拥有强覆盖能力、高纯度(含氧量少)及高输出量而具有潜力。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。