1.评估方法:加速寿命测试

通常集成电路芯片的寿命多达几年。显然,我们不可能将集成电路芯片放在正常条件下运行几年再来判断这个产品是否有可靠性问题,并据此来投放市场。因此,可靠性评估通常会采用“加速法”即加速寿命测试(Accelerated life test),如高电压、高温等条件下进行测试,通常可在几秒到几天之内达到芯片运行几年的效果。

加速试验的前提是加速与正常运行的失效机理和模型一致。比如由于热电子注入引起的MOSFET器件源漏电流降低,其机理是热电子注入表面SiO2层。加大电压会加速这个注入效应,从而加速器件的老化。这种加速法是合理的,但如果电压过大,造成了MOSFET的雪崩导通。这种加速的失效机理和以上的热电子注入是不同的,因此加速法是不合理的。通常,在加速试验之前,需要进行一系列电学测量来确定加速方法成立的上限,比如,电压最大可以加到几伏,温度是多少,等等。

2.失效时间与失效率

通过加速试验得到的加速系数和失效机理的计算模型,可以推算出以上失效机理实际的平均失效时间(MTTF),以下是集成电路四种主要失效机制的MTTF的一般计算模型(其中AXX为加速系数):

式中,J为电流密度;T为温度;EaNBTI和EaEM是激活能;Vgs为栅极、源极、漏极的电压,其他为匹配系数。随着器件尺寸的进一步缩小,必须要考虑失效时间(寿命)的尺寸效应,这些会在下面的“失效机制”进一步讨论。

如果有多重加速因素,高温加高压,则加速系数A要考虑两项系数,如HCI失效机理的失效加速系数可以表征为

【例题8-2】

试比较MTTFEM在室温(300 K)和高温(150℃)的差别,激活能Ea=0.5 eV(Al)

【习题8-4】

如果连线材料用铜,其激活能为Ea=0.9 eV(Cu),试比较MTTFEM在室温(300 K)和高温(150℃)的差别。

另一项重要的表征可靠性的参数是FIT Rate(即每10亿小时失效的次数),FIT Rate是量度故障率的单位:

可以看到,FIT Rate和使用时间与使用条件密切相关,在加速试验的条件下失效率降低。

【习题8-5】

1000个MOSFET测试了一星期(24×7 h)后,出现了10个次品,假设加速系数为1,FIT Rate是多少?

3.失效机理

集成电路的失效机理主要分为前端工艺MOSFET的失效和后端工艺的导电金属和绝缘的失效。对于MOSFET,失效种类有:栅氧化层击穿TDDB,热电子注入(HCI)和负(正)偏压温度不稳定性NBTI等三种主要机制。而后端工艺,则有电迁移(EM)和绝缘层击穿(TDDB)两种主要失效机制。虽然失效的方式有所不同,失效的对象不外乎是栅介质(栅氧化层、high-k)金属绝缘介质(low-k)和连接金属。

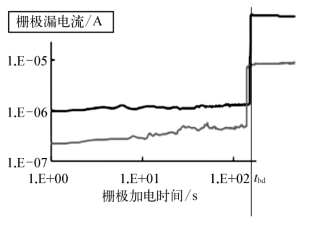

(1)TDDB。与时间相关电介质击穿(TDDB)测量是评估栅介质层质量的重要方法,一般说来,击穿是由于氧化硅中电场过高、电流过大,从而造成电荷累积引起的。栅介质内部及界面处在TDDB测试过程中发生缺陷的积累,当某一局部区域的缺陷数达到某一临界值,触发局部电流密度上升,即发生击穿。通常,栅介质层可以被认为有很多个这样小的局部区域并联组成,只要有一个局部区域发生击穿,整个氧化层就发生击穿。通过恒定电压法,恒定电流法和斜坡电压法在栅极加电,加电的时间越久,积累的电荷越多、电场越强,在氧化层中产生更多的陷阱或界面态,这些缺陷开始积累叠加,最后形成电流传导路径,漏电流开始剧烈上升,进而转至栅极到硅衬底的整个导通,导致整个元件失效,称为击穿(见图8-14)。

图8-14 栅极击穿的过程

图8-15 tbd的测量

如图8-15所示介质层击穿电荷的积累通常有一个临界点tbd:隧穿电子和空穴在氧化层中或界面附近产生陷阱、界面态,当陷阱密度超过临界点时,电流迅速上升并不可逆转,发生击穿。击穿电量tbd值表征了介质层的质量,一般采用以下模型:

式中,tbd为击穿时间;Ea为热激活能;Eox为栅电场强度;k为波尔兹曼常数;T为绝对温度;G为电场加速因子。

TDDB的失效概率遵从Weibull分布,其函数为

![]()

其中F(t)为失效概率,在实用中通常将F(t)转化为以下线性关系

![]()

图8-16 tbd的Weibull分布,CDF为对应的累积失效率

在TDDB测试中通常将样品置于不同的温度应力与电压应力下进行加速测试,栅氧化层TDDB特性的加电方法主要有恒定电流源、恒定电压源、斜坡电流源及斜坡电压源,通常选取F=63%(ln ln 1/1-F(t)=0)为失效标准。在得到了各应力水平下每个样品的寿命数据后,根据Weibull分布的参数估计方法可以得到Weibull分布斜率β和各应力下的尺度参数α,进一步通过加速模型可以得到正常使用应力下栅介质氧化层寿命分布,从而得到各累积失效率下的寿命估计。

栅氧抗电性能不好将引起MOS器件电参数不稳定,如:阈值电压漂移,跨导下降、漏电流增加等,进一步可引起栅氧的击穿,导致器件的失效,使整个集成电路陷入瘫痪状态。TDDB是制约集成电路可靠性的主要因素。TDDB的早期失效分布可以反映工艺引入的缺陷。TDDB可以直接评估氧化、氮化、清洗、刻蚀等工艺对厚度小于10 nm的栅介质质量的影响。

(2)HCI(hot carrier injection)。热电子注入(HCI)是指靠近漏极的沟道导电电子在高电场下被加速到一定的能量,进而注入栅氧化层引起的一系列器件性能的变化。随着大规模集成电路的集成度的提高,芯片尺寸的成比例减小,而芯片的工作电压并没有按比例减少,所以相应的电场强度增加了,导致了电子的加速能量增加。由于电子的加速过程比空穴要快很多,所以,在通常状况下,只考虑nMOSFET的热电子HCI效应。当电子的能量足够高的时候,就可以产生“离化效应”,即激发价带的电子而产生新的电子空穴对,空穴会随着电场流入硅衬底,而产生的电子会被进一步加速。当能量足够高的时候,电子可以越过栅介质势垒而注入栅极介质层内。这些注入的电荷及产生的缺陷会造成器件阈值电压Vt的漂移和沟道迁移率的下降,从而造成MOSFET沟道电流(Idsat)的减小。驱动电流Idsat的减小直接影响器件和电路运行的速度,影响电路的时钟次序,造成系统的可靠性问题,最后会导致系统“停摆”。

图8-17表示热电子注入的过程和MOSFET漏端的高电场分布。热电子注入经历了由A到D的过程:A:电子加热过程;B:电子转向过程;C:电子越过Si/SiO2势垒并在SiO2中造成缺陷;D:电子陷落在SiO2之中。

图8-17 热电子注入的过程和MOSFET漏端的高电场分布

(a)热电子的产生和注入过程A→D(b)计算机模拟的漏端高电场分布图,横轴为MOSFET的尺度范围,纵轴为电场强度

度量HCI的方法通常是驱动电流对于初始值相对减小,这个驱动电流随时间的蜕化通常遵循以下的公式

(https://www.xing528.com)

(https://www.xing528.com)

其中Ion是驱动电流(也称Idsat),Lpoly是MOSFET沟道长度,VDS是源漏极偏压,teq是有效的HCI作用时间,其他为匹配常数。

在实际应用的CMOS电路中,有效的HCI时间和CMOS的转换频率和动态特性(上升与下降时间)有关,HCI的作用只在短暂的开与关过程里。而在直流的HCI可靠性测量中,teq就是实际的nMOSFET加压时间。图8-18(a)中显示了不同栅电压强度下,Idsat随时间的退化实验曲线。A.U.是随机单位,一般在公开发表的文献中少见,这些数值与商业机密有关,通常是不公开的。

【例题8-3】在热电子注入(HCI)实验中,得到两条寿命加速曲线如图8-18(b)。加速试验的电压为1.6 V、1.7 V和1.8 V,试估算公式(8-5)中的电压加速系数(曲线Vmonitor:1.0 V)。

【答】根据曲线可得在1.6 V和1.8 V的Lifetime分别为2E7和7E8,根据公式(8-5)可得:

图8-18 热电子注入(HCl)实验

(a)驱动电流随着注入时间的增加而减小,所加偏压越大,热电子效应越强,驱动电流减小越多(b)寿命推算曲线

电压加速系数A=ln(MTTF2/MTTF1)/(V2-V1)=ln(7E8/2E7)/(1.8-1.6)=17

【习题8-6】利用以上的电压加速系数,求Vstress=1.2 V时的MTTF(lifetime)。如果在测量中的监控电压是1.5 V(图8-18(b)中,Vmonitor:1.5 V的曲线),比较一下在Vstress=1.2 V时的MTTF。

从公式(8-10)亦可推算出器件的寿命Lifetime(MTTF):

![]()

式中,A,B和激活能Ea都是寿命加速系数,用这个公式,可以在规定的范围内推算器件在某个工作电压,某个沟道长度的寿命。如在图8-18(b)中,热电子注入实验的电压是在1.6~1.8 V之间,而器件的工作电压是1 V,可以预算到寿命会相差超过4~5个量级。

(3)NBTI负偏压温度不稳定性(NBTI,negative bias temperature instability)。NBTI效应是指PMOSFET在负栅压及一定温度作用下引起的一系列电学参数的退化。我们都知道,当今的集成电路都以CMOS为主(尤其是数字集成电路)。在CMOS中PMOS的栅极电压常常是负的,而NBTI效应恰恰是产生在PMOSFET负栅压的工作状态下。NBTI效应的产生过程主要涉及正电荷的产生和钝化,即界面陷阱电荷和氧化层固定正电荷的产生以及扩散物质的扩散过程,由于在界面存在大量的Si-H键,热激发的空穴与Si-H键作用生成H原子,而由于H原子的不稳定性,两个H原子就会结合,以氢气分子的形式释放,从而在界面留下悬挂键,从而引起阈值电压的负向漂移。

在NBTI可靠性加速试验[见图8-19(a)],会在高温下对pMOSFET施加过载的负栅压(一般应力条件为125℃恒温下栅氧电场,源、漏极和衬底接地)。加速的NBTI效应通常会引起阈值电压Vt的负向漂移[见图8-19(b)]而造成pMOSFET的器件退化。图8-19(b)中也比较了nMOSFET正负栅压和pMOSFET的正栅压Vt漂移特性,可以清楚地看到,对于45~90 nm的集成电路工艺的SiON氧化层体系,只有pMOSFET的NBTI是明显的。至于未来的金属栅高介质栅介质极工艺(high k Metal Gate),需要对各类偏压

图8-19 NBTI可靠性加速试验

(a)NBTI的实验设置(b)90 nm集成电路工艺的SiON氧化栅层的NBTI的Vt(Threshold Voltage)迁移现象

状况下的nMOSFET和pMOSFET的Vt漂移重新考量。

NBTI除了和偏压、时间和温度密切相关之外,也会受器件的尺寸的影响:

式中,Vg、Tj、t代表偏压、温度和时间,而tox、WD、LD是尺度参数,分别代表栅介质的厚度,沟道宽度和长度。其他变量皆为试验参数。

【例题8-4】

在式(8-12)中,假定试验参数B,C=0.02,0.03,激活能Ea=0.12 eV,场强参数A=2.6,时间常数n=0.18,K=20 V,试估算pMOSFET,W/L=1μm/0.0901μm,tox=2 nm的Vt偏移量。这里Vg=1 V,温度是室温300 K,时间为10年(=3.2×108s)

【答】

【习题8-7】

对于上面的pMOSFET,在相同的工作条件下如果ΔVt漂移了100 mV,寿命t是多少?

随着器件尺寸的不断减小,尤其是为了提高栅氧化层的介电常数而引入的新工艺,如SiOxNy或high-k,SiOxNy或high-k可代替SiO2作为栅介质,这主要是由于它们的介电常数比SiO2要高,在相同的等效栅氧化层厚度下,物理厚度大于SiO2,从而有效地降低栅极漏电流和静态功耗,但也同时需要重新考量MOS器件的NBTI及PBTI效应。通常NBTI或PBTI效应会变得愈发明显,对CMOS器件和电路可靠性的影响也愈发严重,成为限制器件及电路寿命的主要因素之一。因此,研究NBTI和PBTI效应的退化现象并从中找出其内在的产生机理进而提出抑制或消除其效应的有效措施,是当前集成电路(IC)设计者和生产者所面临的迫切问题。

(4)金属导线电迁移EM(electro migration)。电迁移(EM)是微电子器件中主要的重要失效机理之一,电迁移造成金属导线的开路和金属连接线之间的短路和漏电流增加,从而导致器件失效。在器件向纳米尺度发展后,金属线的宽度不断减小,电流密度不断增加,EM现象更为严重。集成电路更易于因电迁移效应而失效。因此,随着集成电路后端工艺的纳米化发展,对EM的可靠性评估备受重视。

导致电迁移的直接原因是金属原子[铝原子(Al)或铜原子(Cu)]在高速流动的电子作用下产生的移动。如图8-20所示,当电流通过金属导线时,电子会撞击金属原子,使得金属原子产生移动,当金属原子离开其原有的位置,会在原有位置产生空缺,形成空洞,引起导线的横截面减小造成电阻增加,进而造成速度特性退化。当空洞逐渐累积到与金属导线的宽度相同时,就会使金属导线断路,而引起电路失效。另一方面,被推离的金属原子会堆积在金属线的另一端形成小丘(hillock),造成金属导线与邻近的金属导线发生短路。所以,电迁移效应会分别引起金属互连线的开路或短路。

图8-20 电子流(电流)流动在金属线中造成的电迁移现象

(a)小丘(hillock)和空位(void)的产生过程(A:导线中的Al或Cu原子)(b)金属线的小丘与空位的SEM图片

电迁移是金属线在电流和温度作用下产生的金属迁移现象,电迁移在高电流密度和高频率变化的连线上比较容易产生,如电源、时钟线等。为了避免电迁移效应,可以增加高电流流量处的连线的宽度和高度,以保证通过连线的电流密度小于一个确定的值。高的工作与环境温度环境也会加剧电迁移现象。

加速寿命试验也是电迁移可靠性试验分析测试的主要手段之一,该方法在较高电流和温度条件下,通过测量互连样品电阻随时间的变化,采用合适的阻值失效判据,获得互联样品电迁移失效时间,并应用统计分布求解累积失效分布得到失效中位寿命,进而利用Black方程得到电迁移扩散激活能。

式中,t50是失效率在50%对应的失效时间;J是电流密度;Ea是激活能;T是温度;k是波尔兹曼常数;A和n都是与材料和结构有关的实验拟合常数。

【习题8-8】估算图8-21中铝和铜的t50。

当前的集成电路工艺多用铜来代替常规的铝来做互联线。铜的电阻系数比铝降低了40%。另外,铜的熔点约为1090℃,高于铝的约为660℃。铜除了在电性上优于铝的特性外,在电子迁移的可靠度亦较铝为佳(高出两个量级)。这是因铜原子较铝原子重不易移动,且其导电性与散热性较佳的缘故。

图8-21 Al和Cu电迁移特性比较(J=2.5 MA/cm2,T=300℃)

虽然铜导线比铝导线有上述的优点,但是不能用沿用传统的铝导线刻蚀制造工艺。铜工艺与铝工艺完全不同,铝工艺通常是首先将铝淀积成金属薄膜,蚀刻后再淀积上绝缘的电介质;而铜工艺是采用嵌入式工艺(damascene)得到图形化的导线,这一制程实际上是在绝缘层上刻蚀出图形化的连线,然后“浇铸”铜,之后再对表面进行电化学磨平处理以“磨掉”多余的铜,最后形成图形化的导线。需要强调的是,这个过程必须包括钝化层的制作。因为铜的扩散速度很快,很容易在电介质内部移动使器件“中毒”,因此紧接着要淀积一层扩散阻障层(通常是TaN),再淀积一层过渡层,然后才是铜层。过渡层连接铜层的作用是使Cu与TaN形成稳定的固化电镀淀积反应。原子层淀积(ALD,atomic layer deposition)技术是目前淀积阻挡层和过渡层的制作工艺。当芯片的特征尺寸变为65 nm或者更小时,阻挡层和过渡层的等比例缩小将面临严重困难,铜导线的宽度和高度分别为90 nm和150 nm,阻挡层和过渡层仅有10 nm。使用ALD技术能够在高深宽比结构薄膜淀积时具有100%台阶覆盖率,对淀积薄膜成分和厚度具有出色的控制能力,能获得纯度很高、质量很好的薄膜。

铜互连已经成为IC制造业的行业标准,使未来更小、更快的集成电路芯片能够成为现实。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。