1.概述

栅极有两个主要部分组成:上导电层(如金属栅极或多晶硅)和绝缘介质层(如氧化层、氮氧化层、高介质常数栅绝缘层)。应该说,栅层的制作历史走了一个ABA的循环:从铝金属栅极(NMOS)→多晶硅栅极(CMOS)→双金属栅极(CMOS)。

(1)Al+SiO2。最早期的MOSFET集成电路使用Al来做金属栅极,SiO2作为栅绝缘层。这个时期的SiO2多用热氧化的方法生成,而Al多为CVD方法淀积而成。由于当时采用的电路设计是基于单型nMOS或pMOS器件,CMOS还没有普及,系统和工艺都偏于简单。

(2)多晶硅+SiON。在20世纪90年代,由于CMOS的显著性能优势,多晶硅代替了Al作为导电栅极。这主要是利用了多晶硅的费米能级可以通过掺杂很方便地加以调整,使NMOS和PMOS可以很容易地集成在CMOS IC里。MOSFET的临界电压Vt(threshold voltage)主要由栅极与沟道Si衬底材料的功函数之间的差异来决定,而因为多晶硅本质上是半导体,所以可以藉由掺杂不同极性的杂质来改变其功函数。更重要的是,因为多晶硅栅极和其下的硅之间能隙相同,因此在降低PMOS或是NMOS的Vt时可以藉由直接调整多晶硅的功函数来达成需求(见图5-85)。

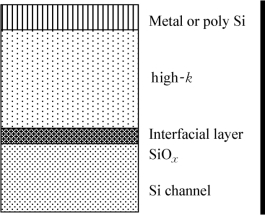

图5-85 MOSFET栅层的结构

多晶硅生长主要是以低压化学气相淀积法来进行,是以SiH4为反应气体在625℃下进行LPCVD进行淀积,低压多晶硅生长可减少气相化学反应,而降低沉粒及孔洞缺陷的生成。利用电子回旋共振及射频等离子体增强化学气相淀积可以在较低的温度下(低于400℃)下在SiO2栅极上长出多晶硅,该工艺具有膜厚均匀,纯度佳,经济效益高等优点。

多晶硅搭配SiO2栅介质及其后来的SiON栅介质,涵盖了集成电路发展的主要过程(从1995年到2011年)。引入SiON氮氧化硅的目的是与MOSFET器件的“等比例”缩小要求密切相关的。等比例缩小要求MOSFET器件的栅介质厚度需要按等比例减小,但当半导体技术进入90纳米时代以来,传统的单纯降低SiO2厚度的方法遇到了前所未有的挑战,因为这时候栅介质SiO2的厚度已经很薄(<2 nm),栅极漏电流中的隧道穿透机制已经起到主导作用并且栅极的漏电亦不可忽略,这时,栅极漏电流也会以指数形式随着SiO2厚度的降低而增长。当栅偏压为1V时,栅极漏电流从栅极氧化层厚度为3.5 nm时的1E-12 A/cm2陡增到了1.5 nm时的1E-2 A/cm2;即当栅氧化层的厚度减小约1倍时,漏电流的大小增长了12个数量级。而抑制栅介质SiO2厚度减小的趋势之一,就是提高栅介质的介电系数k。因为传统栅介质SiO2的k值是3.9,而纯的Si3N4的k值可达到7,通过SiO2氧化膜里掺入氮使之成为致密的SiON来提高栅介质的介电系数。氮原子的掺入还能有效地抑制硼等栅极掺杂原子在栅介质中的扩散。同时,该方法仍然采用SiO2作为栅介质的主体,因此与前期技术有良好的连续性和兼容性。

采用NO、ONO等堆栈结构可以增加栅电容的表面积以增大电容值,从而增加膜的物理厚度,达到减小漏电流、改善硼扩散和电容可靠性的问题。即便如此,制造出的膜厚也是有一定限度的,当小于1.5 nm后,器件的漏电流和电子隧道移动退化效应等问题就会出现。这时,人们又转为使用金属栅极与高介质常数栅绝缘层组合成第三代的集成电路栅极。

(3)HKMG(high-k Metal Gate),金属栅极与高介质常数栅介质。本来理想的情况应该是引入高介质常数栅介质但仍然使用Poly Si作为栅电极,但是多晶硅栅电极与高介质常数栅介质存在不可逾越的失配问题,所以必须利用金属栅电极可高介质常数栅介质进行搭配。金属栅极不能像多晶硅那样调整费米能级,所以对于NMOS和PMOS要利用两种不同功函数的金属材料。

2.高介质常数栅介质

取代传统的栅介质是一项非常艰巨而浩大的系统工程。传统的SiO2不仅能和Si形成近乎完美的界面,而且具有优异的机械、电学、介电和化学稳定性,还可以作为工艺过程中光刻和刻蚀过程中的保护层或阻挡层。并且人们已经对SiO2和Si间的理论模型和各种反应机理有了系统、全面而深入的研究。对于新型的高介电常数材料必须首先进行深入的预研,high-k材料必须满足下面的要求。

(1)高介电常数k(~20)来维持驱动电流而减小漏电流密度。

(2)较大的禁带宽度,与Si导带间的偏差大于1eV。

(3)与Si的匹配:在Si上有优良的化学稳定,在Si衬底上有良好的热力学稳定性,生产工艺过程中尽量不与Si发生反应,并且相互之间扩散要小。与Si界面质量应较好,新型介质材料必须与栅电极间的化学性能匹配。

(4)界面态:high-k介质材料与Si的界面之间的界面态密度和缺陷密度要低,尽量接近于SiO2与Si之间的界面质量,解决界面态引发的费米钉扎效应(Fermi Pinning Effect,使得金属栅的费米能级被钉扎Si禁带中央附近,无法实现双金属栅MOS器件所要求的阈值电压值)。

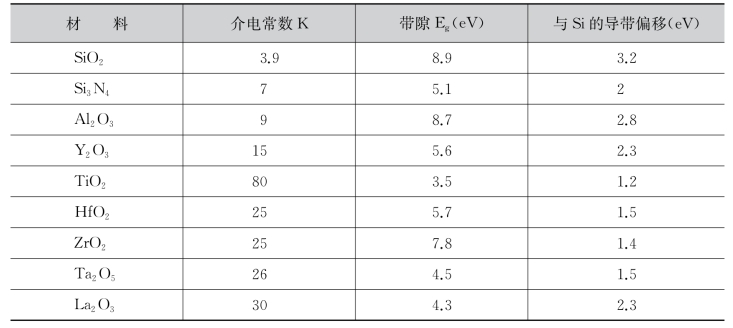

目前,研究的新型高hight-k材料主要包括Zr和Hf的氧化物和硅化物(见表5-7)。其中HfO2和ZrO2等过渡金属氧化物是近年来研究最为深入的栅介质材料,它们的禁带宽度以及与Si间的导带偏移量都满足对于下一代high-k栅介质材料的要求。IVB族金属氧化物HfO2和ZrO2薄膜具有相似的电子结构,这两种材料具有适中的介电常数k,理论值为20~25,比Si的介电常数3.9要大得多,为此可以在相同的等效氧化物厚度下具有较厚的物理厚度,这样可以减少隧穿的漏电流,从而提高器件的稳定性。除此之外,这两种材料还具有相对较宽的带宽、和Si之间合理的带隙偏移量以及在高温条件下在Si基材料上很好的热稳定性[1][2]。它们被视为在下一代的互补型金属—氧化物—半导体(CMOS)器件中,传统的SiO2栅介质材料的很好的替代材料。

表5-7 栅介质层的候选材料及相关特性

在high-k材料选取时,热稳定性也是一个重要指标,因为集成电路工艺中不可避免地会接触到高温,比如退火工艺,所以希望所选取的栅介质在高温下能保持非晶态以及不和衬底Si发生反应。除此以外,high-k栅介质与Si的界面质量也要很好以保证器件很好的工作。目前,任何一种有望替代HKMG的栅介质材料都不能完全满足这几点要求,任何一种新材料都表现出不同的特性,在器件的性能上都或多或少地存在某些不良的效果。作为候选的hight-k栅介质材料在CMOS器件的应用中,保持长达10年的可靠性也将成为科研工作者们所面临的一个挑战性问题。

3.新的金属栅电极

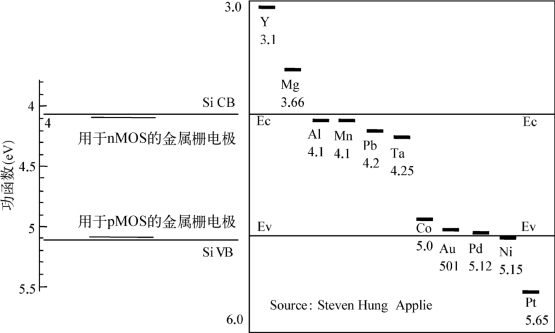

由于CMOS工艺需要同时具备NMOS和PMOS器件,所以采用high-k材料/金属栅电极需要用两种金属材料分别制作NMOS和PMOS,如图5-86所示,用于NMOS的金属功函数接近4 eV;用于PMOS的金属功函数接近5 eV。总的来说,HK/MG就是使用两种不同“功函数”的金属(用以确保满足Vt要求)和一种绝缘材料。调整NMOS和PMOS器件的Vt需要金属具备4.2 eV和5.2eV的功函数。所使用的金属也必须能够适应CMOS生产流程中为激活掺杂杂质而使用的高温热处理工艺。(https://www.xing528.com)

图5-86 新的金属栅电极材料

由于传统的CMOS制造工艺并不与金属栅电极兼容,因此需要一套新的低热预算(Thermal Budget)的CMOS栅极制造工艺,常采用镶嵌工艺(single damascene or dual damascene),将金属栅电极材料淀积在栅电极的沟槽中。对于金属栅淀积设备而言,则需要将物理气相淀积技术(PVD)和原子层淀积技术(ALD)两者相结合。通过整合两项技术,依赖原子层淀积技术(ALD)的超强台阶覆盖能力,能够对狭小的栅电极沟槽进行材料覆盖,紧接着再使用先进的物理气相淀积技术(PVD)生长金属薄膜。ALD、PVD金属和绝缘材料的淀积技术已经取得了重大的突破,依靠一些操作甚至能够根据需要调整器件的VT。

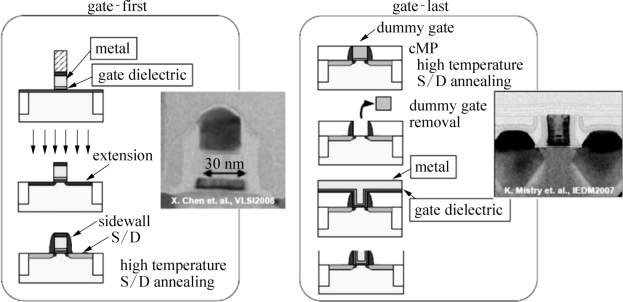

目前(2014年),HKMG在探讨gate-last和gate-first两种工艺技术(见图5-87)。gate-last金属栅极结构的技术特点是在对硅片进行漏/源区离子注入操作以及随后的高温退火工步完成之后再形成金属栅极;与此相对的是gat-first工艺,这种工艺的特点是在对硅片进行漏/源区离子注入操作以及随后的退火工步完成之前便生成金属栅极。由于退火工步需要进行数千度的高温处理,而gate-last工艺则可令金属栅极避开高温退火工步,因此相比gate-first工艺而言,前者对用于制作金属栅极的金属材料要求更低,不过相应的工艺技术也更复杂,Intel便是gate-last工艺的坚定支持者,而IBM/AMD则将采用gate-first工艺制作32 nm制程金属栅极。

图5-87 gate-first和gate-last工艺的比较

注:gate-last工艺的高温退火在栅极的形成之前,这是它的优点,但工艺较gate-first比较复杂。

4.关于栅层工艺的争论

(1)Clifford在IEDM会议上称:“high-k绝缘层天生就需要更多的掩膜层结构才可以制作出来,而这种结构相对复杂,很容易产生制造瑕疵,对制造者而言是一个挑战。”

不过高通并没有完全关上HKMG的门。Clifford表示:“仍然有一部分产品是需要采用HKMG技术制作的。”这其中包括为平板电脑以及部分“极高端”智能手机所设计的芯片产品。高通会选择在此类产品的运行频率需要提高到2 GHz左右时,再向这部分28 nm制程产品中引入HKMG技术。不过对大多数智能手机用芯片,高通则会坚持采用更便宜的poly/SiON技术制作芯片。

Clifford还强调称,虽然高通非常渴望自己设计的芯片产品能够采用更先进的工艺来制作,但是为追逐摩尔定律而必须启用这些工艺所需的如EUV光刻设备以及其他关联技术的研究方面的巨额成本投资却令高通十分担忧。Clifford说:“成本控制对我们而言非常重要。”

(2)从技术角度看,在IEDM会展期间,高通技术主管P.R.Chidambaram则在一份描述其28 nm技术的文件中称,如果某种用于制作HKMG的工艺无法为沟道提供足够的沟道应变力,那么采用这种工艺制造出来的晶体管其性能便无法比采用传统poly/SiON+强效沟道硅应变工艺制作的晶体管高出多少。他表示:“HKMG+强效沟道硅应变工艺的组合可以显著提升晶体管的速度,但是采用这种工艺的成本更高。因此这种工艺更适合于用在平板电脑或超高端智能手机的场合。而采用传统的poly/SiON工艺,则产品开发时间短,而且制程方面所负担的风险也更小,造出的芯片瑕疵密度也更低。”

目前大部分采用高通Snapdragon处理器核心设计的智能手机用芯片的运行频率均在1 GHz及以下的水平,而且还可以用启用双核设计的方法来进一步提升性能。高通公司的高级技术经理Geoff Yeap称高通目前售出的基于Snapdragon核心的芯片产品“数量非常巨大”,他还表示目前主要几家芯片代工厂在high-k工艺方面“都还准备不足”。

Yeap表示高通晚些时候会将其部分产品转向使用HKMG工艺制作。虽然HKMG晶体管由于反型层电荷的增加其驱动电流值也更大,但是也因此而增加了管子的开关电容,而对高通而言,晶体管工作在线性电流特性区的电流驱动能力(Idlin)要比工作在饱和区的电流驱动能力(Idsat)更为重要。

而虽然HKMG工艺对解决栅极的漏电问题帮助甚大,但是这种技术对硅衬底(substrate)以及漏源极的漏电却没有很大的改善。而高通则在其采用28 nm poly/SiON工艺的晶体管中采用了阱偏置技术(well biasing,一种可以改变衬底偏置电压,以减小衬底漏电的技术),以及包含门控时钟(clock gating,即在某模块空闲的时候可切断其时钟信号供应的控制门电路技术)和门控电源(power gating即为在某晶体管模块空闲的时候可彻底切断其电源供应的控制门电路技术)等技术在内的多种电路技术来控制芯片的漏电损耗。Chidambaram还介绍了该产品中应用的某种特殊的门控电源设计,并称这种技术是在高通和其未透露公司名的芯片代工伙伴的共同努力下开发出来的。

当然放开HKMG还是poly/SiON的话题不谈,光是从45 nm节点升级到28 nm节点,高通也可以从中获利不少,这部分相信大家都已经很清楚,这里不再赘述。

(3)外界的看法。在IEDM会议上,许多技术专家都为高通决定仍走poly/SiON工艺路线的决定感到惊讶,因为一般都认为HKMG可以更好地控制沟道性能,而且工艺升级余地也更大。总体上看,目前poly/SiON工艺遇到的主要障碍是栅氧化层的等效厚度由于栅极漏电等问题的存在从90 nm节点制程起便难以进一步缩小,以至于需要依赖硅应变技术来提升晶体管的速度,而HKMG则可以解决这个问题。

(4)关于高通28 nm产品代工商的推理分析:至于高通这些28 nm产品可能的代工商方面,台积电和GlobalFoundries都与高通有代工合作关系。而我们已经知道台积电将启用三种不同的28 nm制程工艺技术,这三种制程工艺分别是:1-“低功耗氮氧化硅栅极绝缘层(SiON)工艺”(代号28LP);2-“high-k+金属栅极(HKMG)高性能工艺”(代号28HP);3-“低功耗型HKMG工艺”(代号28HPL)。所以从台积电的情况看其28LP工艺正好满足高通28 nm产品的规格。

而据GlobalFoundries此前公布的工艺技术路线图显示,GlobalFoundries生产的28 nm低功耗(28 nmLP)及高性能(28 nmHP)芯片产品均会使用gate-first HKMG工艺。这样,除非GlobalFoundries没能代工大部分高通28 nm制程芯片,否则高通走28 nm poly/SiON工艺路线的决定,不免会令人猜测他们会不会为高通这个可以算作代工厂商最大客户的合作伙伴而对自己的工艺技术路线图做些修改。不过Clifford表示不愿为哪家厂商将代工其28 nm芯片产品作任何评论,称代工商的具体人选还在内部讨论的过程中。

有趣的是,尽管GlobalFoundries的发言人在IDEM会上大肆宣传称其28 nm工艺是基于gate-first HKMG工艺基础上的,但他又表示:“不过,我们也本着特事特办的精神,正在为满足某些来自特殊客户的特殊请求而为某些特殊产品提供基于28 nmPoly/SiON制程的代工,这类产品并不需要HKMG技术带来的性能提升和漏电降低优势。”而且GlobalFoundries也不会为28 nm Poly/SiON技术建立一整套完备的电路设计系统。

他还表示GlobalFoundries转向HKMG工艺的计划“仍然在正常进行中,我们认为这种工艺对客户的吸引力是非常大的。我们预计HKMG会成为28 nm低功耗移动设备用产品,以及28 nm高性能设备用产品的绝对主流工艺”。GlobalFoundries还称目前已经有多家客户的芯片产品处于硅片验证阶段,而且公司旗下的德累斯顿Fab1工厂也已经在测试相关的原型芯片,很快便会进入试产阶段。

GlobalFoundries与台积电目前因所用HKMG工艺的不同而在市场上火药味很浓:GlobalFoundries在28 nm会使用gate first型HKMG工艺,而台积电则会使用gate-last HKMG工艺。GlobalFoundries还宣称自己的gate-first HKMG工艺在成本方面要比台积电的gate-last HKMG工艺节能约10%~15%。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。