在一定的衬底上,用溅射、氧化、外延、蒸发、电镀等技术制成绝缘体、半导体、金属及合金等材料的薄膜,薄膜的厚度在纳米和微米之间。这种加工技术就是薄膜的淀积技术和薄膜生长技术。薄膜淀积是简单的厚度“加法”,薄膜的增长过程与基地或衬底没有相互作用,衬底材料的厚度没有改变或没有消耗;而薄膜生长技术则需要依托特定的衬底来完成,如硅的氧化过程是表面处氧化剂与Si原子起反应,生成新的SiO2层,氧化膜是以消耗Si衬底原子的方式进行的。在集成电路的制造过程中用得比较多的是薄膜淀积技术。

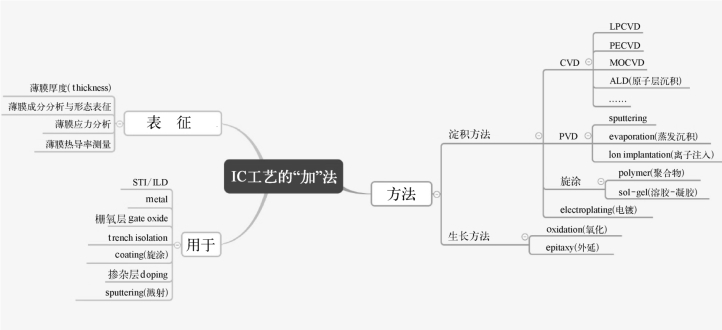

而就薄膜的形成方法而言,薄膜制造有淀积法和生长法两大类。薄膜淀积方法包括化学方法CVD(chemical vapor deposition)与物理气相淀积PVD(physical vapor deposition)。薄膜的生长技术则有氧化(oxidation)和外延(epitaxy)生长两大类,包括分子束与原子束外延技术和分子自组装技术等(见图5-1)。

图5-1 集成电路工业的加法

薄膜的淀积方法通常指薄膜的增长过程与基地或衬底没有相互作用,即在衬底材料上叠加一层或几层其他的材料,没有改变衬底材料的厚度及晶向状态。

薄膜生长则需要依托特定的衬底来完成,主要有氧化和外延两种。氧化是在硅片表面处氧化剂与Si原子起反应,生成新的SiO2层,使SiO2膜不断增厚,同时SiO2Si界面向Si内部推进。而外延技术则是在单晶衬底(基片)上生长一层与衬底晶向相同的单晶层,外延生长的新单晶层可在导电类型、电阻率等方面与衬底不同,从而大大提高器件设计的灵活性和器件的性能。

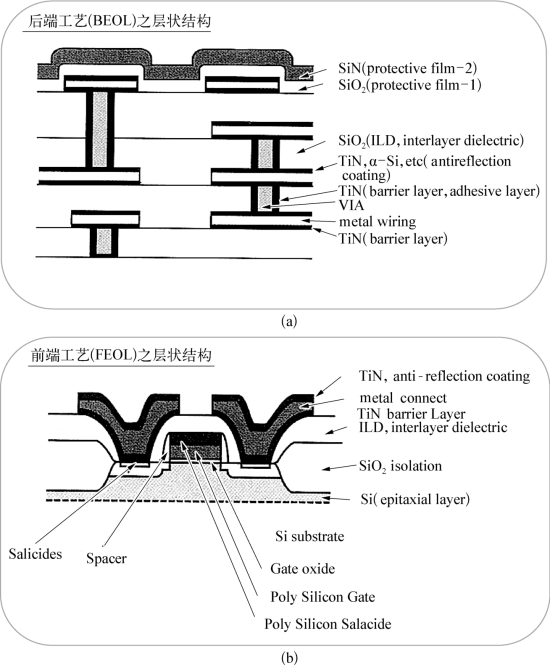

就功能而言,集成电路常用的有三类薄膜:金属薄膜、半导体薄膜和绝缘薄膜,分别实现器件之间的互连、半导体器件的结构制作和器件之间相互隔离等功能。图5-2为集成电路结构的各类薄膜层。总体上讲,集成电路的薄膜层分为前段工艺(FEOL,front end of line)和后端工艺(BEOL,back end of line)。前端工艺FEOL用于制作各类有源及无源器件,如MOSFET、电容、MEMS传感器等等;后端工艺BEOL负责器件之间、模块之间、系统之间的金属连线系统。由图5-2可以看出各集成电路功能层的图形化过程,包含了光刻、薄膜淀积与覆盖、薄膜的刻蚀和钝化等。也就是说,半导体在生产过程中所形成的薄膜不只是普通意义的平面膜,而是包含了淀积过程中对非均匀平面的覆盖和其后的图形化刻蚀,是一个带有一定图案的3D曲面膜。例如,在制作铜金属互连的过程中,铜层的淀积包含了填充接触孔和铜连线金属的淀积过程,铜的互联金属线和与下层链接的连接孔是在同一层的淀积和覆盖过程中完成的。(https://www.xing528.com)

图5-2 集成电路工业常用薄膜层的种类

(a)后端工艺(b)前端工艺

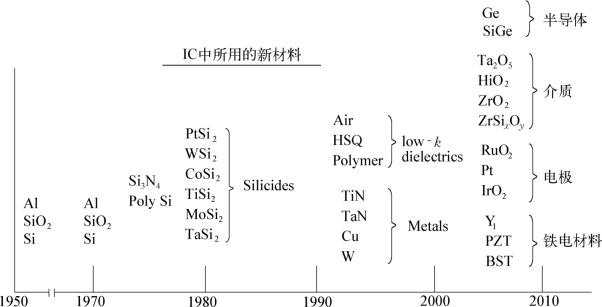

在集成电路的发展历程中以及在不同的发展阶段所常用的各类半导体薄膜种类见图5-3。从图5-3中可以看出,初期的集成电路技术以铝、二氧化硅和硅三种为主要材料,早期的研发力量主要集中在解决这三种材料及其接触界面的质量和制造工艺上,以实现有效而可靠的工业化的制造工艺。然后,20世纪八九十年代引入多晶硅(Poly Si)和金属硅化物(Salicide),从而促成了以CMOS为基础的革命性的发展。CMOS有静态功耗几乎为零便于集成和易于等比例缩小等优点,统领了0.8μm~90 nm好几代的CMOS集成电路发展阶段,是集成电路技术发展的主要和“黄金”阶段。21世纪初期,用铜(Copper,Cu)作为互连金属和用低介电常数(low-k)作为隔离介质大大减低了后端连线过程引入的速度阻抗,从而大大提高了集成电路和集成系统的综合速度,所以copper low k及其附加的界面缓冲层(TiN,TaN,…)成为21世纪初集成电路新材料的标志。到了2010年之后,薄膜技术有了长足的发展,尤其是ALD(atomic layer deposition)技术进入到集成电路的产业化链条,大大地提高了薄膜淀积的精确度和工程化能力。乘着更新的薄膜技术发展的“东风”,更多的新材料登上了集成电路制造的历史舞台,针对三种主要应用需求:高介电常数加金属栅极(high-k metal gate),高迁移率衬底材料(如GaAs与Ge)和MEMS器件与材料(来实现系统集成)。high-k metal gate主要解决硅工艺本身薄栅极本身的漏电带来的漏电功耗问题,高迁移率衬底为提高器件的速度“锦上添花”,而集成各类MEMS传感器与执行器系统则是多功能系统集成大方向的必然要求。

图5-3 集成电路各个发展阶段对于各类主要薄膜材料开发要求

注:集成电路各个发展阶段对于各类主要薄膜材料开发要求主要经历了四个大的阶段:传统的铝、氧化硅、硅系统(~1990年前),poly Si CMOS系统(~>1990年),Cu low-k(~>2004年),HKMG系统(~>2010年)。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。