器件的结构示意图如图4.20所示,在Si-GaAs基底上外延生长厚度为2μm、掺杂浓度为3×1016 cm-3的n GaAs,在此外延层上刻蚀出周期a=120μm、台阶宽度w=50μm、高度h=1μm的栅格结构。在每个栅格台阶上镀金作为负电极,且为肖特基接触;在栅格槽及芯片其他部分镀金作为正电极,也形成肖特基接触,并与栅格台阶保持5μm间隔。器件在电学上形成一个双肖特基接触阵列,而在光学上又形成一个周期性栅格的MSSPW结构。

图4.20

(a)器件的结构和在锥形平行平板波导中传输的示意图;(b)单元结构示意图

采用标准的半导体工艺加工该器件,工艺流程大致如下。

(1)设计器件图形并制成掩膜版。掩膜版分为图形互补的两版,第一个掩膜版用作正电极,第二个掩膜版的边沿比第一个掩膜版大5μm,用作负电极。

(2)制外延层。在2英寸Si-GaAs晶圆上使用分子束外延获得2μm厚的n-Ga As外延层。

(3)制正电极。涂胶,对第一个掩膜版进行光刻,曝光、显影后在晶圆上形成图形,蒸镀金属(10 nm厚的钛和100 nm厚的金),去胶、剥离带胶部分的金属,形成金属栅正电极。

(4)制栅格台阶。以金属栅为掩膜版进行刻蚀,形成栅格台阶。(https://www.xing528.com)

(5)制负电极。对第二个掩膜版进行光刻,重复第(3)步工艺,制作并形成负电极。

(6)切片。获得单块芯片,整个芯片工艺完成。

(7)蒸镀电极及焊接引线后完成器件制备过程。器件的实物照片与芯片的SEM图如图4.21和图4.22所示,整个器件几何尺寸约为1.5 cm×1.5 cm×0.2 cm。

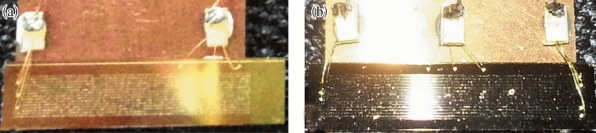

图4.21 器件的实物照片

(a)单正电极结构器件;(b)双正电极结构器件

图4.22 芯片的SEM图

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。