1.创建工程并设计输入

(1)在E:\project\目录下,新建名为BTimer的新工程。器件族类型(Device Family)选择Spartan-3E,器件型号(Device)选XC3S500E FG320-4,综合工具(Synthesis Tool)选XST(VHDL/Verilog),仿真器(Simulator)选ISim(VHDL/Verilog)。

(2)设计输入 在源代码窗口中单击鼠标右键,在弹出的快捷菜单中选择New Source,在弹出的对话框中选择Verilog Moudle,在右端的File name中输入源文件名BTimer,再依次单击Next-Next-Finish,然后在弹出的源代码编辑框内输入下面的源代码并保存即可。

为了在仿真器上更好地观察波形,只需要进行25000次分频即可。

设计的Verilog HDL代码详见光盘附件5-22。

2.功能仿真

(1)在源代码窗口中单击鼠标右键,在弹出的快捷菜单中选择NewSource,新建test-bench文件,选择Verilog Test Fixture,然后单击Next-Next-Finish,在弹出的testbench模板中编辑激励信号。编辑的激励信号代码详见光盘附件5-23。

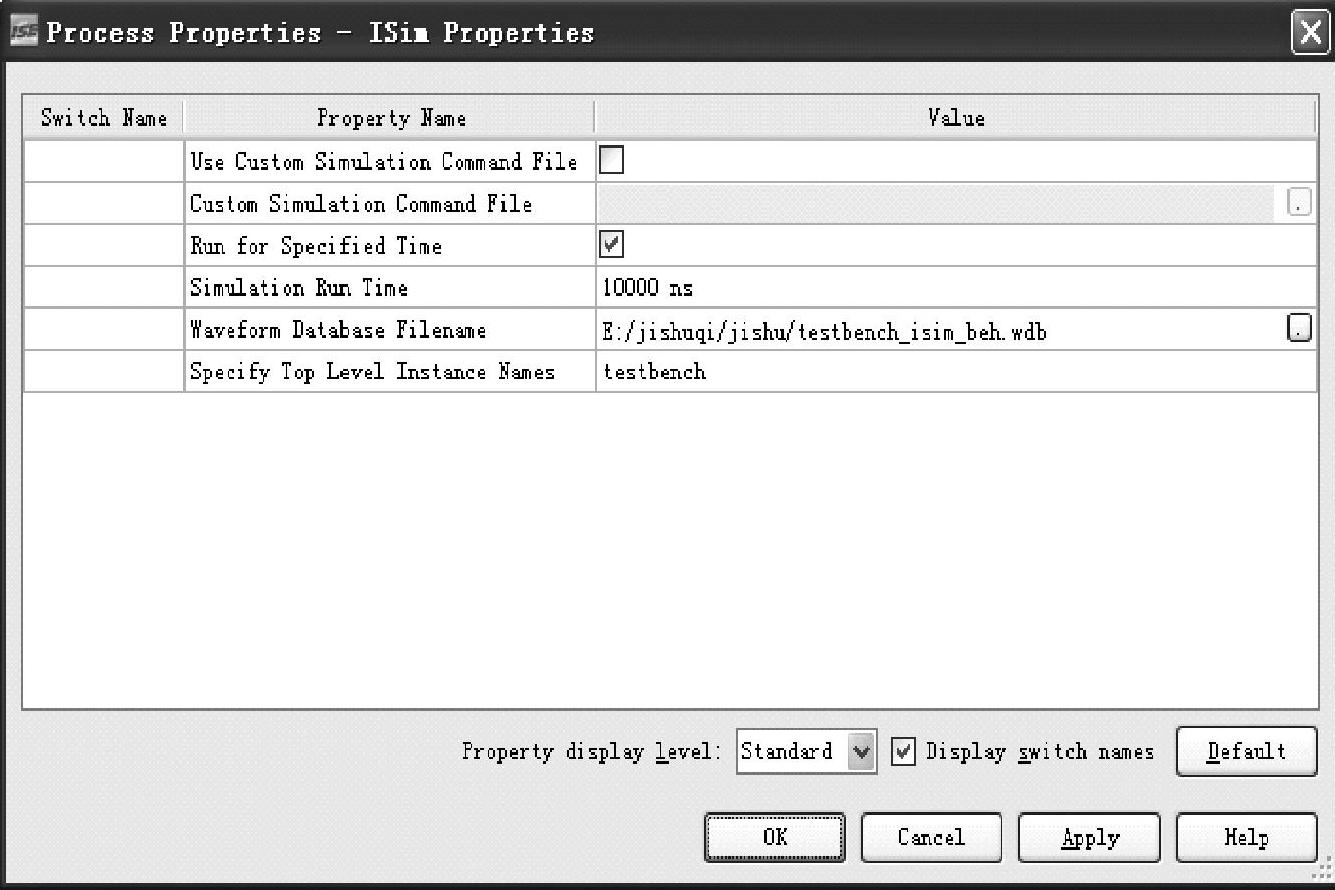

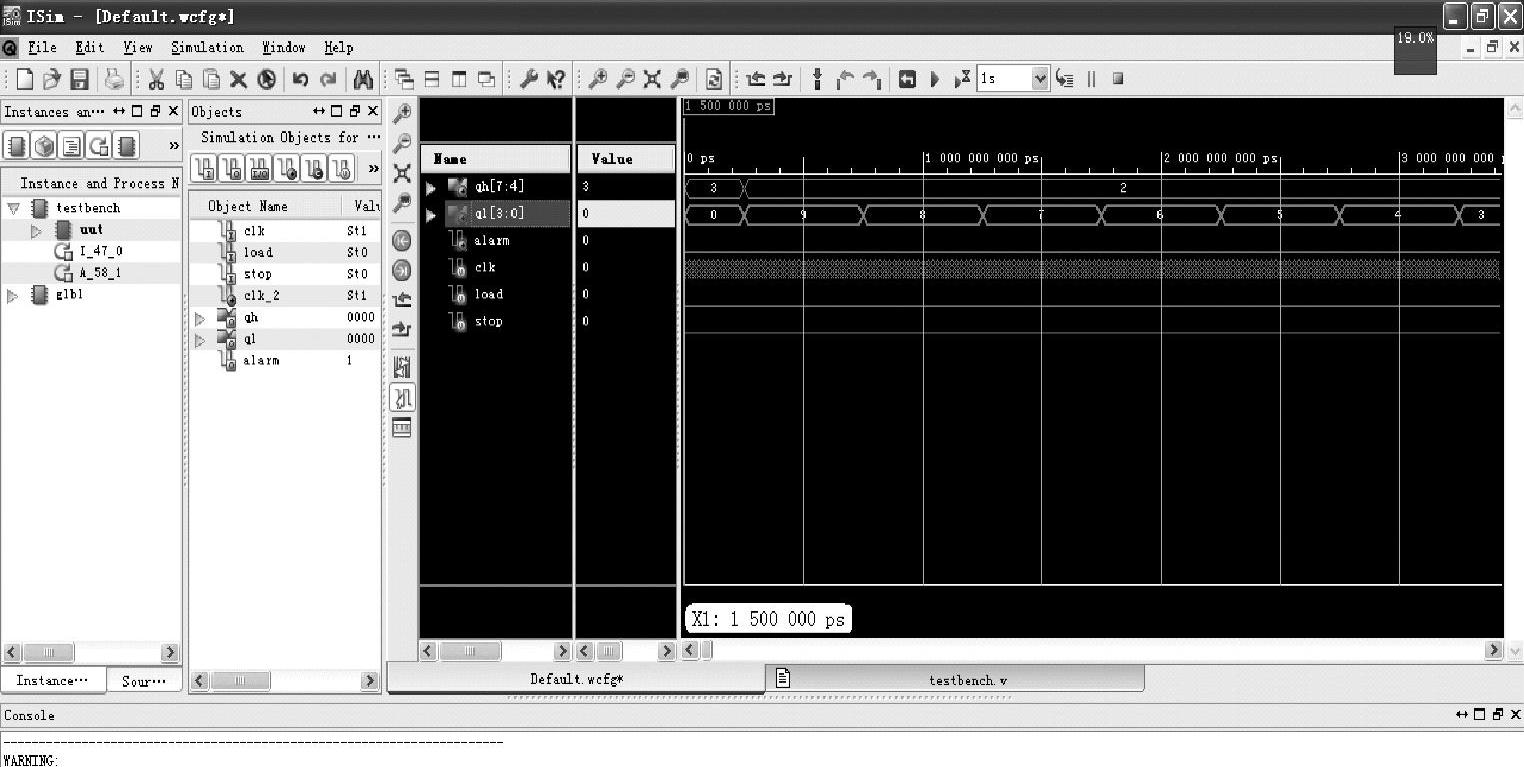

(2)在sources窗口的sourcesfor中选择Behavioral Simulation。用鼠标右键单击Simulate Behavioral Model设置Simulation Run Time,如图5-94所示;然后双击Simulate Behavioral Model得到仿真波形,如图5-95所示。

由图5-95可以看出,此程序实现了所要设计的计时器功能。

3.添加引脚约束

(1)对生成的工程进行综合。

图5-94 操作示意图1

图5-95 仿真波形

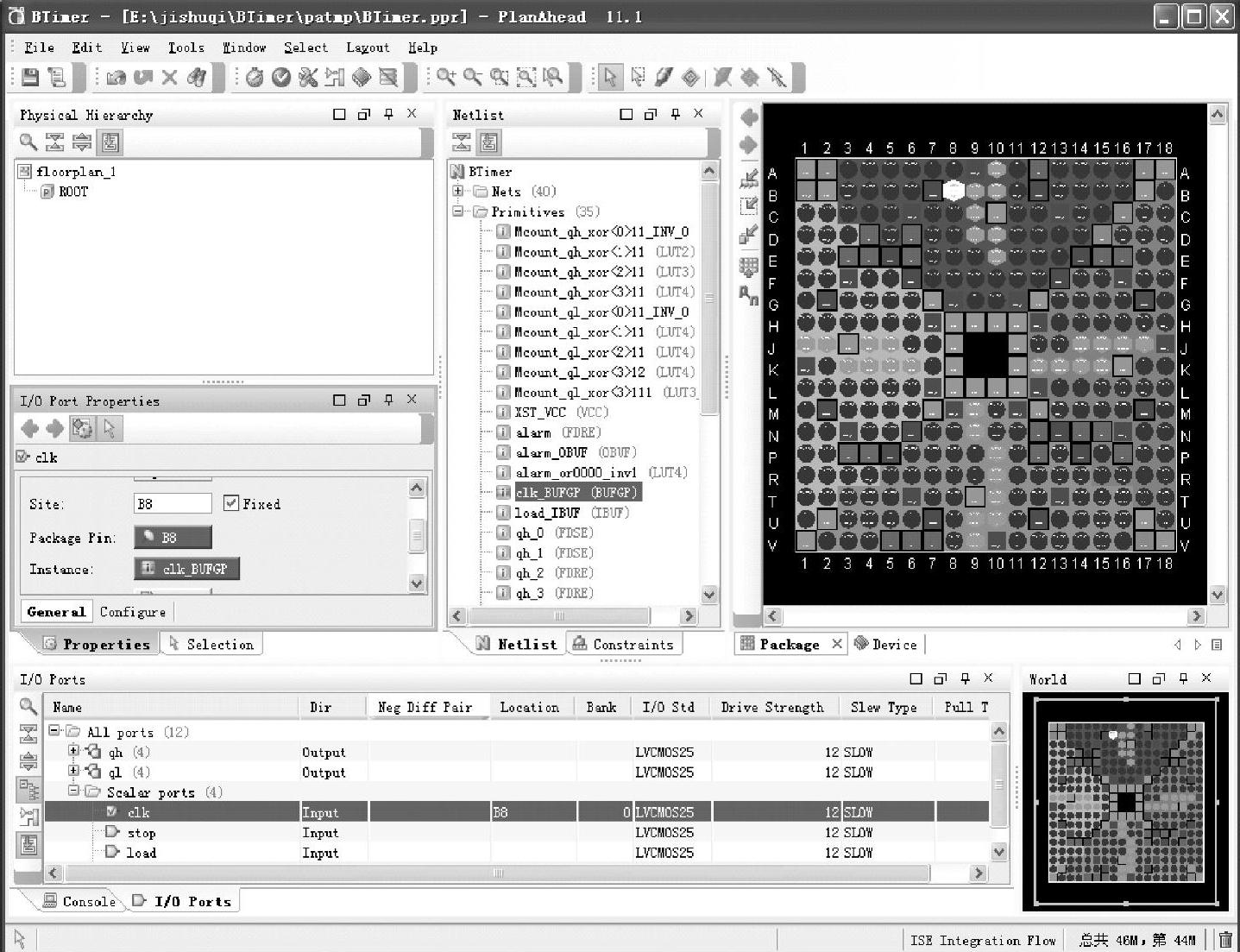

(2)添加引脚约束,如图5-96所示。

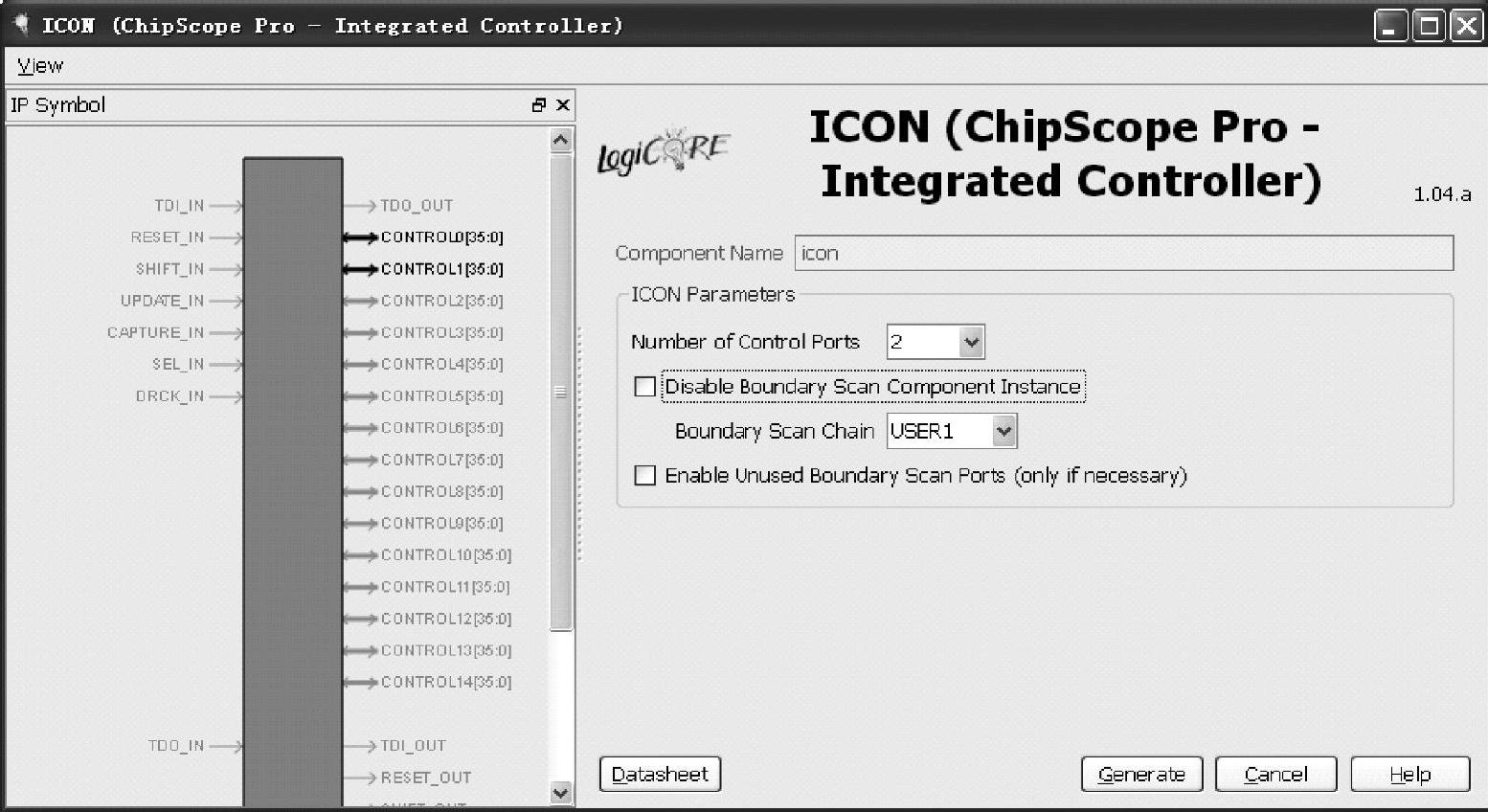

4.进行ChipScope在线调试

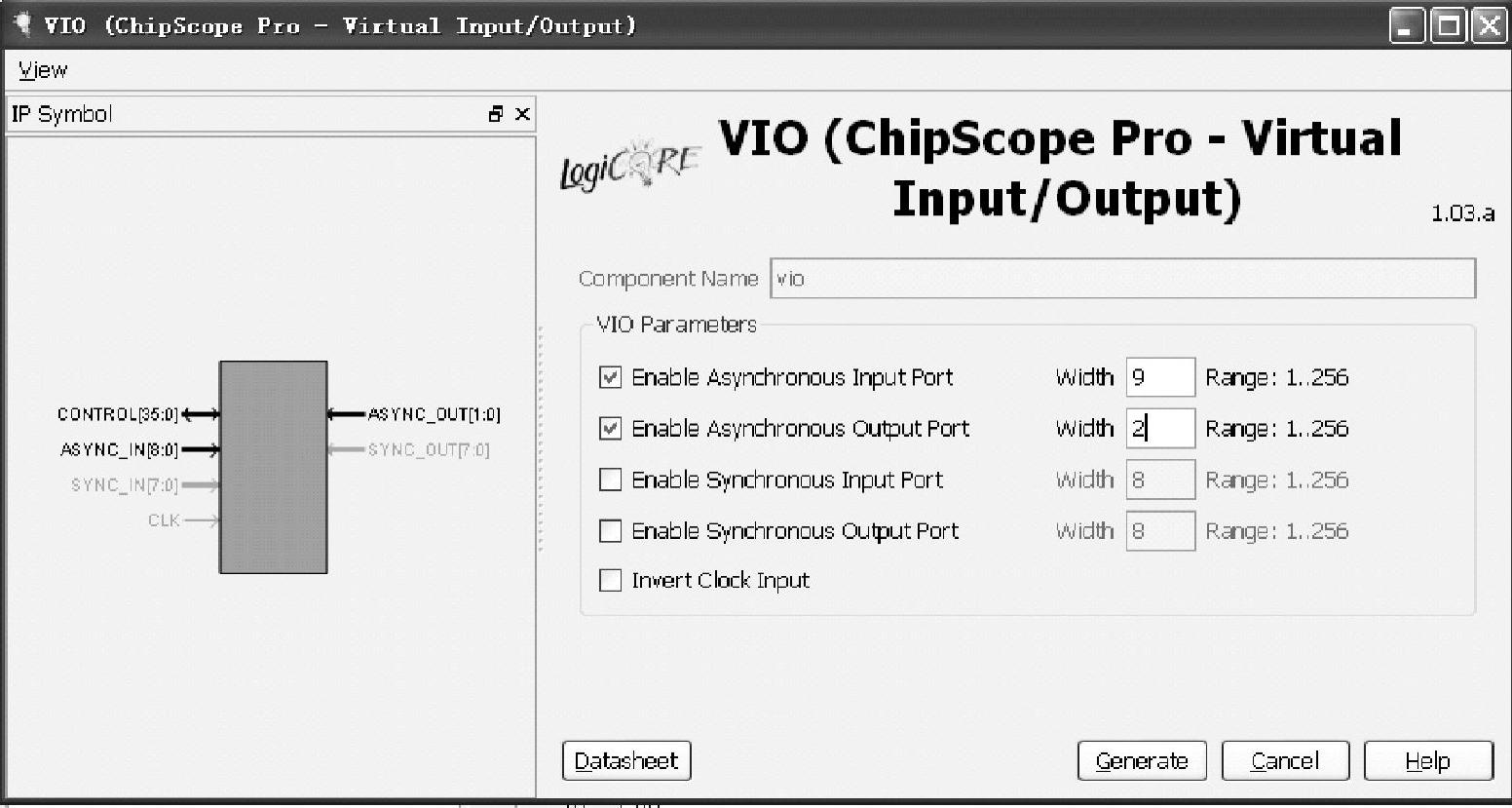

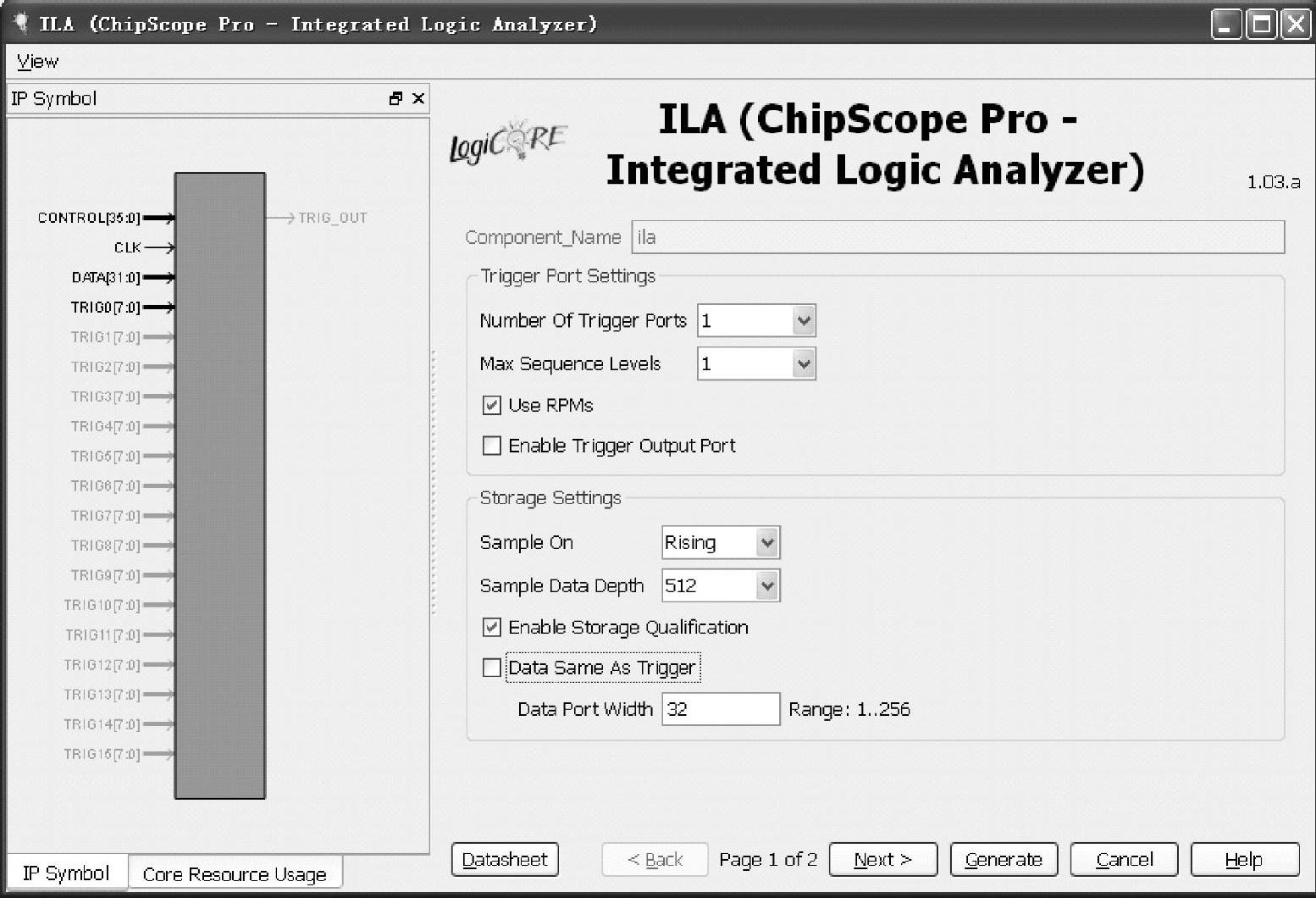

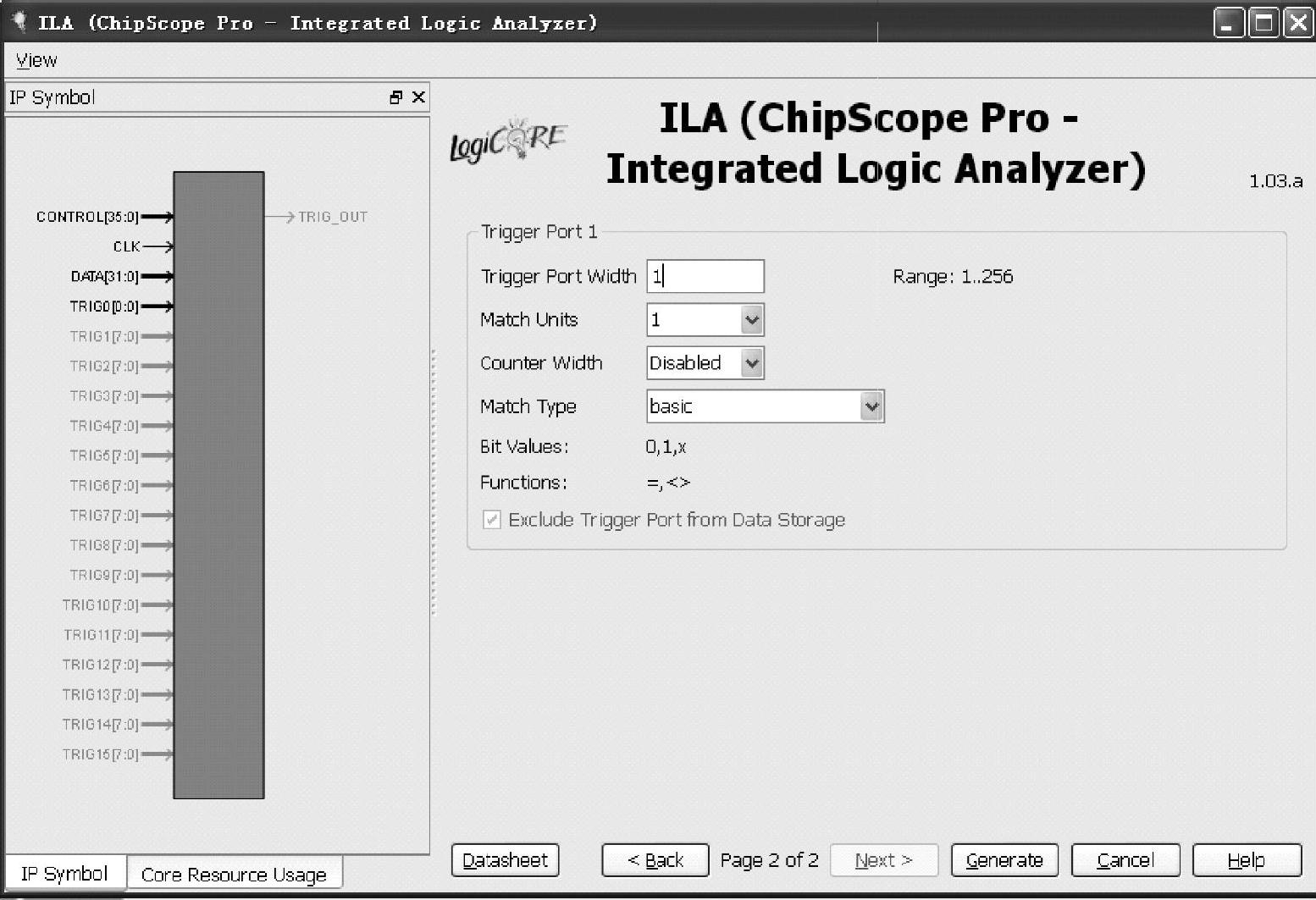

(1)生成ICON核和VIO核并添加到工程 这里使用的是核生成法,因为ICON核需要控制VIO核和ILA核,所以控制端口数为2,如图5-97所示。VIO核使用异步I/O端口,异步输入位宽为2,异步输出位宽为9,如图5-98所示。ILA核的设置如图5-99和图5-100所示。

图5-96 时钟引脚约束

图5-97 操作示意图1

图5-98 操作示意图2(https://www.xing528.com)

图5-99 操作示意图3

图5-100 操作示意图4

在进行板调的时候,为了能够看得更直观,需要将分频再次扩大,即进行250万次分频。最后得到的代码详见光盘附件5-24。

(2)在ISE里进行综合和实现,然后生成bit文件。

(3)在ChipScope里观测调试。

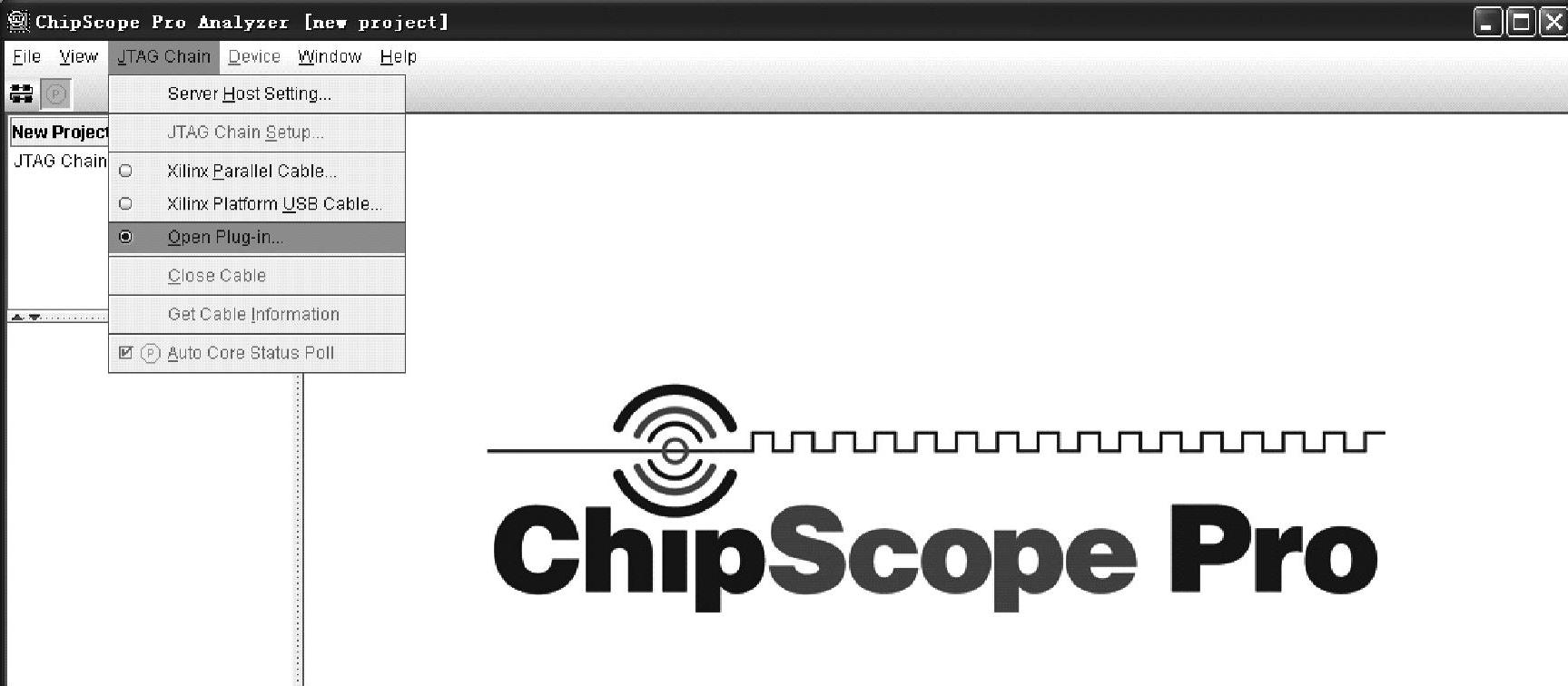

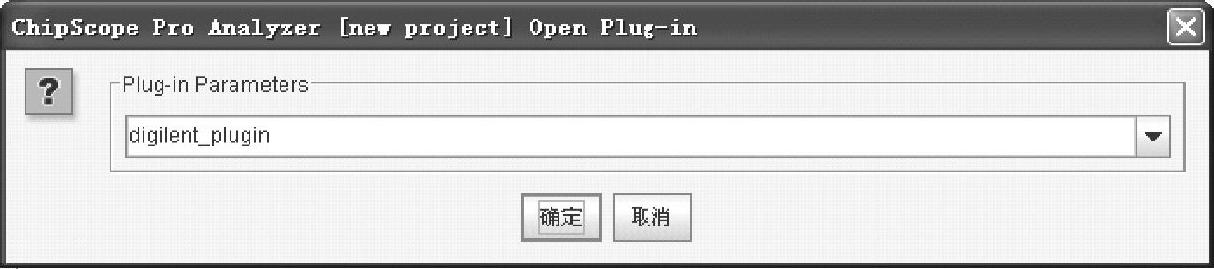

在Processes窗口中选择双击Analyze Design Using Chipscope进入Chip ScopePro Analyzer窗口,单击JTAG Chain在弹出的窗口中单击Open Piug in,如图5-101所示。

图5-101 操作示意图1

然后在弹出的对话框中单击“确定”按钮,如图5-102所示。

图5-102 操作示意图2

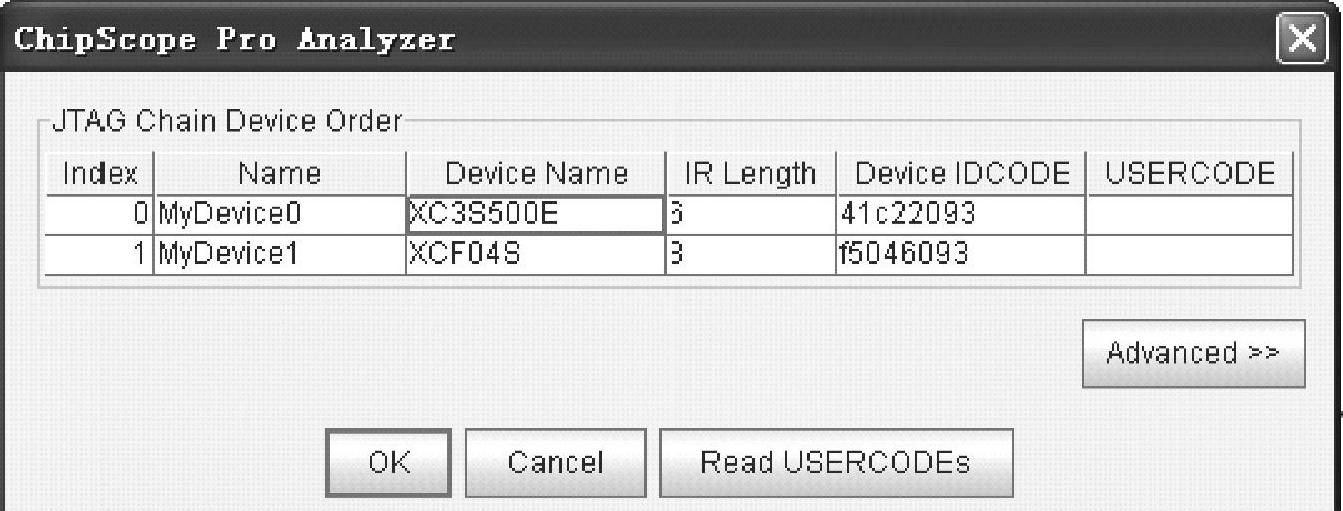

然后选择XC3S500E单击“OK”按钮,如图5-103所示。

图5-103 操作示意图3

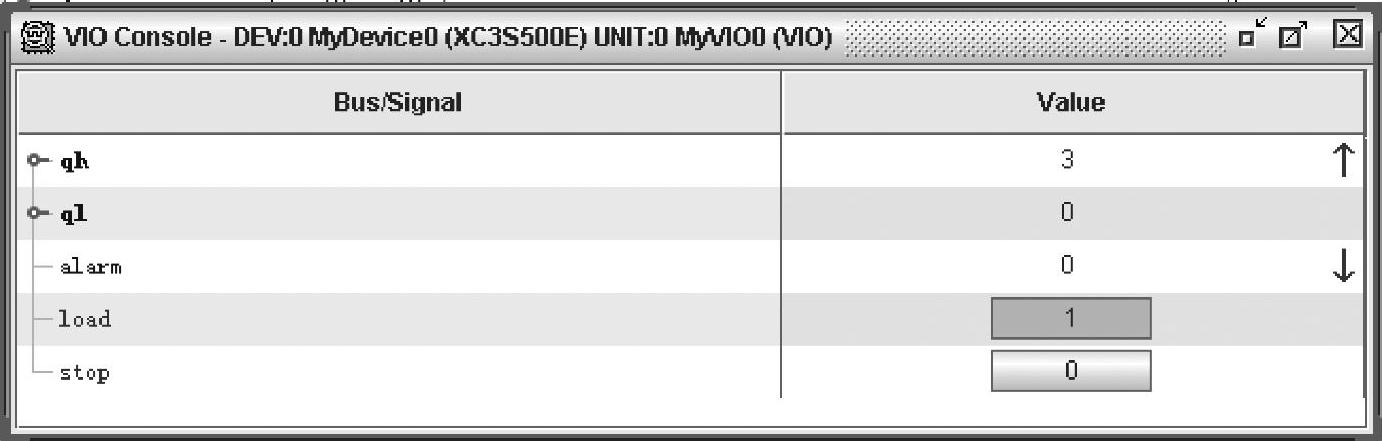

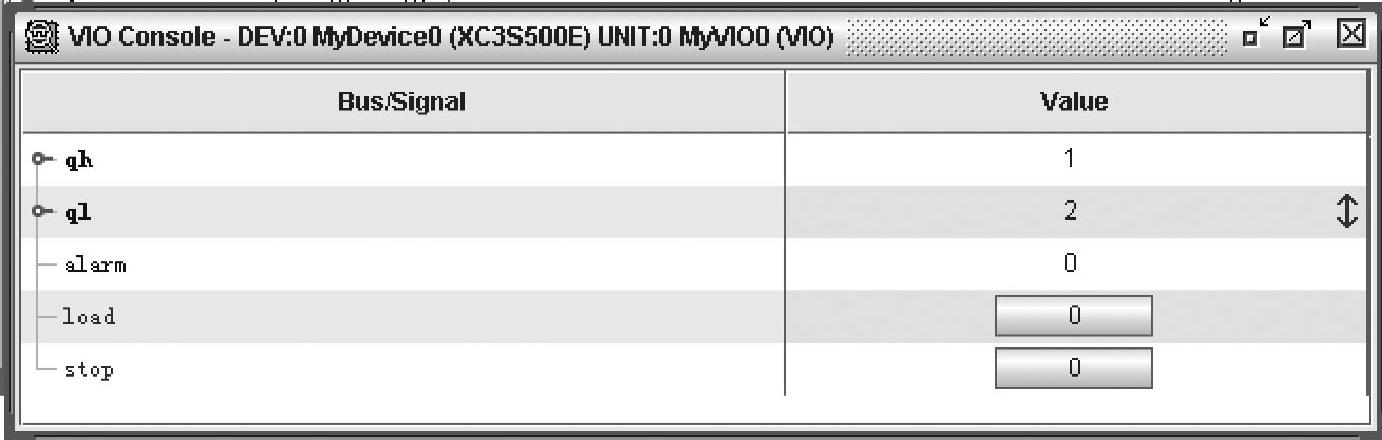

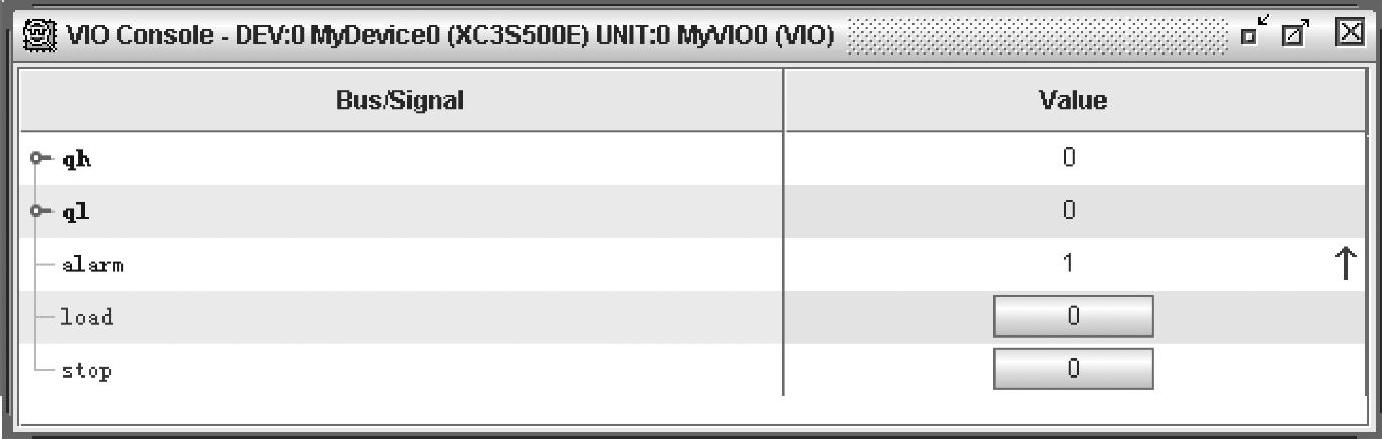

最后得到的结果如图5-104~图5-106所示。

图5-104 load=1,置数30s

图5-105 load=0,stop给一个高脉冲,开始减计时

图5-106 30s计时结束,alarm=1,报警

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。