由5.5.1节分析可知,基于FPGA的数字电压表包括四个模块,分别为分频模块、A-D转换控制模块、数据处理模块、七段数码管扫描显示模块。下面对四个模块分别进行设计。

1.分频模块

在分频模块代码设计中,CLK是时钟输入端,OUT0、OUT1是两组分频输出端,也可根据实际需要设计多组分频输出端。在源程序中定义了L0、L1两个参数和它们对应的位宽,这样可以灵活的设置不同的输出频率,同时可以满足多个模块不同的频率需求。例如,七段数码管扫描显示模块需要1kHz的频率,因为Spartan 3E开发板内部提供了一个50MHz的频率,所以可以令L1=24999来得到1kHz的频率。

分频模块的设计代码详见光盘附件5-16。

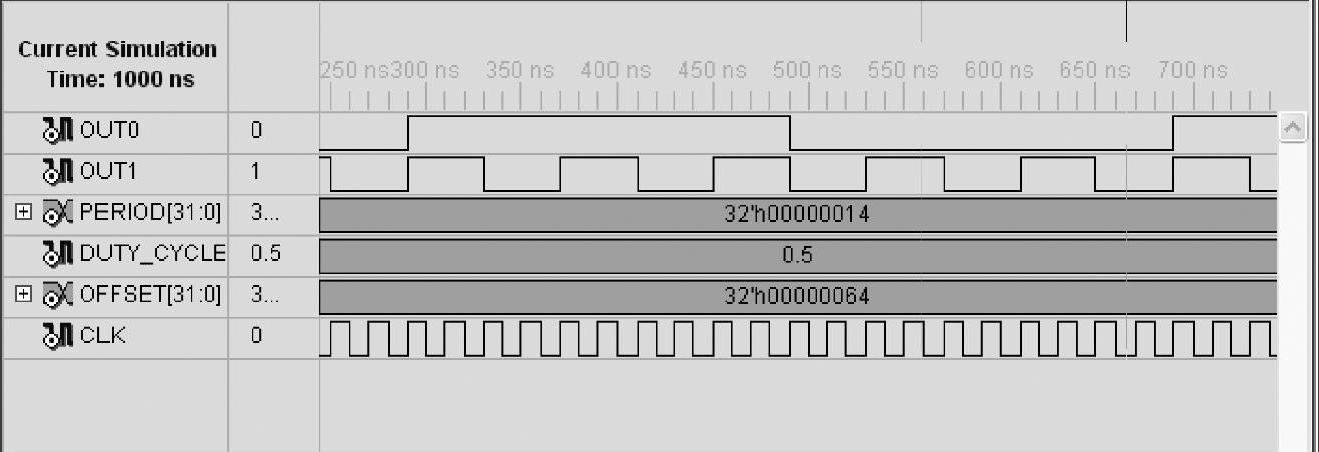

分频模块的仿真结果如图5-82所示,OUT0、OUT1输出分别是10分频和4分频,与设置的参数相符。

图5-82 分频仿真图

2.A-D转换控制模块

用状态机对ADC0809进行采样控制时首先必须了解其工作时序,然后据此作出状态图,最后再写出相应的VerilogHDL代码。

A-D转换控制模块完成ADC0809的初始化、A-D转换的启动、地址锁存、通道选择、状态读取及数据读取、数据锁存等功能。ADC0809的特性及工作时序如下:

(1)ADC0809工作特性:

①8路输入通道,8位ADC,即分辨率为8位。

②具有转换起/停控制端。

③转换时间为100μs。

④单个5V电源供电。

⑤模拟输入电压范围0~5V,不需零点和满刻度校准。

⑥工作温度范围为-40~85℃。

⑦低功耗,约15mW。

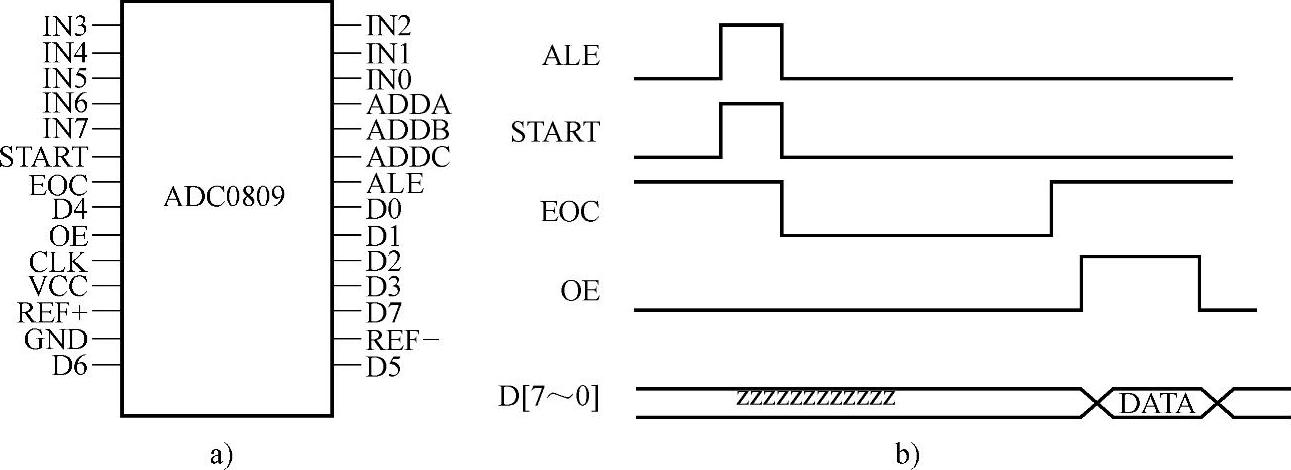

(2)ADC0809引脚图和工作时序如图5-83所示。

图5-83 ADC0809引脚图及工作时序

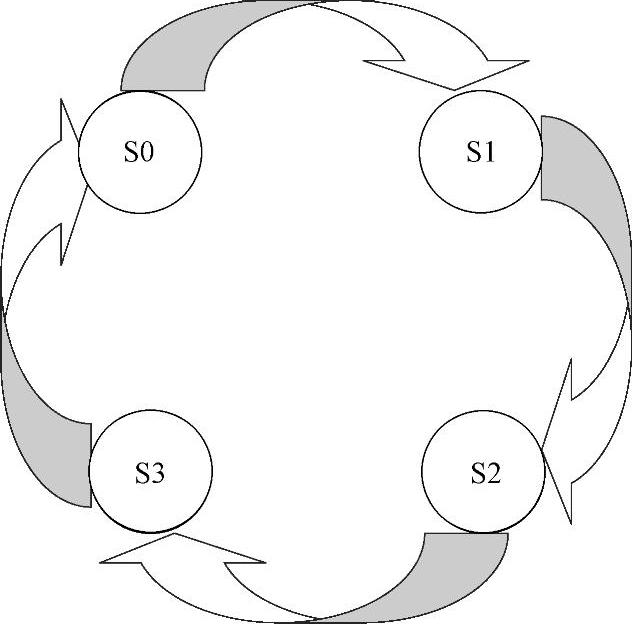

模块的工作时序:上电瞬间FPGA初始化,ADDA置成0,状态机处于第一个状态;第一个上升沿到来时,ALE、OE、START均置0,初始化ADC0809,状态机由状态一转换到状态二;第二个上升沿到来时,ALE、START置1,OE为0,此时地址锁存信号有效,由ALE将ADDA的0状态锁存到地址锁存器并译码,选择IN0作为模拟信号输入端,同时START信号有效,启动采样,状态机由状态转换到状态三;第三个上升沿到来时,ALE、START返回到低电平,OE继续为低电平,此时如果FPGA检测到ADC0809的EOC引脚由低电平变成高电平(A-D转换完成),转换到状态四,否则继续保持在状态三,直到转换完成。由状态三转换到状态四后,当时钟上升沿到来时,OE置高电平,允许转换数据输出,其余信号状态保持不变。时钟上升沿再次到来时,状态机返回到状态一,控制器在时钟信号控制下完成状态转换,实现对ADC0809的控制。控制采样状态图如图5-84所示。

该模块的设计程序要对四个状态进行控制,第一个状态是对ADC0809进行初始化;第二个状态是ADC0809进行转换动作;第三个状态是等到ADC0809转换完成以后允许输出状态;第四个状态是由控制器读取数据总线上的数字转换信号。可以根据读取时间的长短,决定是否要增加一个状态以延长读取时间。

A-D转换控制模块程序详见光盘附件5-17。

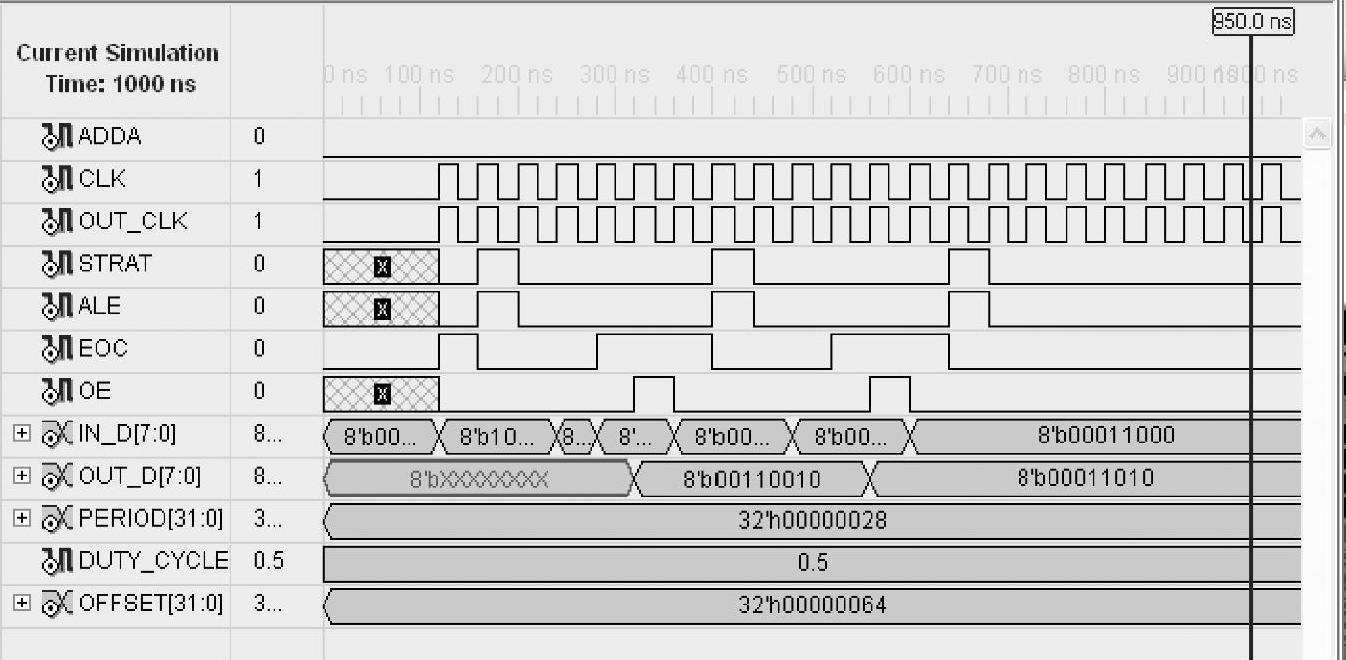

A-D转换控制模块的仿真结果如图5-85所示。

(https://www.xing528.com)

(https://www.xing528.com)

图5-84 控制采样状态图

图5-85 A-D转换控制模块仿真图

由图5-85所示的仿真结果可以看到,STRAT、ALE、EOC、OE输出时序与ADC0809的工作时序相符,仿真结果正确,图中EOC是根据ADC0809工作特点手动输入的一个信号,不会影响仿真与调试的结果。

3.数据处理模块

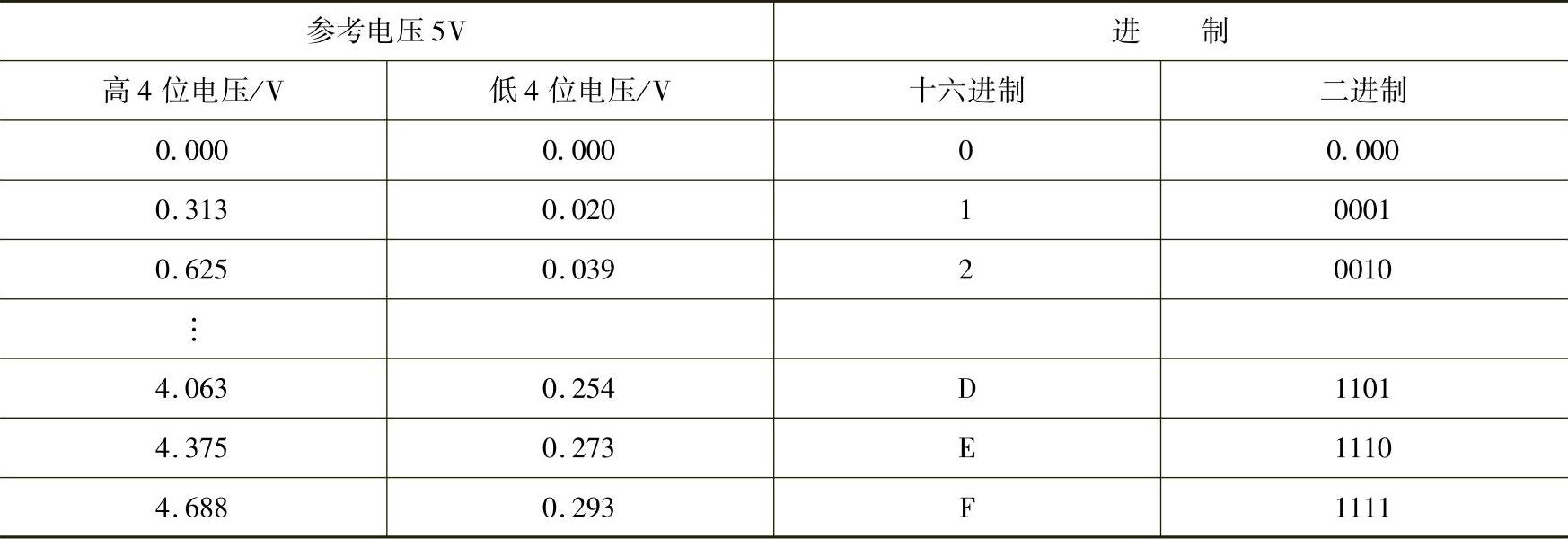

数据处理模块的设计采用5V参考电压,测量范围为0~5V。由于ADC为8位,所以电压的最小分辨率为0.02V,待转换数据与实际电压值的对应关系如表5-8所示。

表5-8 待转换数据与实际电压值的对应表

根据表5-8的对应关系可编制一个查表程序,用查表指令计算出高、低4位的两个电压值,并分别用16位BCD码表示;再设计16位BCD码加法,如果每4位相加的结果超过9则需要进行进位和加6调整,从而可得到待处理数据的BCD码。

例如,从ADC0809上取得的数据为“00010100”,0001对应的电压值为0.313V,其对应的BCD编码为“0000001100010011”;0100对应的电压值为0.078V,其对应的BCD编码为“0000000001111000”。0~3位相加为1011,大于9,加6将其调整为BCD码,其值为0010,并且向前有一进位。4~7位相加的结果为1000,由于低位有进位,因此最终结果为1001。同理可得8~11位的结果为0011,12~15位的结果为0000。4位合计的值为0.391V,与0.313+0.078的结果相符。其他计算依此类推。

数据处理模块的设计代码详见光盘附件5-18。

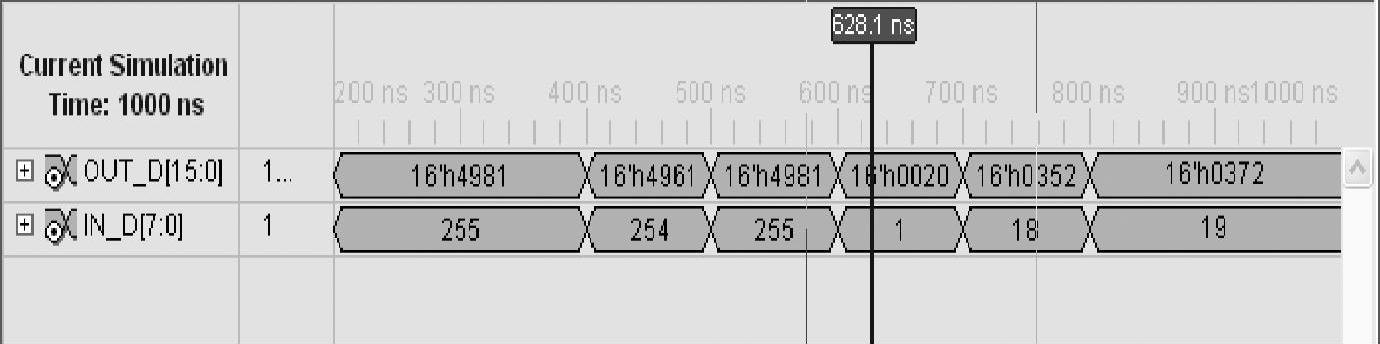

仿真结果如图5-86所示。

图5-86 数据处理仿真图

从图5-86所示的仿真结果可以看到,当输入“00010100”时,BCD码输出0391,实现了加法过程中的进位,同时与查表程序设置的数据相符,仿真结果正确。

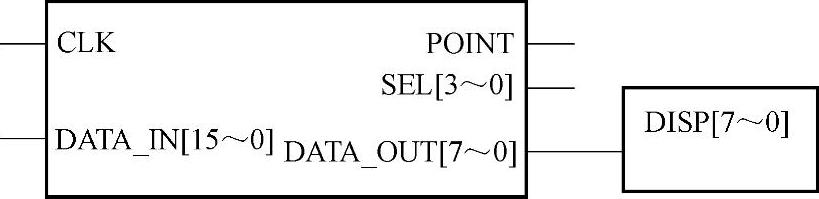

图5-87 扫描显示模块

4.七段数码管扫描显示模块

扫描显示模块如图5-87所示,图中CLK是扫描时钟,其频率应大于100Hz,否则会有闪烁现象;模块频率为1kHz,由开发板内部给定的50MHz时钟分频得到;DATA_IN是数据处理模块输出电压值的BCD码;SEL是数码管的片选信号;POINT是数码管小数点驱动信号;通过扫描分别从DATAOUT输出4位电压值的BCD码,并通过DISP将BCD码译成相应的七段数码管驱动值,送数码管显示。

七段数码管扫描显示模块的设计代码详见光盘附件5-19。

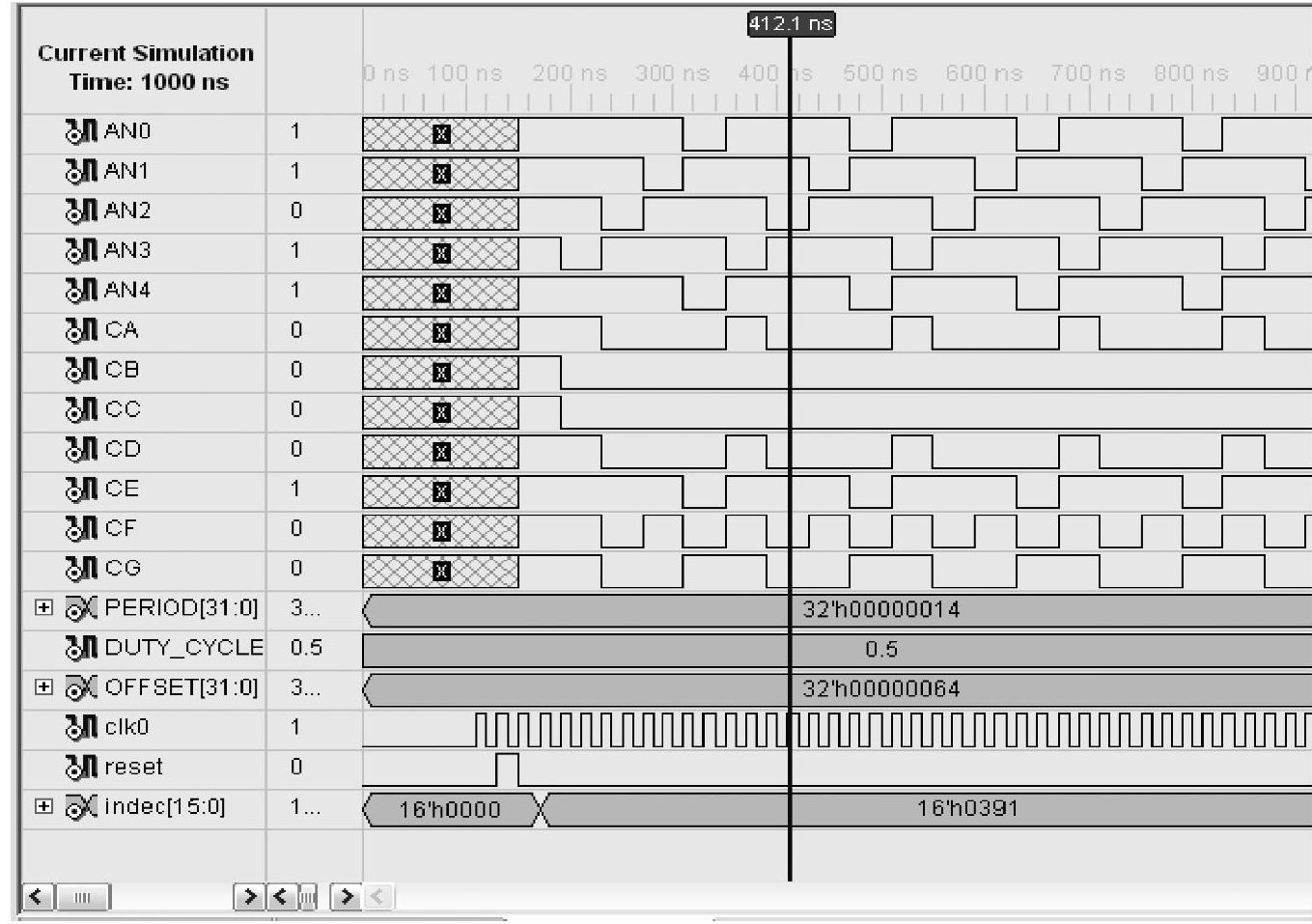

为了更清晰地观察仿真波形,可在仿真时将频率调低,仿真结果如图5-88所示。

图5-88 扫描显示仿真图

从图5-88所示的仿真波形可以看出,在复位前,输出数据都是乱码。在复位结束后,所有输出都置高电平,这与程序相符。当hclk跳变为高电平时,首选译码显示最低位1,这里是低电平有效,即只有CB、CC为低电平,同时选择第四个数码显示管即AN3为低电平。下一个时钟信号到来时,显示9,直至显示最高位0,此时表示小数点的AN4为低电平,这样一个扫描循环即完成。如果没有新数据来驱动,它将一直这样循环下去,可见仿真结果正确。

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。