5.4.2.1 一般演奏电路实现步骤

1.设计输入

使用Xilinx Virtex Ⅱ-Pro调试,仿真软件ISE11.1。

(1)创建工程 在创建工程的时候,注意器件族类型、器件型号、综合工具和仿真器的选择,在这里选择的器件族类型(Device Family)是Virtex2P,器件型号(Device)是XC2VP30 ff896-7,综合工具(Synthesis Tool)是XST(VHDL/Verilog),仿真器(Simulator)是ISES imulator(VHDL/Verilog)。

(2)输入代码 VerilogHDL代码详见光盘附件5-11。

2.功能仿真

(1)在sources窗口的sources for中选择Behavioral Simulation。

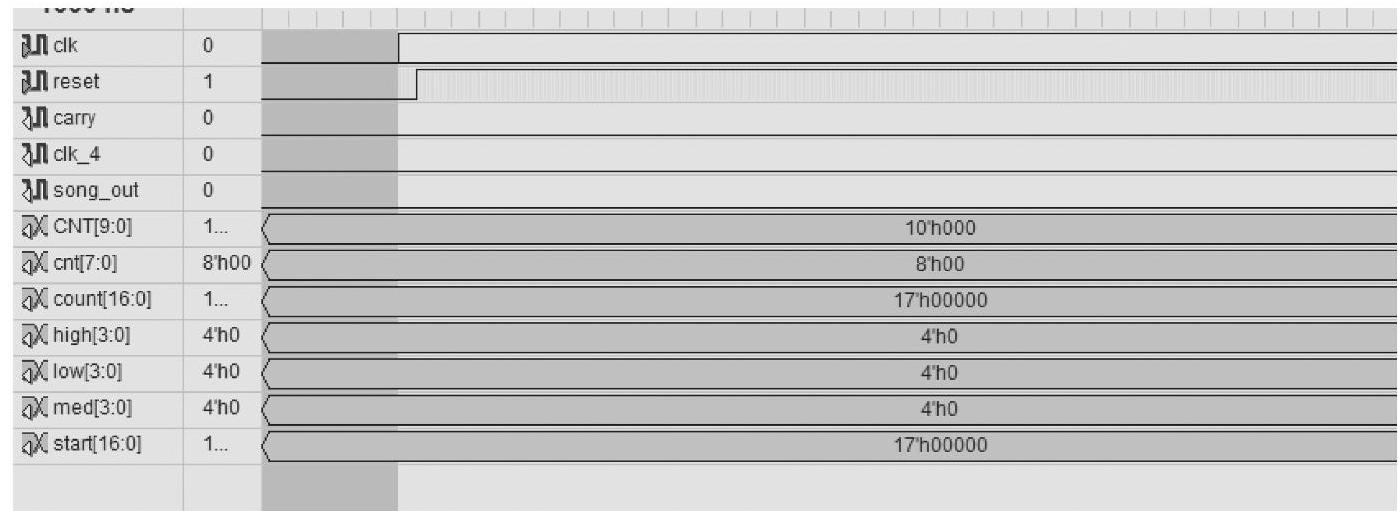

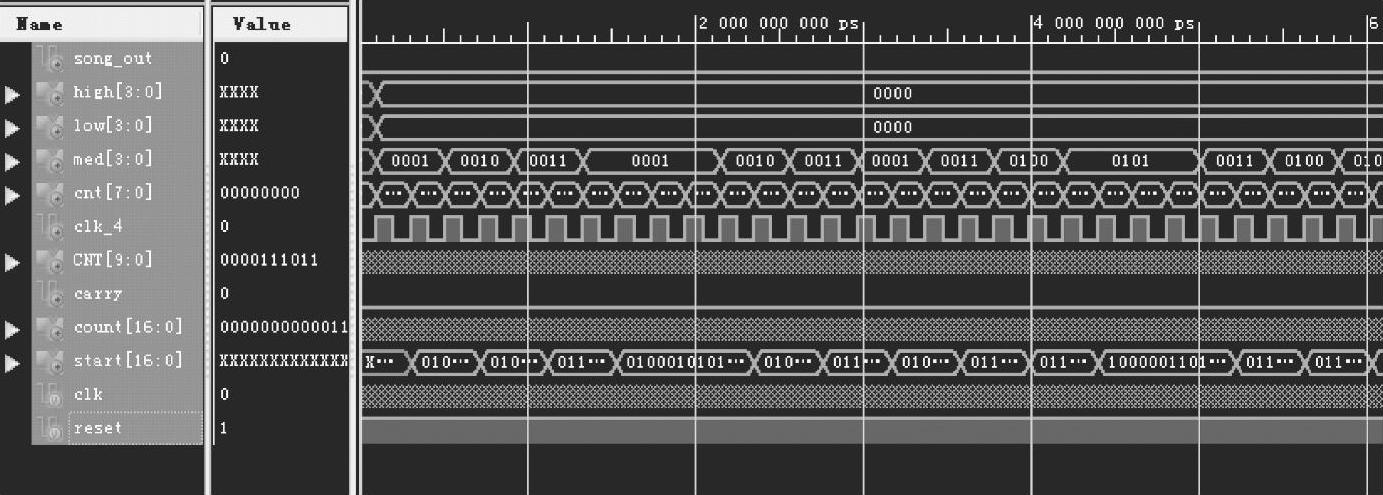

(2)由Test Bench WaveForm添加激励源,如图5-67所示。

图5-67 时钟和clk输入

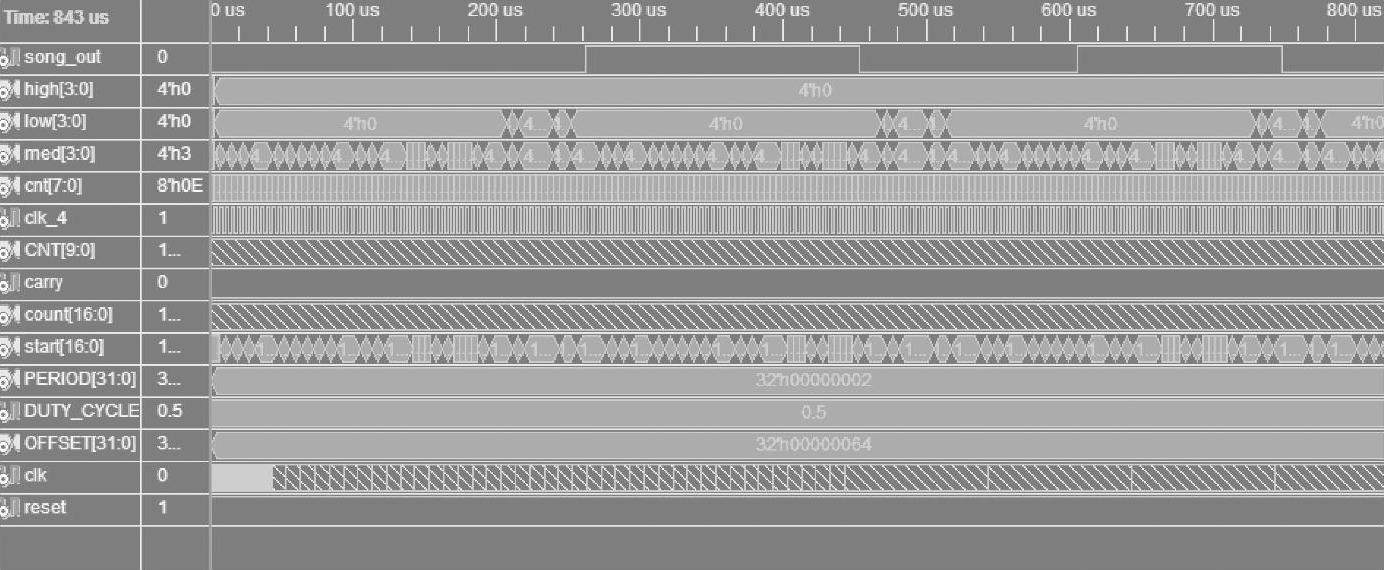

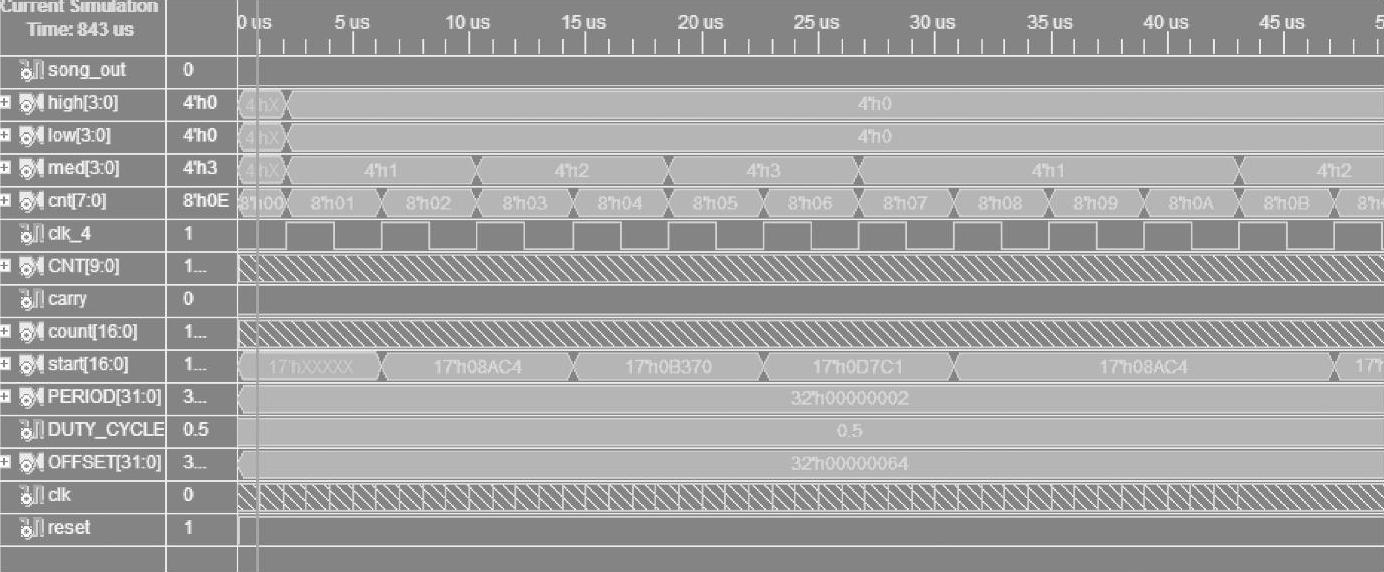

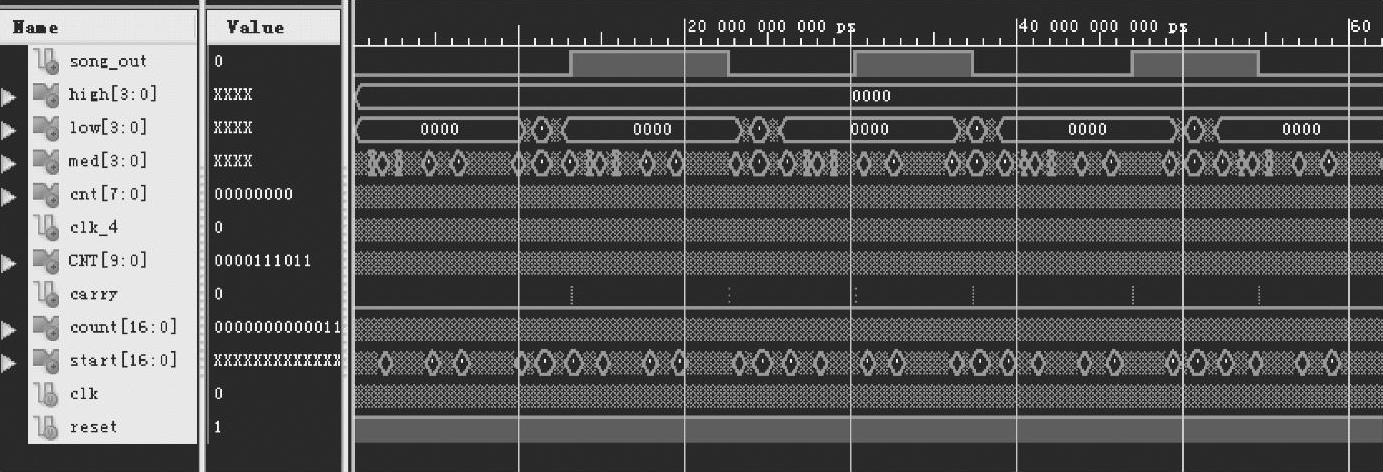

仿真结果如图5-68、图5-69所示。

图5-68 观察song_out输出

图5-69 观察高、中、低音的输出

由图5-68、图5-69可以看出,当reset=0时,乐曲演奏电路输出song_out,high,med,low清零;当reset=1时,song_out,high,med,low开始正确的输出。

在进行功能仿真验证之后,再进行综合。

3.在线调试

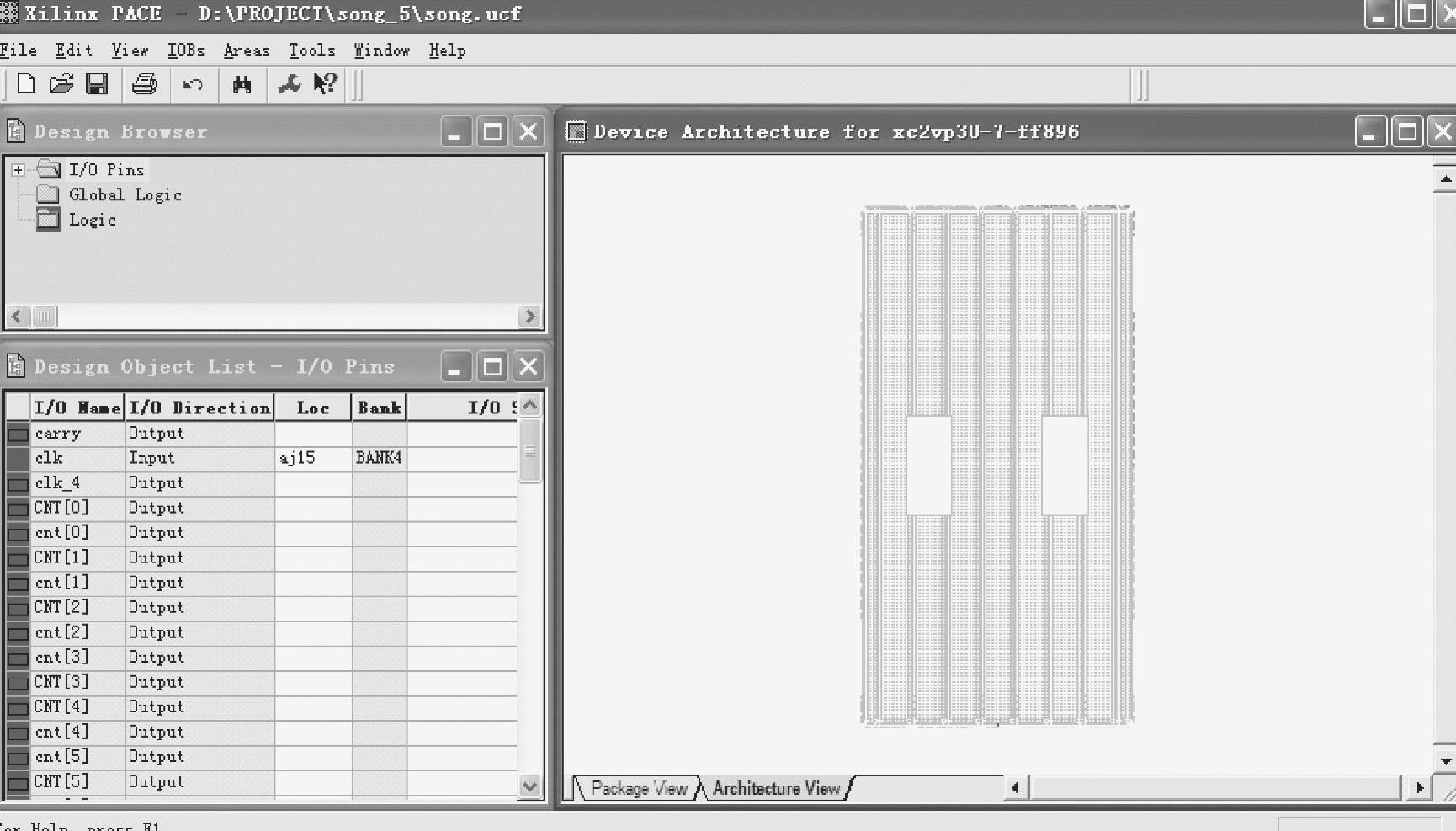

(1)添加引脚约束,如图5-70所示。

图5-70 添加引脚约束

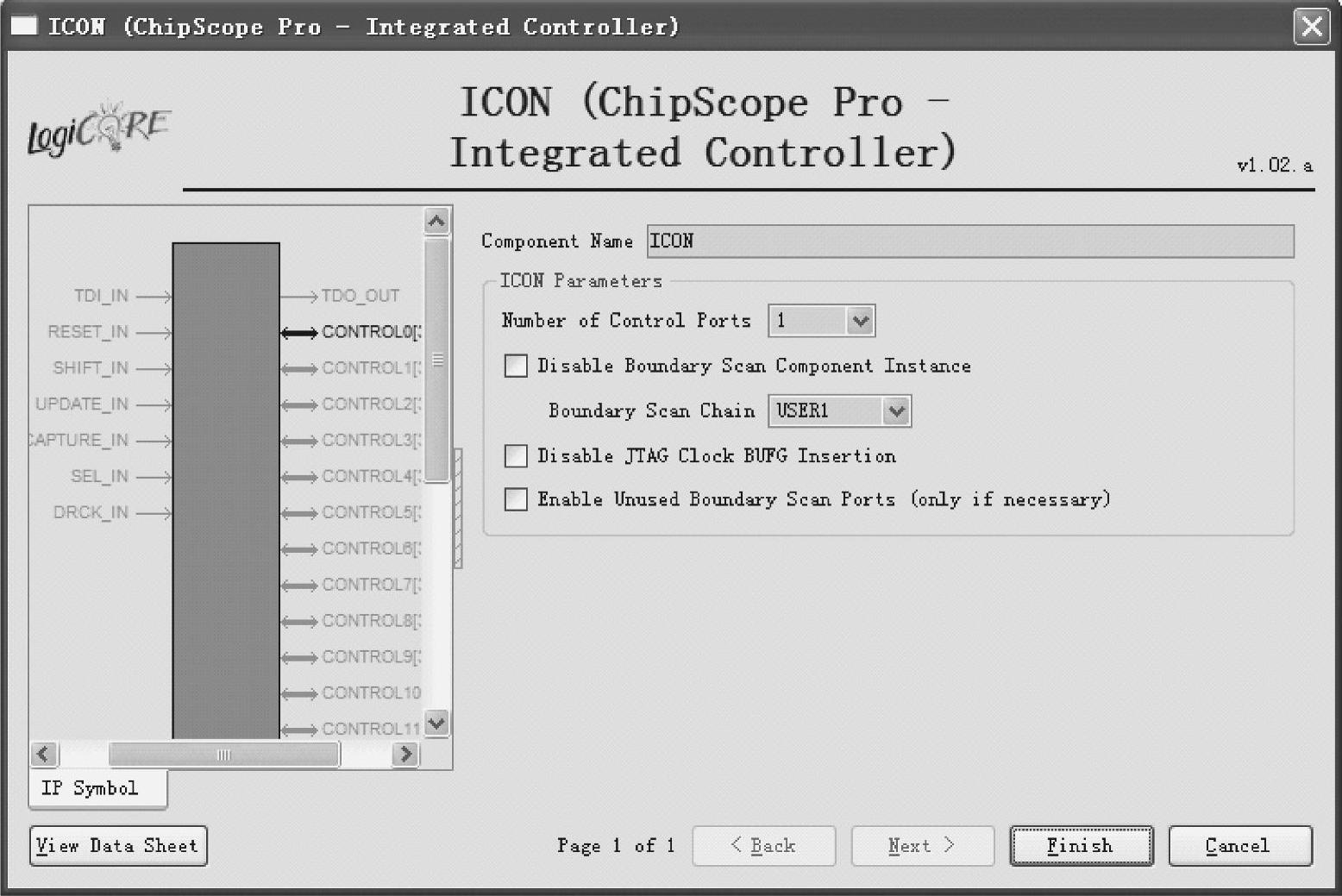

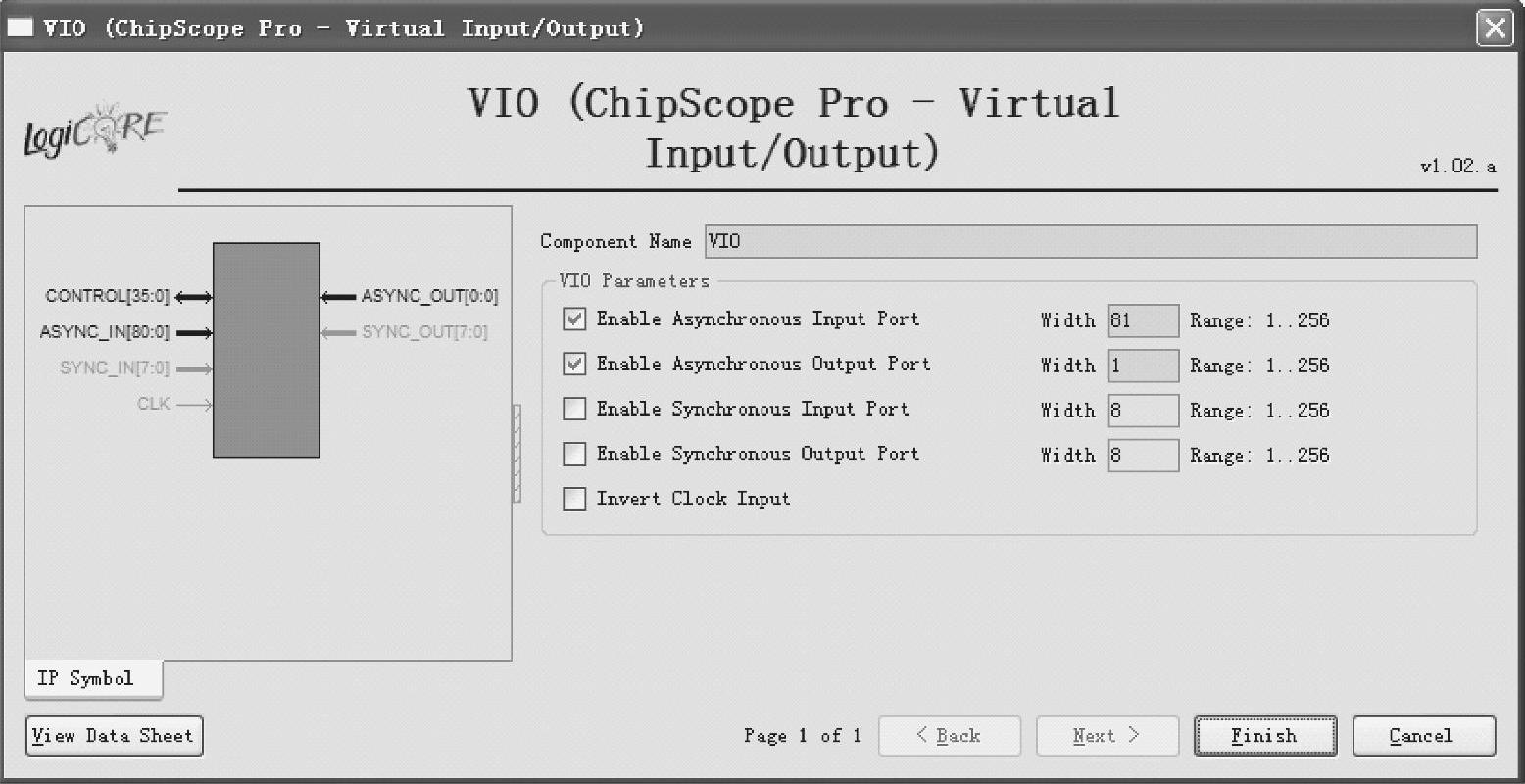

(2)生成ChipScope核并添加到工程 这里使用的是核生成法。由于只需要使用VIO核来观察结果,ICON核只需要控制VIO一个核,所以控制端口数为1,如图5-71、图5-72所示。

图5-71 添加ICON核

图5-72 添加VIO核

最后得到的代码详见光盘附件5-12。

(3)在ISE里进行综合和实现,然后生成bit文件。

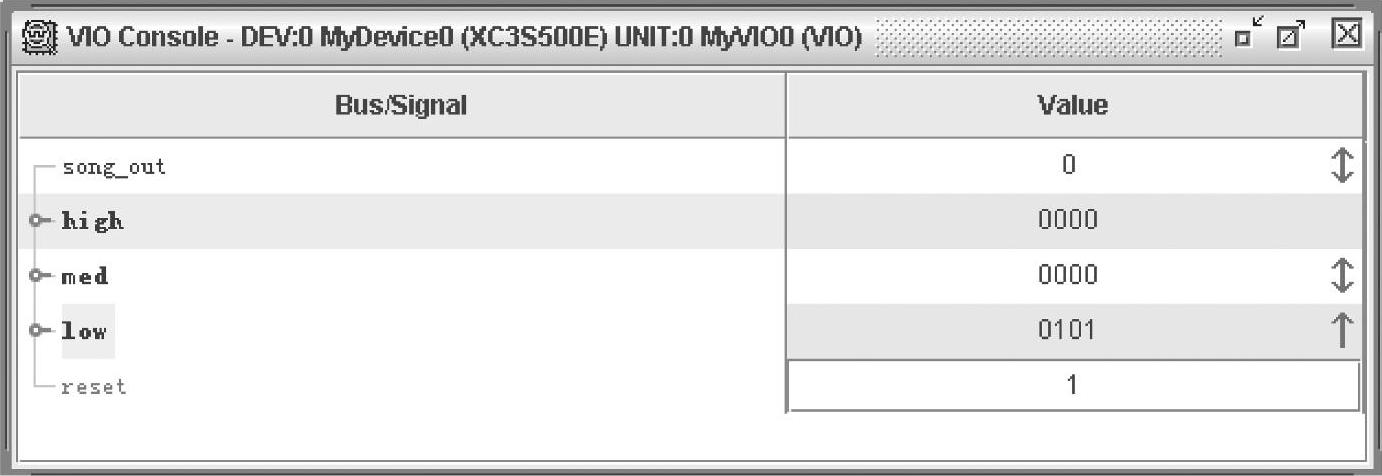

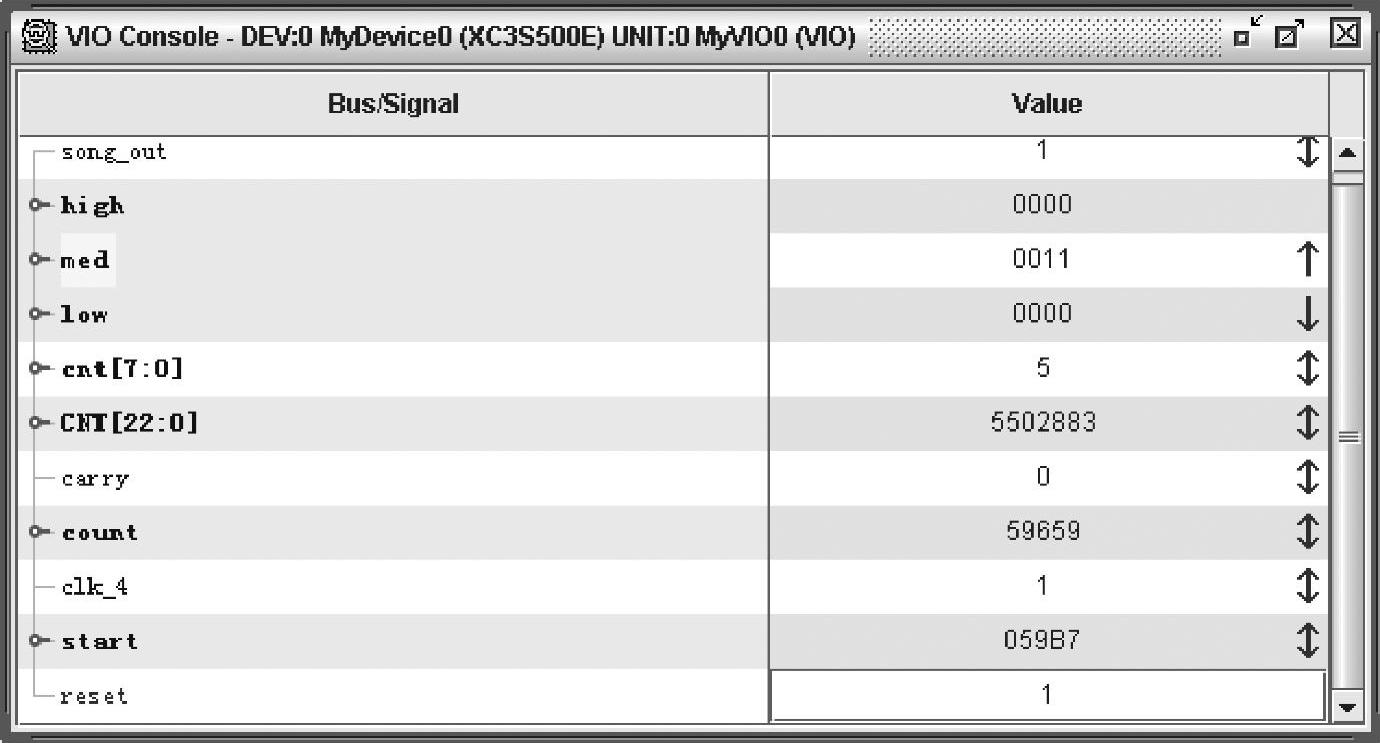

(4)在ChipScope里观测调试 在Processes窗口中选择双击Analyze Design Using Chips-cope进入ChipScope Pro Analyzer窗口,单击 图标检查连接情况,然后下载bit文件进行在线观测。调试结果如图5-73所示。

图标检查连接情况,然后下载bit文件进行在线观测。调试结果如图5-73所示。

图5-73 在线调试

5.4.2.2 加分频器

1.设计思路

使用Spartan-3E调试,仿真软件ISE11.1。由于Spartan-3E的时钟频率为50MHz,采用上述同样的方法可以求出《两只老虎》片段中各音名的分频系数,如表5-7所示。

为了产生4Hz的脉冲,可以把50MHz的时钟进行6250000分频(用计数器CNT统计分频次数),变为8Hz(周期为0.125s),然后,使4Hz信号每0.125s取反一次,则变为4Hz的信号(周期为0.25s)。(https://www.xing528.com)

从表5-7可以看出,最大的分频系数为63776,故采用16位二进制计数器(count)分频可满足需要(最大计数216-1=65535)。在表5-7中,除给出了分频比以外,还给出了对应于各个音阶频率计数器不同的预置数。预置数等于65535减去相应的分频系数,对于不同的分频系数,只要加载不同的预置数即可。此外,对于乐曲中的休止符,可将分频系数设为0,即加载预置数65535,此时,蜂鸣器不会发声。

表5-7 《两只老虎》片段中各音名的频率、分频系数和预置数

2.设计步骤

(1)创建工程 在创建工程的时候,注意器件族类型、器件型号、综合工具和仿真器的选择,这里选择的器件族类型(Device Family)是Spartan 3E,器件型号(Device)是XC3S500E FG320-4,综合工具(Synthesis Tool)是XST(VHDL/Verilog),仿真器(Simula-tor)是ISE Simulator(VHDL/Verilog)。

(2)在源代码窗口中单击鼠标右键,在弹出的快捷菜单中选择NewSource,在弹出的对话框中选择Verilog Moudle,在右端的Filename中输入源文件名BTimer,再依次单击Next-Next-Finish,然后在弹出的源代码编辑框内输入下面的源代码并保存即可。

(3)设计输入 设计代码详见光盘附件5-13。

(4)功能仿真:

①在源代码窗口中单击右键,在弹出的快捷菜单中选择NewSource,新建testbench文件,选择Verilog Test Fixture,然后单击Next-Next-Finish,在弹出的testbench模板中编辑激励信号。

编辑的激励信号代码详见光盘附件5-14。

②在sources窗口的sources for中选择Behavioral Simulation,用鼠标右键单击Simulate Behavioral Model设置Simulation Run Time,然后双击Simulate Behavioral Model,得到仿真的波形如图5-74、图5-75所示。

图5-74 仿真波形1

(5)添加引脚约束:

①对生成的工程进行综合。

图5-75 仿真波形2

②添加引脚约束,如图5-76所示。

(6)在线调试:

①生成ICON核和VIO核并添加到工程。这里使用的是核生成法。只需要ICON核控制VIO核,所以控制端口数为1。VIO核使用异步I/O端口,异步输入位宽为80,异步输出位宽为1。

最后得到的代码详见光盘附件5-15。

②在ISE里进行综合和实现,然后生成bit文件。

③在ChipScope里观测调试。

图5-76 添加引脚约束

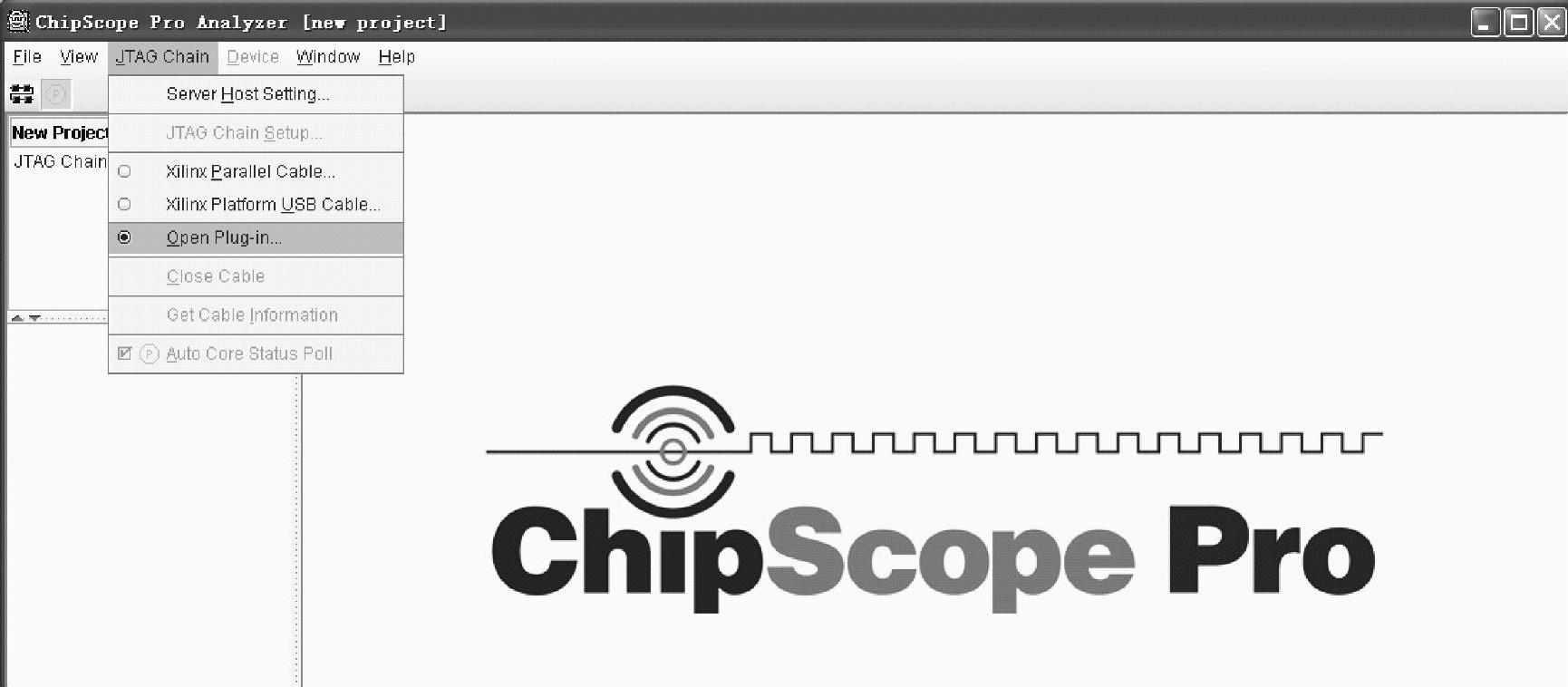

在Processes窗口中选择双击Analyze Design Using Chipscope进入ChipScope Pro Analyzer窗口,单击JTAG Chain在弹出的窗口中单击Open Piug in,如图5-77所示。

图5-77 操作示意画面1

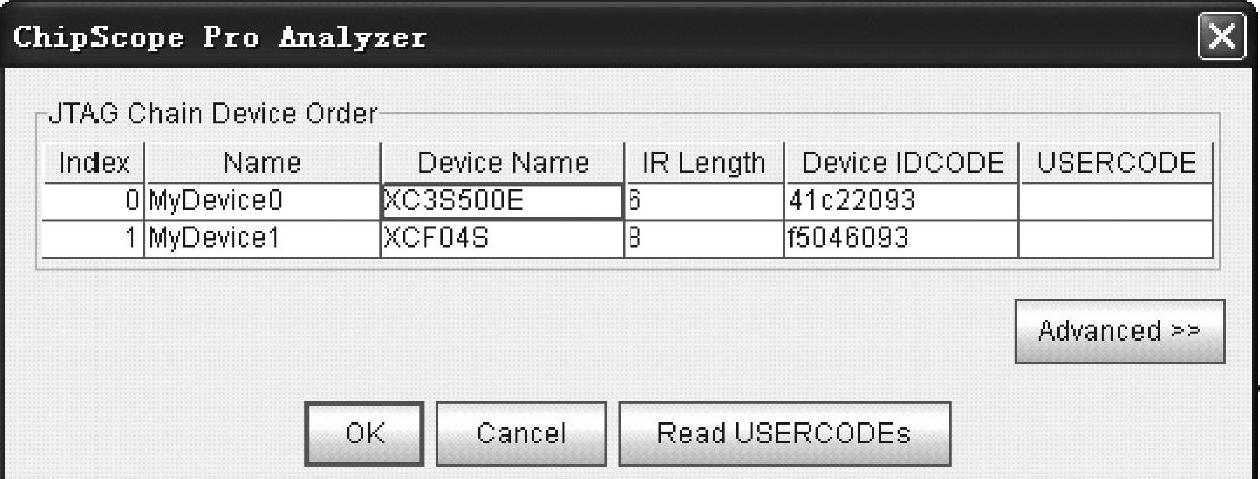

然后选择XC3S500E单击OK按钮,如图5-78所示。

图5-78 操作示意画面2

最后得到的调试结果如图5-79所示。

图5-79 调试结果

免责声明:以上内容源自网络,版权归原作者所有,如有侵犯您的原创版权请告知,我们将尽快删除相关内容。